Computer Design

Course Handout

The following materials are available for those in the cam.ac.uk domain together with videos of the lectures (see the Recordings tab for local high-quality video, or the YouTube tab if you would like videos with captions):

- Computer Design complete handout: PDF

- Slides (one per page) for Part 1: PDF

- Slides (one per page) for Part 2: PDF

Errata

- 2020-10-20: There was a VLC video playback issue for lectures 1-10. These videos have been transcoded, which reduced the size and also appears to have fixed the playback issue.

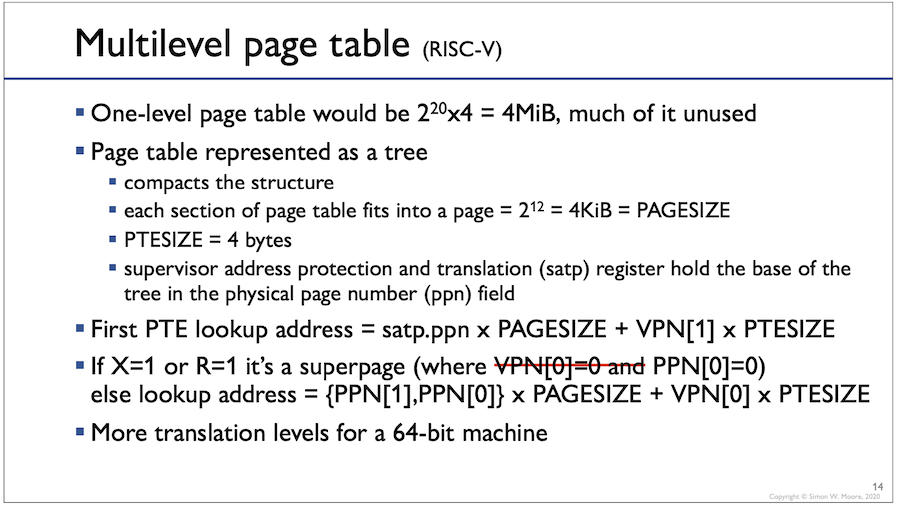

- 2021-04-08: Bug fix on Lecture 9 slide 14 below - VPN[0] does not need to

be zero for superpages and has been crossed out in the slide:

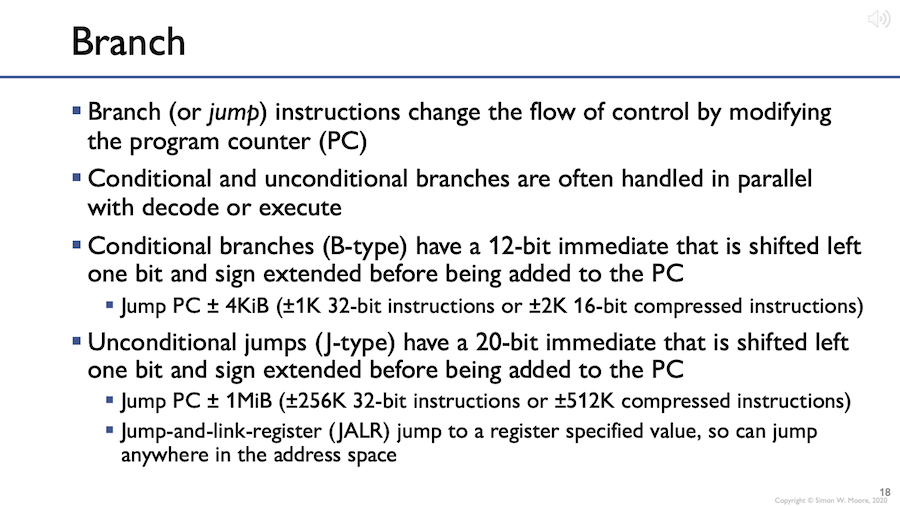

- 2021-04-13: Bug fix on Lecture 5 slide 18: the branch reach was

incorrectly labelled as ±512 instructions but should have been ±1K

instructions.

Laboratories

The ECAD+Arch laboratory sessions are loosely coupled to this lecture course. Please review the laboratory pages since there is a compulsory component.

Supervision Exercises

Recommended text

Computer Organization and Design - the hardware/software interface (RISC-V edition), Patterson and Hennessy, 2017.

Supervision 1: Lectures 1 to 4

Lecture syllabus covered:

- Lecture 1: Technology trends and design challenges. Current technology, technology trends, ECAD trends, challenges.

- Lecture 2: Digital system design. Practicalities of mapping SystemVerilog descriptions of hardware (including a processor) onto an FPGA board. Tips and pitfalls when generating larger modular designs.

- Lecture 3: Eight great ideas in computer architecture.

- Lecture 4: Reduced instruction set computers and RISC-V.

Some of this material in reinforced through the ECAD+Arch laboratory sessions. Question 1 on Paper 5 is ECAD+Arch related.

Suggested reading: Chapters 1 and 2 of the recommended text, particularly section 1.2. The exercises at the end of Chapters 1 and 2 are good sources of supervision questions.

Suggested past paper questions:

- 2017 P5 Q1 - tests reading and writing SystemVerilog and an understanding of state transitions.

- 2016 P5 Q1 - tests reading of SystemVerilog code and finding bugs.

- 2010 P5 Q2 - parts (a) and (b) ask questions about Moore's law.

- For a revision supervision: 2019 P5 Q1, 2018 P5 Q1, 2015 P5 Q1

Supervision 2: Lectures 5 to 8

Lecture syllabus covered:

- Lecture 5: Executable and synthesisable models

- Lectures 6 and 7: Pipelining

- Lecture 8: Memory hierarchy and caching

Suggested reading: Chapters 4 and 5 (sections 5.1-5.5) of the recommended text. The exercises associated with these chapters are a useful source of supervision questions.

Suggested past paper questions:

- 2017 P5 Q2 - Explores fallacies and pitfalls

- 2016 P5 Q2 - Pipelines (similarly: 2007 P6 Q2)

- 2015 P5 Q2 - Memory hierarchy (skip part (d) that is no longer covered)

- 2012 P5 Q2 - Assembler coding - redo for RISC-V rather than MIPS (they are very similar); you may wish to skip part (b)

- For a revision supervision: 2019 P5 Q2, 2018 P5 Q2, 2009 P5 Q3

Supervision 3: Lecture 9 and 10 [half supervision, other half from Dr Jones' part of of the course]

Lecture syllabus covered:

- Lecture 9: Support for operating systems. Memory protection, exceptions, interrupts, etc.

- Lecture 10: Other instruction set architectures. CISC, stack, accumulator

Suggested reading: Chapter 5 sections 5.6 onward of the recommended text.

Suggested past paper questions:

- 2008 P6 Q2 - RISC, CISC and stack machines

- 2006 P6 Q2 - register vs. stack machines; caches

Additional questions:

- How is virtual memory used to isolate applications?

- What are protection domains and how does software move between protection domains?

Second half of supervision 3 and Supervision 4

Part 2 of Computer Design: supervision exercises are available here: PDF. Supervisors can find sample answers on the supervisors tab.

Additional Material

- The RISC-V instruction set reference manual is available from the RISC-V foundation as a PDF