Introduction to Computer Architecture

Past Exam Questions

Please note that the course used to be called Computer Design, so past exam questions are under that title: Past Exam Questions in Computer Design

Course Handout

The following materials are available for those in the cam.ac.uk domain. Lectures are being presented live. For videos - see below.

Errata

Lecture 1

- Slide 12 Manufacturing Costs:

Wrong:

Correct:

- Slide 17 Voltage and frequency trade-offs:

Wrong:

Correct:

Lecture 3

- Slide 9 Instruction count and CPI (cycles per instruction):

Wrong:

Correct:

Lecture 5

- Slide 23 Compile and link for simulation:

"sudo" should be "pseudo" - Slide 11 U-type: Forming large constants:

The lecturer thought that this slide was wrong, but it is not. Specifically, in the lecture it was suggested that ORI should be used in conjunction with LUI to source a 32b immediate, which is wrong for the following reason: the 12b immediate in ORI is sign extended before being ORed with the value from LUI, so if the MSB of the 12b immediate is a 1 then all of the upper bits will be 1 obliterating the constant loaded via LUI. Instead, ADDI should be used (i.e. as per the original slide). The following sequence is correct:

LUI t0, 20-bit_constant ADDI t0, t0, 12-bit_constantIf the 12-bit_constant is negative, then this needs to be taken into account when forming the 20-bit_constant.

Lecture 7

- Slide 24 Branches cause control-flow hazards:

The comment "O3: t2=t3" should read "O3: t1=t3"

Lecture 12

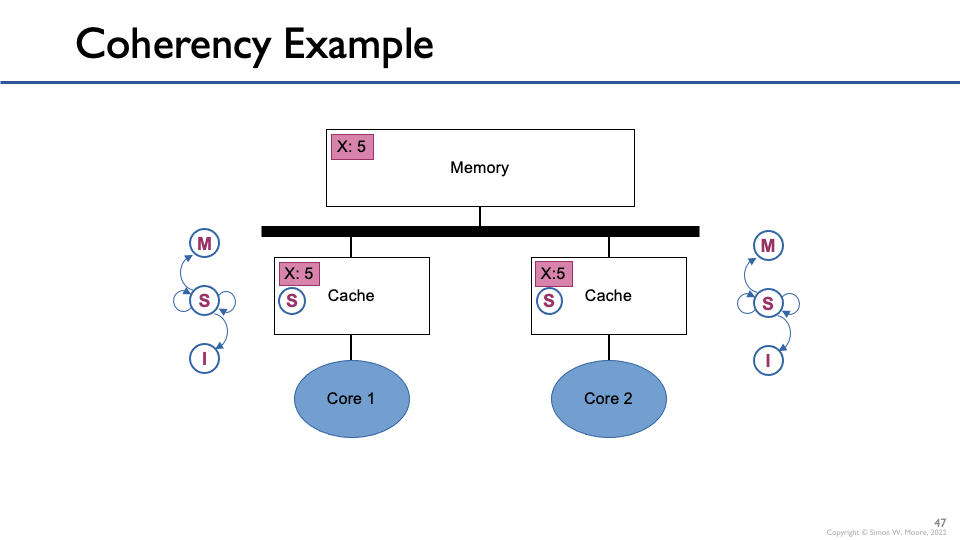

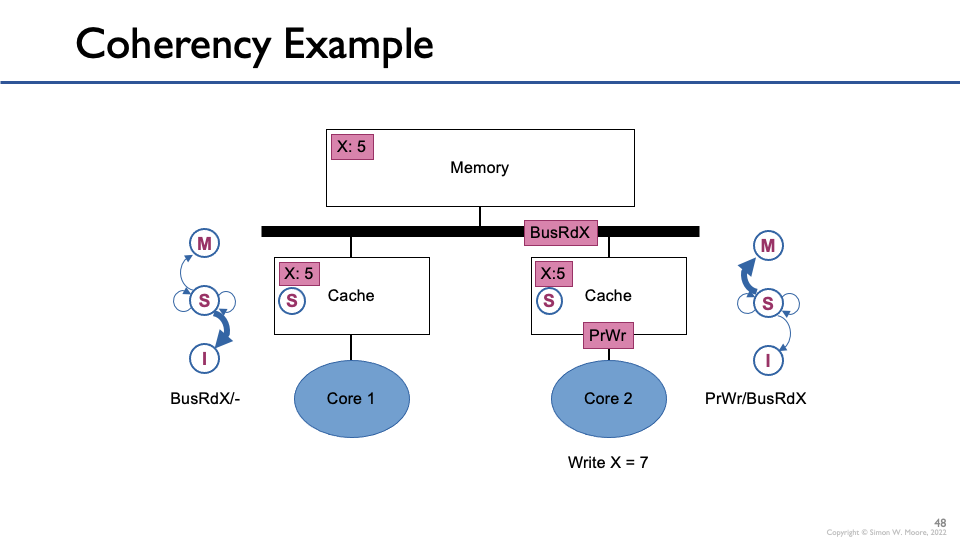

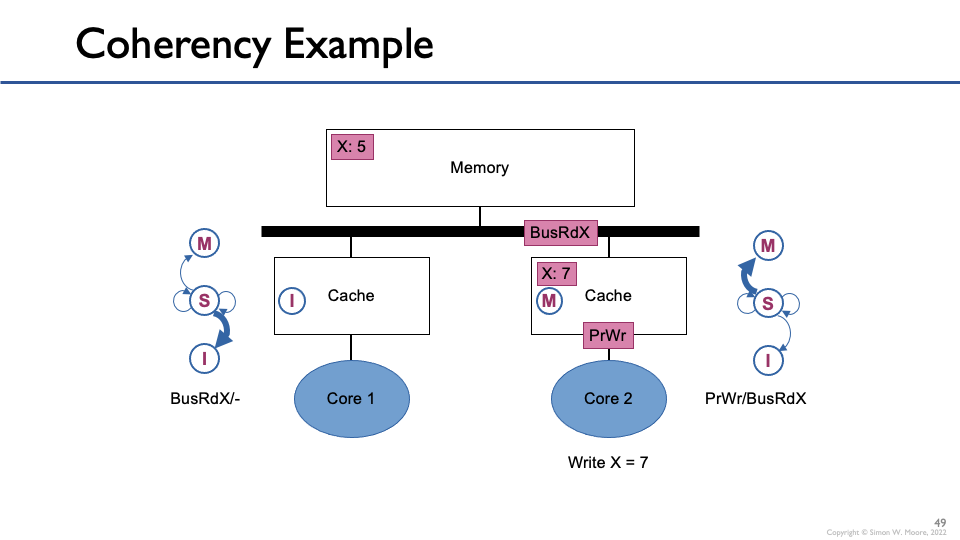

- Corrections to slides 47-49 to show that the cache for core 2

ends up with a copy of the data at address X, and that after the

BusRdX the data is flushed from core 1's cache.

Lecture 13

- Slide 22 incorrectly says: "Source register contains 1 on

success, 0 on fail"

but it should say "Source register contains 0 on success, 1 on fail" for RISC-V. - Slides 23-33 due to the above fix, all of the tests of the source register after a store conditional need to be changed from beqz to bnez.

Lecture 15

- Some versions of DAXPY assign the result to array Z where as others assign to array Y, which is one of the source arrays. Apologies for this inconsistency. The examples are still valid and the lecturer will aim to remove this inconsistency in a future version of this lecture.

- After the lecture there were quite a few questions about the details of OpenCL. The principles are far more important than the details. For example, details of the particular OpenCL function calls are not examinable and are provided as examples only.

Videos

Lectures are being presented live. Recordings are also available under the Recordings.

Lectures 1-10 videos are a re-release of the videos from 2021 with minor corrections. These are narrated by the current lecturer: Simon Moore.

Lectures 11-16 videos are the 2020 videos under the old course title but the same content as this year but with the 2020 lecturer: Tim Jones.

Laboratories

The ECAD+Arch laboratory sessions are loosely coupled to this lecture course. Please review the laboratory pages since there is a compulsory component.

Supervision Exercises

Recommended text

Computer Organization and Design - the hardware/software interface (RISC-V edition), Patterson and Hennessy, 2017.

Supervision Guide

Supervision exercises are available here: Supervision Questions (PDF). Supervisors can find sample answers on the supervisors tab.

Additional Material

- The RISC-V instruction set reference manual is available from the RISC-V foundation as a PDF