Tests and Test Results

Tests cited by name in the paper

| | | Model | CortexA9 | Tegra2 |

| 2+2W | Allow | = | — | Ok, 7.4M/3.0G |

| 2+2W+dmbs | Forbid | = | — | Ok, 0/3.0G |

| 2+2W+reads | Allow | — | — | — |

| 2+2W+dmbs+reads | Forbid | — | — | — |

| CoRR1 | Forbid | = | — | — |

|

CoRR2 | Forbid | = | — | — |

| CoRW | Forbid | = | — | Ok, 0/3.0G |

| CoWR | Forbid | = | — | Ok, 0/3.0G |

| CoWW | Forbid | = | — | Ok, 0/6.0G |

| LB+rs | Allow | = | Ok, 43k/402M | Ok, 99k/3.0G |

| MP+dmb+rs | Allow | = | Ok, 243k/402M | Ok, 9.0M/3.0G |

| MP+nondep+dmb | Allow | = | Ok, 7.2k/402M | Ok, 2.2M/3.0G |

| PPOAA | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| PPOCA | Allow | = | No, 0/402M | No, 0/3.0G |

| | | | Allow unseen | Allow unseen |

| RDW | Forbid | = | — | — |

| RDWI | Allow | = | No, 0/402M | No, 0/3.0G |

| | | | Allow unseen | Allow unseen |

| RSW | Allow | = | No, 0/402M | No, 0/3.0G |

| | | | Allow unseen | Allow unseen |

| IRIW | Allow | = | — | — |

| IRIW+addrs | Allow | = | — | — |

| IRIW+dmbs | Forbid | — | — | — |

| IRIW+dsbs | Forbid | — | — | — |

| ISA2+dmb+data+addr | Forbid | = | — | — |

| LB | Allow | = | Ok, 239k/402M | Ok, 1.4M/3.0G |

| LB+addrs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+datas | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dmbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP | Allow | = | Ok, 824k/402M | Ok, 2.1M/3.0G |

| MP+po+addr | Allow | = | Ok, 285k/402M | Ok, 624k/3.0G |

| MP+dmb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dmb+ctrl | Allow | = | Ok, 218k/402M | Ok, 5.7M/3.0G |

| MP+dsb+ctrl | Allow | = | Ok, 233k/402M | Ok, 5.4M/3.0G |

| MP+dmb+ctrlisb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsb+ctrlisb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dmbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| SB | Allow | = | Ok, 3.6M/402M | Ok, 72M/3.0G |

| SB+dmbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| SB+dsbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| WRC | Allow | = | — | — |

| WRC+data+addr | Allow | = | — | — |

| WRC+dmb+addr | Forbid | = | — | — |

| WRC+dsb+addr | Forbid | = | — | — |

| WRC+data+dmb | Allow | = | — | — |

| WRC+dmbs | Forbid | = | — | — |

| WRC+data+dsb | Allow | = | — | — |

| WRC+dsbs | Forbid | = | — | — |

Systematic tests

These tests are generated using the diycross tool, a variant

of diy. They are systematic

variations of a number of families, inserting different choices of

barriers or dependencies. The families themselves are also

systematic, as follows.

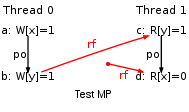

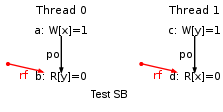

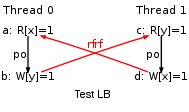

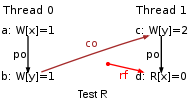

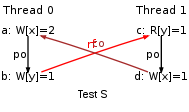

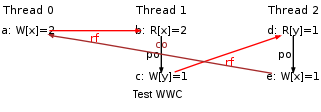

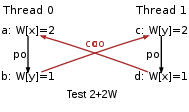

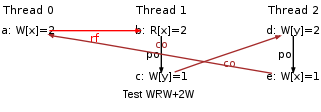

Consider tests built from a cycle of edges of the following four kinds: program order (po)

(perhaps with barriers or dependencies); reads-from (rf) edges,

from a write to a read that reads from it; from-reads (fr) edges,

from a read to coherence-successors of the write it reads from; and

coherence (co) edges, from a write to a coherence-later write to the

same address. In the diagrams below reads from the initial state

are shown as rf edges from a red dot; the fr edges are not shown

explicitly but go from such reads to the write that is to the same

address.

There are six two-thread cycles with four edges, as in the

left-hand column of the table below: test families MP, SB, LB, R, S,

and 2+2W. MP and SB are the classic ‘message-passing’ and

‘store-buffering’ tests.

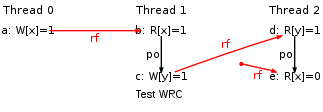

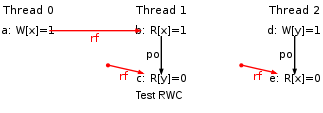

For all those test families except LB and R, there is an obvious three-thread

analogue in which the initial write is replaced by a read from a write

pulled out to another thread, as in the middle column below. The

analogues of MP and SB are the classic WRC and RWC tests (as in Boehm

and Adve, PLDI 2008). For R there are two three-thread analogues,

pulling back the writes of the two threads:

WRW+WR and WRR+2W.

MP: rf,fr

| WRC: rf,rf,fr

| |

SB: fr,fr

| RWC: rf,fr,fr

| |

LB: rf,rf

| | |

R: co,fr

| WRW+WR: rf,co,fr

| WRR+2W: rf,fr,co

|

S: rf,co

| WWC: rf,rf,co

| |

2+2W: co,co

| WRW+2W: rf,co,co

| |

The ISA2 family (based on the second example in the Power 2.06 ISA,

illustrating B-cumulativity) is a three-thread six-edge test, which one could think

of as MP with the first write pulled back along a barrier;rf path, or

as WRC with the first write pulled back along a barrier edge:

There are many other three-thread six-edge tests, some of which we

have explored but do not give here.

The IRIW family is a four-thread six-edge test:

All the tests above have at most one edge on each thread. The PPO

family (tests of preserved program order) are variations of MP with a

barrier on the writing thread and various combinations of edges on the

reading thread.

MP: Message Passing

| | | Model | CortexA9 | Tegra2 |

| MP | Allow | = | Ok, 824k/402M | Ok, 2.1M/3.0G |

| MP+isb+po | Allow | = | Ok, 541k/402M | Ok, 34M/3.0G |

| MP+dmb+po | Allow | = | Ok, 168k/402M | Ok, 3.1M/3.0G |

| MP+dsb+po | Allow | = | Ok, 171k/402M | Ok, 3.0M/3.0G |

| MP+po+addr | Allow | = | Ok, 285k/402M | Ok, 624k/3.0G |

| MP+isb+addr | Allow | = | Ok, 392k/402M | Ok, 22M/3.0G |

| MP+dmb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+po+ctrl | Allow | = | Ok, 600k/402M | Ok, 4.3M/3.0G |

| MP+isb+ctrl | Allow | = | Ok, 579k/402M | Ok, 25M/3.0G |

| MP+dmb+ctrl | Allow | = | Ok, 218k/402M | Ok, 5.7M/3.0G |

| MP+dsb+ctrl | Allow | = | Ok, 233k/402M | Ok, 5.4M/3.0G |

| MP+po+ctrlisb | Allow | = | Ok, 388k/402M | Ok, 1.0M/3.0G |

| MP+isb+ctrlisb | Allow | = | Ok, 420k/402M | Ok, 21M/3.0G |

| MP+dmb+ctrlisb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsb+ctrlisb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+po+isb | Allow | = | Ok, 622k/402M | Ok, 2.8M/3.0G |

| MP+isbs | Allow | = | Ok, 653k/402M | Ok, 33M/3.0G |

| MP+dmb+isb | Allow | = | Ok, 254k/402M | Ok, 1.0M/3.0G |

| MP+dsb+isb | Allow | = | Ok, 273k/402M | Ok, 971k/3.0G |

| MP+po+dmb | Allow | = | Ok, 317k/402M | Ok, 606k/3.0G |

| MP+isb+dmb | Allow | = | Ok, 450k/402M | Ok, 16M/3.0G |

| MP+dmbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsb+dmb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+po+dsb | Allow | = | Ok, 304k/402M | Ok, 682k/3.0G |

| MP+isb+dsb | Allow | = | Ok, 394k/402M | Ok, 13M/3.0G |

| MP+dmb+dsb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| MP+dsbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

SB: Store Buffer forwarding (sometimes called Dekker’s example)

| | | Model | CortexA9 | Tegra2 |

| SB | Allow | = | Ok, 3.6M/402M | Ok, 72M/3.0G |

| SB+isb+po | Allow | = | Ok, 3.9M/402M | Ok, 141M/3.0G |

| SB+dmb+po | Allow | = | Ok, 1.6M/402M | Ok, 11M/3.0G |

| SB+dsb+po | Allow | = | Ok, 1.4M/402M | Ok, 11M/3.0G |

| SB+isbs | Allow | = | Ok, 2.1M/402M | Ok, 199M/3.0G |

| SB+dmb+isb | Allow | = | Ok, 658k/402M | Ok, 28M/3.0G |

| SB+dsb+isb | Allow | = | Ok, 638k/402M | Ok, 28M/3.0G |

| SB+dmbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| SB+dsb+dmb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| SB+dsbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

LB: Load Buffering

| | | Model | CortexA9 | Tegra2 |

| LB | Allow | = | Ok, 239k/402M | Ok, 1.4M/3.0G |

| LB+addr+po | Allow | = | Ok, 80k/402M | Ok, 555k/3.0G |

| LB+data+po | Allow | = | Ok, 72k/402M | Ok, 522k/3.0G |

| LB+ctrl+po | Allow | = | Ok, 77k/402M | Ok, 559k/3.0G |

| LB+ctrlisb+po | Allow | = | Ok, 46k/402M | Ok, 267k/3.0G |

| LB+isb+po | Allow | = | Ok, 135k/402M | Ok, 1.1M/3.0G |

| LB+dmb+po | Allow | = | Ok, 5.4k/402M | Ok, 14k/3.0G |

| LB+dsb+po | Allow | = | Ok, 7.3k/402M | Ok, 15k/3.0G |

| LB+addrs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+data+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrl+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrlisb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+isb+addr | Allow | = | Ok, 15k/402M | Ok, 82k/3.0G |

| LB+dmb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsb+addr | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+datas | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrl+data | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrlisb+data | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+isb+data | Allow | = | Ok, 17k/402M | Ok, 163k/3.0G |

| LB+dmb+data | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsb+data | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrls | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrlisb+ctrl | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+isb+ctrl | Allow | = | Ok, 18k/402M | Ok, 129k/3.0G |

| LB+dmb+ctrl | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsb+ctrl | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+ctrlisbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+isb+ctrlisb | Allow | = | Ok, 8.7k/402M | Ok, 51k/3.0G |

| LB+dmb+ctrlisb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsb+ctrlisb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+isbs | Allow | = | Ok, 38k/402M | Ok, 494k/3.0G |

| LB+dmb+isb | Allow | = | Ok, 2.2k/402M | Ok, 9.4k/3.0G |

| LB+dsb+isb | Allow | = | Ok, 1.9k/402M | Ok, 8.7k/3.0G |

| LB+dmbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsb+dmb | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

| LB+dsbs | Forbid | = | Ok, 0/402M | Ok, 0/3.0G |

IRIW: Independent Reads of Independent Writes

WRC: Write to Read Causality

RWC: Read to Write Causality

ISA2: Second example from POWER documentation

2+2W:

| | | Model | CortexA9 | Tegra2 |

| 2+2W | Allow | = | — | Ok, 7.4M/3.0G |

| 2+2W+dmbs | Forbid | = | — | Ok, 0/3.0G |

| 2+2W+isb+po | Allow | = | — | Ok, 19M/3.0G |

| 2+2W+isbs | Allow | = | — | Ok, 38M/3.0G |

| 2+2W+dmb+po | Allow | = | — | Ok, 1.4M/3.0G |

| 2+2W+dmb+isb | Allow | = | — | Ok, 4.9M/3.0G |

| 2+2W+dsb+po | Allow | = | — | Ok, 1.7M/3.0G |

| 2+2W+dsb+isb | Allow | = | — | Ok, 5.4M/3.0G |

| 2+2W+dsb+dmb | Forbid | = | — | Ok, 0/3.0G |

| 2+2W+dsbs | Forbid | = | — | Ok, 0/3.0G |

R:

| | | Model | CortexA9 | Tegra2 |

| R | Allow | = | Ok, 1.9M/170M | Ok, 32M/3.0G |

| R+isb+po | Allow | = | Ok, 2.3M/170M | Ok, 102M/3.0G |

| R+dmb+po | Allow | = | Ok, 147k/170M | Ok, 18M/3.0G |

| R+dsb+po | Allow | = | Ok, 137k/170M | Ok, 18M/3.0G |

| R+po+isb | Allow | = | Ok, 2.6M/170M | Ok, 100M/3.0G |

| R+isbs | Allow | = | Ok, 1.8M/170M | Ok, 148M/3.0G |

| R+dmb+isb | Allow | = | Ok, 81k/170M | Ok, 46M/3.0G |

| R+dsb+isb | Allow | = | Ok, 75k/170M | Ok, 46M/3.0G |

| R+po+dmb | Allow | = | Ok, 467k/170M | Ok, 741k/3.0G |

| R+isb+dmb | Allow | = | Ok, 667k/170M | Ok, 45M/3.0G |

| R+dmbs | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| R+dsb+dmb | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| R+po+dsb | Allow | = | Ok, 579k/170M | Ok, 712k/3.0G |

| R+isb+dsb | Allow | = | Ok, 661k/170M | Ok, 42M/3.0G |

| R+dmb+dsb | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| R+dsbs | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

S:

| | | Model | CortexA9 | Tegra2 |

| S | Allow | = | Ok, 711k/170M | Ok, 4.6M/3.0G |

| S+isb+po | Allow | = | Ok, 573k/170M | Ok, 58M/3.0G |

| S+dmb+po | Allow | = | Ok, 81k/170M | Ok, 270k/3.0G |

| S+dsb+po | Allow | = | Ok, 73k/170M | Ok, 239k/3.0G |

| S+po+addr | Allow | = | Ok, 919k/170M | Ok, 1.7M/3.0G |

| S+isb+addr | Allow | = | Ok, 349k/170M | Ok, 50M/3.0G |

| S+dmb+addr | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+dsb+addr | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+po+data | Allow | = | Ok, 541k/170M | Ok, 1.8M/3.0G |

| S+isb+data | Allow | = | Ok, 457k/170M | Ok, 36M/3.0G |

| S+dmb+data | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+dsb+data | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+po+ctrl | Allow | = | Ok, 523k/170M | Ok, 1.9M/3.0G |

| S+isb+ctrl | Allow | = | Ok, 474k/170M | Ok, 47M/3.0G |

| S+dmb+ctrl | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+dsb+ctrl | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+po+ctrlisb | Allow | = | Ok, 148k/170M | Ok, 1.3M/3.0G |

| S+isb+ctrlisb | Allow | = | Ok, 236k/170M | Ok, 29M/3.0G |

| S+dmb+ctrlisb | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+dsb+ctrlisb | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+po+isb | Allow | = | Ok, 684k/170M | Ok, 2.7M/3.0G |

| S+isbs | Allow | = | Ok, 555k/170M | Ok, 60M/3.0G |

| S+dmb+isb | Allow | = | Ok, 13k/170M | Ok, 253k/3.0G |

| S+dsb+isb | Allow | = | Ok, 11k/170M | Ok, 227k/3.0G |

| S+po+dmb | Allow | = | Ok, 70k/170M | Ok, 316k/3.0G |

| S+isb+dmb | Allow | = | Ok, 133k/170M | Ok, 12M/3.0G |

| S+dmbs | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+dsb+dmb | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+po+dsb | Allow | = | Ok, 66k/170M | Ok, 480k/3.0G |

| S+isb+dsb | Allow | = | Ok, 132k/170M | Ok, 11M/3.0G |

| S+dmb+dsb | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

| S+dsbs | Forbid | = | Ok, 0/170M | Ok, 0/3.0G |

WWC:

WRW+2W:

PPO:

Extra tests