BERI

BERI open-source hardware downloads

| Newflash - May 18 2015: we have made a new release of the BERI/CHERI source code, which has been updated for our most recent architectural changes and includes everything necessary to synthesise BERI on an Altera FPGA. |

| Newflash - June 18 2014: the BERI/CHERI source code is now available for download! Physical build specs for the Terasic DE4-based tablet are online, as is FreeBSD OS support for BERI, which was merged to FreeBSD 10.0 in August 2012. |

SRI International and the University of Cambridge have developed BERI, a pipelined 64-bit RISC FPGA soft-core processor designed for teaching and research in the hardware-software interface. BERI is implemented in Bluespec, a high-level hardware definition language (HDL) that compiles to efficient C simulation or Verilog descriptions suitable for FPGA implementation. BERI is able to boot the open-source FreeBSD UNIX operating system, which supports multitasking, TCP/IP networking, multiple filesystems, POSIX APIs, advanced security features, a has drivers for a variety of devices found on Terasic's FPGA boards, as well as many thousands of third-party open-source applications. We use the BERI hardware-software platform daily in our teaching and research (e.g., CHERI), and hope that others will find it useful as well!

Hardware Downloads

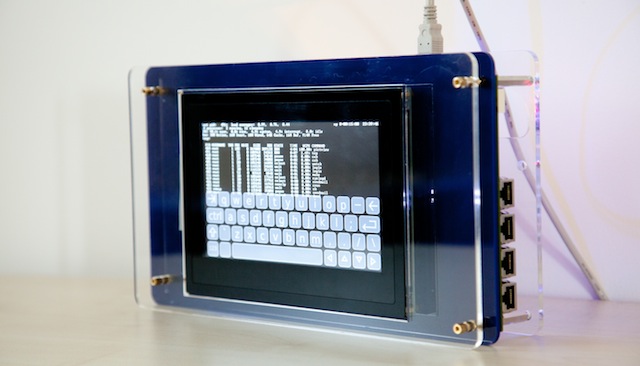

BERI consists of a number of components including: physical designs (e.g., tablet packaging for the Terasic DE4); HDL descriptions of the processor and several peripherals; and adaptations of FreeBSD and other open-source software to support BERI.

For software downloads such as BERI OS support, see this page.

Please consider subscribing to our mailing lists if you have any questions or need a hand getting started with BERI.

- BERI hardware description

-

We have open sourced the Bluespec hardware description of the BERI1 and BERI2 processors, integrated peripherals such as the BERI programmable interrupt control, C-language simulations exposing UNIX devices within the simulation (e.g., disk images as SD cards), and the control/debugging tool berictl. We include our FPGA projects for synthesis on the DE4, so this release is usable for both Bluespec software simulation and synthesis on FPGA.

- BERI processor source: https://github.com/CTSRD-CHERI/beri

- BERI physical designs - June 2013

-

We have open sourced the hardware specs and build instructions for our Terasic DE4-based tablet design.

License and Disclaimer

BERI is distributed under the BERI Hardware-Software License, a lightly modified version of the Apache Software License enhanced to better support open-source hardware. BERI Open Systems CIC is a UK-based not-for-profit responsible for receiving contributors' agreements for BERI.

The BERI hardware-software platform is highly experimental; users are cautioned that damage to physical FPGA hardware can result from bugs or user error. The BERI hardware-software open-source license places further limitations on warranty and liability.

Acknowledgment

This hardware, software, and documentation was developed by SRI International and the University of Cambridge Computer Laboratory under DARPA/AFRL contract (FA8750-10-C-0237) ("CTSRD"), as part of the DARPA CRASH research programme. Additional support was received from Google.

We acknowledge our many supporters, including Terasic, and our early adopter community who have provided helpful feedback and advice!