BERI

BERI frequently asked questions (FAQ)

Here are answers to some of the common questions we've received (or in some cases, anticipate) about BERI. See the CHERI FAQ for questions about the CHERI ISA and prototype.

BERI processor and software stack

- What is BERI?

-

BERI is the Bluespec Extensible RISC Implementation, a 64-bit pipelined RISC processor developed by SRI International and the University of Cambridge Computer Laboratory as part of our joint CTSRD Project on revising the hardware-software interface for security. BERI implements a 1994-vintage variant on the 64-bit MIPS ISA including floating-point unit (FPU), a programmable interrupt controller (PIC), and in-progress support for multithreading and multicore operation.

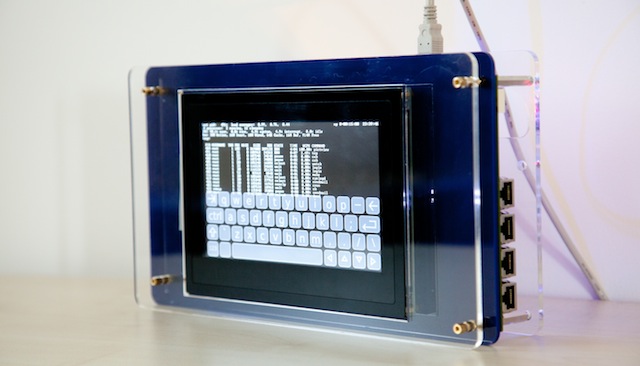

BERI is written in Bluespec System Verilog, a Haskell-drived high-level hardware description language (HDL) that makes it easy to perform design-space exploration. In typical use, we synthesise BERI to Altera or Xilinx FGPAs, but also perform some development and testing work in simulation. On the Altera-based Terasic DE4 board, we clock BERI at 100MHz, and for cache-resident workloads, experience a CPI close to 1.0.

Our hardware-software research is facilitated by a large-scale software corpus (more below), and in normal operation we SSH into a UNIX shell on BERI and use it as a general-purpose computer to the greatest extent possible. BERI's open-source software stack includes the FreeBSD operating system and tens of thousands of third-party applications.

Development of BERI and CHERI was supported by grants from DARPA and Google.

- What do you use BERI for at SRI/Cambridge?

-

We designed BERI to support research into the hardware-software interface, with our first major research project being Capability Hardware Enhanced RISC Instructions (CHERI); it has also seen use in research into formal verification, processor multithreading, and other instruction-set-level experimnetation at both the masters and PhD level. We also use BERI in our masters' course in computer architecture, and hope to deploy BERI in further hardware-software teaching in the future.

- What software does BERI support?

-

A realistic software corpus is critical to performing and evaluating architectural research, so we have invested considerable effort in adding processor features required to support off-the-shelf software (e.g., mature MMU and exception handling), and in bringing up a large-scale open-source software stack on BERI. This includes the FreeBSD UNIX operating system, Clang/LLVM compiler suite, and tens of thousands of third-party open-source applications. We will usually cross-compile from higher-performance x86 systems, but it is also possible to compile software on BERI itself.

- What is BERI2

-

BERI1 is the first version of the BERI processor, focused on experimental implementation of the CHERI ISA and providing a hardware-software research platform suitable for daily use in teaching and research. BERI2 is a reimplementation of the core BERI1 pipeline using a stylised form of Bluespec more suitable for formal verification; it also implements a basic form of hardware multithreading. BERI1 and BERI2 share many core functions including memory subsystem, buses, and peripheral devices, and both support the FreeBSD UNIX operating system. For experimentation with processor design in a teaching or research setting, we would likely recommend BERI1 as a first choice; for research into formal verification of hardware designs, BERI2 might be preferred.

- Does BERI support multicore?

-

Yes; however, it is an early prototype and not yet able to support a full software stack (e.g., OS). You can find the current prototype code in the BERI distribution available for download, and we have developed initial software-side support to be used once the hardware is more mature. We are pursuing this actively and hope to announce more here soon!

- What debugging tools and testing tools exist for BERI?

-

We develop BERI in both simulation and synthesis to FPGA. There is extensive debug-tracing output available in the latter, configurable from the simulator command line; this includes ISA-level tracing (providing a clean trace entry for each instruction committed), and lower-level tracing that tracks cache operation, etc. In synthesis, BERI has a debug unit that can be attached to over JTAG, allowing control of the processor pipeline, tracing of instructions, etc. These tools are useful for both hardware and software debugging. We have developed an extensive ISA-level test suite, use fuzzing tools to help detect pipeline and exception-handling bugs, and also test a large software corpus (including a general-purpose operating system) against BERI. We use Jenkins to run the test suite to several different BERI and CHERI configurations on each commit to our source repository, adopting a continuous integration model to quickly detect regressions.

- Why the Bluespec HDL?

-

A key aspect of our CHERI Project was exploring how ISA-level changes in memory protection and security model can support stronger compiler-, OS-, and application-facing software security models. This required rapid prototyping (although BERI did take almost four years to implement!) and the ability to rapidly change aspects of the design, a task made markedly easier by using Bluespec. Use of a high-level language is a key differentiator between BERI and many previous open-source processor designs, and makes it particular suitable for research and teaching. Bluespec depends on a proprietary toolchain, as do many hardware design tools, but can be compiled to C or Verilog, which may be redistributed and used without the tools. Bluespec provides generous academic licensing that has met our needs well.

- What FPGA boards do you use?

-

Our most heavily used platform is Terasic's DE4 board, which includes a fairly high-end Altera FPGA able to implement BERI at 100MHz. We have also used Altera's tPad board, and have an experimental adaptation to the Xilinx-based NetFPGA 10G board. While BERI is not specific to any particular FPGA, it relies on an AXI bus attachment, the floating-point unit has been tested only with Altera's floating-point library, and the software stack will of course also require device drivers for peripherals found on the AXI bus. FreeBSD supports a number of Altera and Xilinx peripherals, as well as other commonly available embedded parts. We are happy to offer advice on how to adapt FreeBSD to support further devices you may encounter.

- What is FreeBSD?

- FreeBSD is an open-source UNIX operating system derived from the Berkely Software Distribution (BSD). FreeBSD is widely used in service-provider environments, as a foundation for appliance and embedded devices and operating systems (e.g., Netflix's video streaming service, the F root name server, NetApp Filers, EMC/Isilon storage devices, Juniper routers, Apple's Mac OS X and iOS operating systems, and Sony's Playstation 3 and 4). FreeBSD provides a full UNIX environment with support for multithreading and multiprocessing, the UNIX process model, TCP/IP networking, multiple filesystems, support for many embedded targets, advanced security features such as capability-system support, integrated tracing using DTrace, and is built using the Clang/LLVM compiler suite. FreeBSD supports mature cross compilation, so we will typically develop software on a 64-bit FreeBSD x86 system, copying compiled binaries over to BERI systems to execute.

- Why FreeBSD?

-

We have used FreeBSD in significant amounts of past research, but found three features in particular compelling to use the OS for our BERI and CHERI projects: integrated support for capability-system-based security (Capsicum), the DTrace tracing system, and agressive early adoption of the Clang/LLVM compiler suite on which we depend heavily for ISA and software transformation/analysis research. FreeBSD's commercialisation-friendly license was also relevant.

- How did you port FreeBSD to BERI?

-

BERI implements an ISA roughly similar to that found in the 1993 MIPS 4000 processor, although with substantial changes including those required to provide efficient implementation on FPGA. We therefore started with the existing FreeBSD/MIPS port, creating a new BERI platform support package, and developing drivers for BERI-specific peripherals such as the BERI programmable interrupt controller (PIC). We wrote new device drivers for a variety of hard and soft cores available on Altera and Xilinx boards of interest, including for the Altera JTAG UART, Altera Triple-Speed Ethernet MAC, Altera University Program SD Card Core, and Philips ISP1761 USB controller. We similarly improved drivers such as that for the Intel Strata Flash found on Terasic's DE4 FPGA board. We also ported FreeBSD's boot2 and loader boot environments to the MIPS ISA, work that should benefit other non-BERI systems. We have an in-progress adaptation of FreeBSD/BERI supporting BERI's early multicore support.

- How can I contribute to BERI?

-

We require all contributors to BERI to sign an individual or institutional contributors agreement (or, in some cases, both, if you contribute in both individual and employed capacities); you can find these on the BERI Open Systems CIC website. Our Subversion revision-control repository is not currently public, but we hope that this will change in the future (probably, this would coincide with a migration to Git and some rearrangement of the repository, hence our being uncertain on the timescale). However, you can submit patches to us directly by e-mail, or via the cl-beri-discuss mailing list. We will produce new releases intermittently that incorporate suitable changes. We cannot guarantee to include all modifications that we receive, for all of the obvious reasons!