BERI

Bluespec Extensible RISC Implementation (BERI)

| February 2016: We have posted QEMU-CHERI, an ISA-level simulation of CHERI MIPS, to complement our HDL prototypes. QEMU-CHERI runs CheriBSD, providing an accessible CHERI experimentation environment. |

| November 2015: Two new technical reports on CHERI are now available: CHERI ISAv4, and the CHERI Programmer's Guide. |

| May 2015: we have made a new release of the BERI/CHERI source code, which has been updated for our most recent architectural changes and includes everything necessary to synthesise BERI on an Altera FPGA. |

BERI is an open-source platform to support research into the hardware-software interface. BERI allows investigation of research questions spanning historically siloed domains in systems research: computer architecture, compilers and programming languages, operating systems, and applications. We have released BERI under the BERI Hardware-Software License, a lightly modified version of the Apache Software License suitable for open-source hardware. Combined with a complete BSD- or Apache-licensed open-source software stack, including an adapation of the widely used FreeBSD operating system, Clang and LLVM compiler suite, and countless open-source applications, we are able to perform multi-dimensional systems reseach, exploring complex tradeoffs in via reproducible scientific methodology.

BERI is an FPGA soft-core processor implementing a 64-bit RISC instruction set, and is implemented in the Bluespec Hardware Description Language (HDL) – a high-level functional programming language for describing hardware designs. Bluespec allows for highly parameterisable designs, as well as easier design-space exploration, making it well-suited for teaching and research. BERI is able to boot the open-source FreeBSD UNIX operating system, which supports multitasking, TCP/IP networking, multiple filesystems, POSIX APIs, advanced security features, a has drivers for a variety of devices found on Terasic's FPGA boards, as well as many thousands of third-party open-source applications. We use the BERI hardware-software platform daily in our teaching and research and hope that others will find it useful as well!

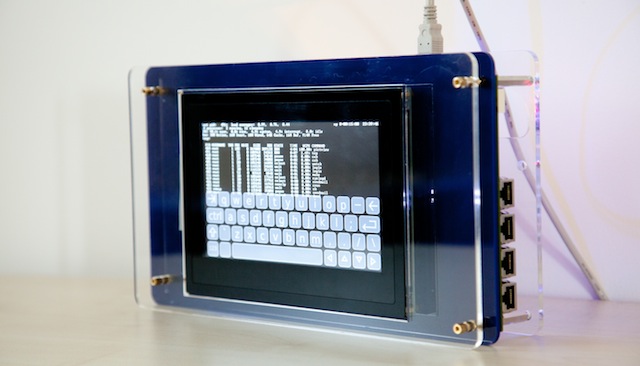

We have successfully synthesised BERI for both Altera and Xilinx FPGAs. We have developed device drivers for several hard- and soft-core peripherals found on Altera-based board designs, including the Terasic DE4 board. We use FPGA-based BERI systems daily in user-friendly tablet, as well as in a network-accessible rackmount "server" format permitting remote software development and experimentation.

Our first BERI-based research project is CHERI: a research platform deconflating virtualisation and protection; however, the platform is intended to allow exploration of a broad range of other research problems, including in CPU multi-threading, CPU/memory interconnects, tagged memory, compiler-CPU design tradeoffs, CPU extensions for high-performance networking, graphics processing, and many other areas.

Research conference and journal papers

- Robert N. M. Watson, Jonathan Woodruff, Peter G. Neumann, Simon W. Moore, Jonathan Anderson, David Chisnall, Nirav Dave, Brooks Davis, Khilan Gudka, Ben Laurie, Steven J. Murdoch, Robert Norton, Michael Roe, Stacey Son, and Munraj Vadera. CHERI: A Hybrid Capability-System Architecture for Scalable Software Compartmentalization, Proceedings of the 36th IEEE Symposium on Security and Privacy ("Oakland"), San Jose, California, USA, May 2015.

- David Chisnall, Colin Rothwell, Robert N.M. Watson, Jonathan Woodruff, Munraj Vadera, Simon W. Moore, Michael Roe, Brooks Davis, and Peter G. Neumann. Beyond the PDP-11: Architectural support for a memory-safe C abstract machine, Proceedings of the Twentieth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2015), Istanbul, Turkey, March 2015. (Audience choice: Best presentation award.)

- Jonathan Woodruff, Robert N. M. Watson, David Chisnall, Simon W. Moore, Jonathan Anderson, Brooks Davis, Ben Laurie, Peter G. Neumann, Robert Norton, and Michael Roe. The CHERI capability model: Revisiting RISC in an age of risk, Proceedings of the 41st International Symposium on Computer Architecture (ISCA 2014), June 14–16, 2014, Minneapolis, MN, USA.

Research workshop papers

- Jonathan Woodruff, Simon W. Moore and Robert N.M. Watson, Memory Segmentation to Support Secure Applications, CEUR Workshop: Doctoral Symposium on Engineering Secure Software and Systems (ESSoS), Paris, France, 26–27 February, 2013.

- Robert N. M. Watson, Peter G. Neumann, Jonathan Woodruff, Jonathan Anderson, Ross Anderson, Nirav Dave, Ben Laurie, Simon W. Moore, Steven J. Murdoch, Philip Paeps, Michael Roe, and Hassen Saidi, CHERI: A Research Platform Deconflating Hardware Virtualization and Protection, RESoLVE workshop associated with ASPLOS in London, March 5–7, 2012.

- Peter G. Neumann and Robert N. M. Watson, Capabilities Revisited: A Holistic Approach to Bottom-to-Top Assurance of Trustworthy Systems, Fourth Layered Assurance Workshop (in association with ACSAC 2010), Austin, Texas, USA, December 6–7, 2010.

Open-source and industrial papers

- Brooks Davis, Robert Norton, Jonathan Woodruff, and Robert N. M. Watson. How FreeBSD Boots: a soft-core MIPS perspective, Proceedings of AsiaBSDCon 2014, 13–16 March, 2014, Tokyo, Japan.

- A Theodore Markettos, Jonathan Woodruff, Robert N. M. Watson, Bjoern A. Zeeb, Brooks Davis, Simon W Moore, The BERIpad tablet: open-source construction, CPU, OS and applications, Proceedings of 2013 FPGA Workshop and Design Contest, November 1st–3rd, Southeast University, Nanjing, China.

Technical Reports - ISA specification and hardware/software references

- Robert N. M. Watson, David Chisnall, Brooks Davis, Wojciech Koszek, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, and Jonathan Woodruff. Capability Hardware Enhanced RISC Instructions: CHERI Programmer’s Guide, Technical Report UCAM-CL-TR-877, University of Cambridge, Computer Laboratory, September 2015. Current CHERI programmer's guide

- Robert N. M. Watson, Peter G. Neumann, Jonathan Woodruff, Michael Roe, Jonathan Anderson, David Chisnall, Brooks Davis, Alexandre Joannou, Ben Laurie, Simon W. Moore, Steven J. Murdoch, Robert Norton, and Stacey Son. Capability Hardware Enhanced RISC Instructions: CHERI Instruction-Set Architecture, Technical Report UCAM-CL-TR-876, University of Cambridge, Computer Laboratory, September 2015. Current CHERI ISA specification

- Robert N. M. Watson, David Chisnall, Brooks Davis, Wojciech Koszek, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, Jonathan Woodruff. Bluespec Extensible RISC Implementation: BERI Software Reference, Technical Report UCAM-CL-TR-869, University of Cambridge, Computer Laboratory, April 2015.

- Robert N.M. Watson, Jonathan Woodruff, David Chisnall, Brooks Davis, Wojciech Koszek, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, Robert Norton, and Michael Roe. Bluespec Extensible RISC Implementation: BERI Hardware Reference, Technical Report UCAM-CL-TR-868, University of Cambridge, Computer Laboratory, April 2015.

- Robert N.M. Watson, Peter G. Neumann, Jonathan Woodruff, Jonathan Anderson, David Chisnall, Brooks Davis, Ben Laurie, Simon W. Moore, Steven J. Murdoch, and Michael Roe. Capability Hardware Enhanced RISC Instructions: CHERI Instruction-Set Architecture, Technical Report UCAM-CL-TR-864, University of Cambridge, Computer Laboratory, December 2014. Note: superseded by UCAM-CL-TR-876

- Robert N.M. Watson, David Chisnall, Brooks Davis, Wojciech Koszek, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, and Jonathan Woodruff. Bluespec Extensible RISC Implementation: BERI Software Reference, Technical Report UCAM-CL-TR-853, University of Cambridge, Computer Laboratory, April 2014. Note: superseded by UCAM-CL-TR-869.

- Robert N.M. Watson, Jonathan Woodruff, David Chisnall, Brooks Davis, Wojciech Koszek, A. Theodore Markettos, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, Robert Norton, and Michael Roe. Bluespec Extensible RISC Implementation: BERI Hardware Reference, Technical Report UCAM-CL-TR-852, University of Cambridge, Computer Laboratory, April 2014. Note: superseded by UCAM-CL-TR-868.

- Robert N.M. Watson, David Chisnall, Brooks Davis, Wojciech Koszek, Simon W. Moore, Steven J. Murdoch, Peter G. Neumann, and Jonathan Woodruff. Capability Hardware Enhanced RISC Instructions: CHERI User’s Guide, Technical Report UCAM-CL-TR-851, University of Cambridge, Computer Laboratory, April 2014. Note: superseded by UCAM-CL-TR-877

- Robert N.M. Watson, Peter G. Neumann, Jonathan Woodruff, Jonathan Anderson, David Chisnall, Brooks Davis, Ben Laurie, Simon W. Moore, Steven J. Murdoch, and Michael Roe. Capability Hardware Enhanced RISC Instructions: CHERI Instruction-Set Architecture, Technical Report UCAM-CL-TR-850, University of Cambridge, Computer Laboratory, April 2014. Note: superseded by UCAM-CL-TR-864.