Course pages 2019–20

Computer Design

Course Handout

For part 1 of the course (lectures 1-10), people in Cambridge may download the lecture notes as a PDF or 1-up tablet version as a PDF. Please observe the copyright notice.

Material for part 2 (lectures 11-16) is available here: handout PDF and slides 1-up for viewing.

Errata

- Lecture 2, slide 3: "lock clock skew" should be "low clock skew".

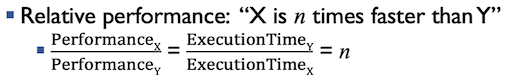

- Lecture 3, slide 6: the definition of relative performance was

incorrect. The corrected version is:

- Lecture 9: questions after the lecture indicated that virtual to physical translation of pages and super-pages needed to be clarified. To this end, two additional slides have been prepared: PDF

- Lecture 13: the descriptions of fetch-and-add and atomic exchange as being synchronisation primitives was misleading. It is clearer to refer to them as atomic operations. Various slides towards the end of this lecture have been altered to better reflect this. All slides for this lecture are available as 1-up PDF or 8-up PDF.

Supervision Exercises

Recommended text

Computer Organization and Design - the hardware/software interface (RISC-V edition), Patterson and Hennessy, 2017.

Supervision 1: Lectures 1 to 4

Lecture syllabus covered:

- Lecture 1: Technology trends and design challenges. Current technology, technology trends, ECAD trends, challenges.

- Lecture 2: Digital system design. Practicalities of mapping SystemVerilog descriptions of hardware (including a processor) onto an FPGA board. Tips and pitfalls when generating larger modular designs.

- Lecture 3: Eight great ideas in computer architecture.

- Lecture 4: Reduced instruction set computers and RISC-V.

Some of this material in reinforced through the ECAD+Arch laboratory sessions. Question 1 on Paper 5 is ECAD+Arch related.

Suggested reading: Chapters 1 and 2 of the recommended text, particularly section 1.2. The exercises at the end of Chapters 1 and 2 are good sources of supervision questions.

Suggested past paper questions:

- 2017 P5 Q1 - tests reading and writing SystemVerilog and an understanding of state transitions.

- 2016 P5 Q1 - tests reading of SystemVerilog code and finding bugs.

- 2010 P5 Q2 - parts (a) and (b) ask questions about Moore's law.

- For a revision supervision: 2019 P5 Q1, 2018 P5 Q1, 2015 P5 Q1

Supervision 2: Lectures 5 to 8

Lecture syllabus covered:

- Lecture 5: Executable and synthesisable models

- Lectures 6 and 7: Pipelining

- Lecture 8: Memory hierarchy and caching

Suggested reading: Chapters 4 and 5 (sections 5.1-5.5) of the recommended text. The exercises associated with these chapters are a useful source of supervision questions.

Suggested past paper questions:

- 2017 P5 Q2 - Explores fallacies and pitfalls

- 2016 P5 Q2 - Pipelines (similarly: 2007 P6 Q2)

- 2015 P5 Q2 - Memory hierarchy (skip part (d) that is no longer covered)

- 2012 P5 Q2 - Assembler coding - redo for RISC-V rather than MIPS (they are very similar); you may wish to skip part (b)

- For a revision supervision: 2019 P5 Q2, 2018 P5 Q2, 2009 P5 Q3

Supervision 3: Lecture 9 and 10 [half supervision, other half from Dr Jones' part of of the course]

Lecture syllabus covered:

- Lecture 9: Support for operating systems. Memory protection, exceptions, interrupts, etc.

- Lecture 10: Other instruction set architectures. CISC, stack, accumulator

Suggested reading: Chapter 5 sections 5.6 onward of the recommended text.

Suggested past paper questions:

- 2008 P6 Q2 - RISC, CISC and stack machines

- 2006 P6 Q2 - register vs. stack machines; caches

Additional questions:

- How is virtual memory used to isolate applications?

- What are protection domains and how does software move between protection domains?

Second half of supervision 3 and Supervision 4

Part 2 of Computer Design: supervision exercises are available here: PDF. Supervisors can find sample answers on the supervisors tab.

Laboratories

The ECAD+Arch laboratory sessions are loosely coupled to this lecture course. Sign-up for these lab sessions at the first Computer Design lecture.

Additional Material

- The RISC-V instruction set reference manual is available from the RISC-V foundation as a PDF