ECAD and Architecture Practical Classes

Lablet 2.2 - System on Chip Design

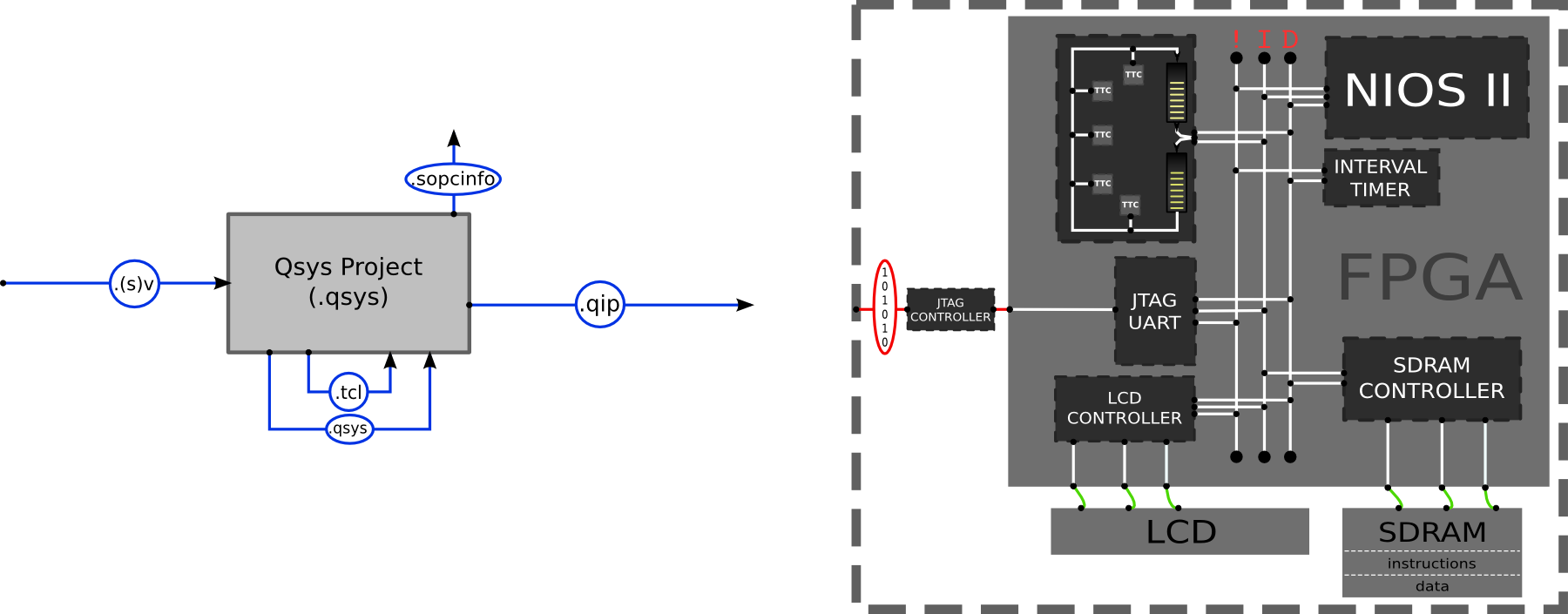

The SoC that you will design is an extension of that from Lablet 2.1, replacing the PIOs with a controller for the LCD screen and adding a custom component that implements a number of TTC processors and logic that allows them to be used by the NIOS processor.

Getting Started

First you need to create a new Quartus project using the same procedure as for lablet 1.1; call your directory e.g. ecad_lablet_2_2. Don't forget to copy and include the design constraints file to specify clocks (toplevel.sdc) and to import the pin definition file (tPad_pin_assignments.qsf). You should also copy your button synchroniser module and the PLL that you used in Lablet 1.2.

Copy the MIF file and TTC core (ttc.sv) from Lablet 2.1 into your project directory. Also copy the following files:

- lcd_controller.qsys

- A controller for the tPad LCD.

- ring_ttc.sv

- A SystemVerilog component that instantiates a specified number of TTC processors in a switched ring. Each of the processors runs the same specified MIF program binary. The component enables parameters to be addressed to a particular TTC in the ring and for their responses to be returned to the NIOS.

- ring_ttc_hw.tcl

- Describes the component in ring_ttc.sv in a format that allows it to be used as a component in Qsys.

- ring_ttc_proc.qsys

- Qsys subsystem that wraps the multi-core TTC system. A FIFO is used to store input parameters; these are sent around the ring and put in the input stream of a specified TTC. Results output from the TTC cores are sent to a separate FIFO to await retrieval by the NIOS.

Note that these files (lcd_controller.qsys, ttc.sv, ring_ttc.sv, ring_ttc_hw.tcl, lcd_controller.qsys) will all be imported into your mandelbrot Qsys project (on the next page) and should therefore NOT be added to your Quartus project to avoid duplicates. Duplicate logic may result in errors and longer compile times.

The only files that should be added to your Quartus project are:

- toplevel.sv

- synchronisation.sv (or whatever you called your two flop synchroniser)

- toplevel.sdc

- pll.qip

- mandelbrot/synthesis/mandelbrot.qip - which will be created by Qsys once you've completed the instructions on the next page

Start Qsys by selecting Tools | Qsys.