Lab 2 - Architecture, Simulation and Multi-Core SoC Design

This lab has two parts. As a guideline, each part should take between one and two weeks.

Lablet 2.1 - Processor Architecture

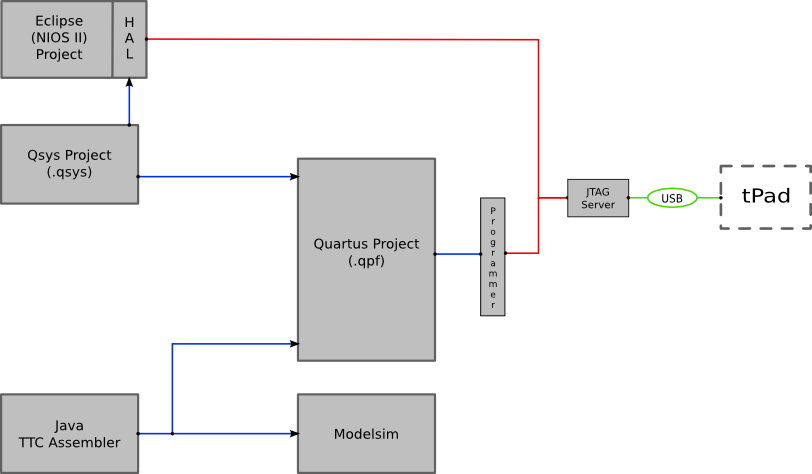

You will use Modelsim to simulate the TTC processor discussed in lectures. After modifying the TTC to add a fixed-point multiply instruction you will then write some assembly code to calculate if a given point is a member of the Mandelbrot set and test this is simulation. Simulation allows us to test the functional correctness of a design before embarking on time-consuming synthesis runs.

Lablet 2.2 - Multi-Core SoC Design

You will produce a Mandelbrot set viewer on the tPad. This will involve creating a multi-core SoC, which will use many copies of the TTC processor, each running the assembley code written in Lablet 2.1, to accelerate rendering.

- Lab 2 Contents

- Lablet 2.1 - Simulation

- Lablet 2.2 - Architecture

- Assessment