ECAD and Architecture Practical Classes

Lablet 2.1 - Simulation

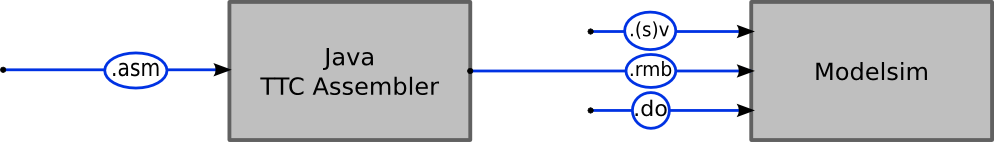

This part of the lab involves simulating the TTC processor described in lectures using Modelsim. In addition to the HDL description of the processor, a test harness is available to run programs under simulation; you will write some TTC assembly code, convert it to a compatible binary (machine code) format using an assembler, and test the program binary using the test harness.

Programming the TTC

Before continuing, it is strongly advised you familiarise yourself with the TTC Assembler Guide.

Create a new directory for this lablet, called ecad_lablet_2_1. Download the following files into the new directory:

- ttcasm.jar

- Assembler for the TTC processor, written in Java.

- ttc.sv

- SystemVerilog implementation of Thacker's Tiny Computer (TinyComp), a debug module for use in simulation, and various operational constructs.

- ttc_test.sv

- SystemVerilog test harness (TestTinyComp) for running programs under simulation.

- ttcsim.do

- Modelsim script to invoke a simulation run.

- add.asm

- Example TTC assembly program to add two unsigned numbers.

Open a terminal and cd to the directory you created above.

To assemble a program, type java -jar ttcasm.jar <option> <yourfile.asm>, where yourfile.asm contains TTC assembly code. The output of the assembler depends on the option chosen:

- mif

- A Memory Initialisation File format used by Quartus when running the program as part of synthesised hardware.

- rmb

- A file, in a similar format, used by Modelsim when running the program in simulation.

- display

- Displays the program instructions in a verbose form corresponding to the field layout used by the TTC. Labels are resolved to instruction addresses.

- help

- Displays a summary of assembler usage.

Assemble the program in add.asm using the rmb format. This will produce and output file called add.rmb.