| Computer Laboratory ECAD and Architecture Practical Classes |

Computer Laboratory > Teaching > Course material 2008–09 > ECAD Labs > Tutorials > Incremental Compilation

This tutorial takes you through the steps needed to set up the second lab exercise for an incremental compile. It is not meant to be a complete overview of the subject, merely an introduction to the basics of incremental compilation. For a more thorough coverage of this topic, see Altera's documentation. Although this tutorial uses lab 2 as a specific example, the techniques used here can be applied to any project. PartitioningThe first step in getting a design ready for an incremental compile is to split up the design into several logical partitions. Once incremental compilation is set up, Quartus will only compile those partitions where the source code of any module within them has changed since the previous compile. It is thus best to set up partitions that split the design into separate parts that do not interact in a very complicated way, to help prevent cases where several modules covering lots of partitions have to be changed, thus negating the effect of incremental compilation. For lab 2, we will create 2 partitions. One holds the entire project, the other just the processor. You can think of the partitions as being nested inside one another, since the processor is contained entirely within the top level, yet we are assigning a separate partition to it.Before you can continue, you must first run analysis & synthesis if this has not already been done. This enables Quartus

to produce a model of your system, enabling you to then select your partitions.

To set up the partitions, first open up the Design Partitions Window located under Assignments | Design Partitions Window.

You will notice the top level partition is already present in the window, and this cannot be deleted. You now need to add the processor

partition. Do this by finding the game_of_life module in the Hierarchy window of the project navigator, right-clicking on

it and selecting Set as Design Partition. This should add another entry in the design partition window. If you haven't yet enabled

incremental compilation in the settings window, it will prompt you to do so now. If it does, select

Full incremental compilation. Finally, change the netlist type for the "game_of_life" partition to Source File.

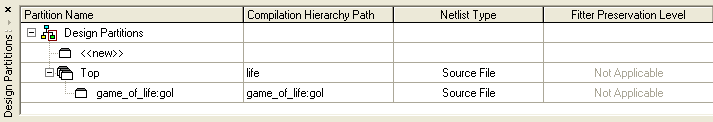

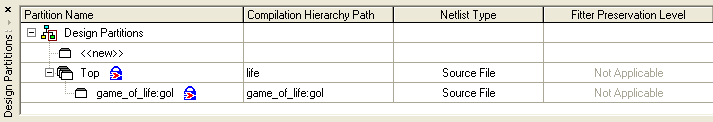

The window should now look like the image below:  LogicLock regionsThe netlist type tells Quartus where to obtain the netlist for the current design from. Source File tells the compiler to use the source files to create the netlist, which is what a standard compilation does. You now need to assign LogicLock regions to each of the partitions you have created (including the top- level partition). These are regions of the FPGA that will contain each partition. To do this, right-click on each of the 2 partitions and select Create New LogicLock Region. The design partitions window should now look like this: You should now perform a full compilation of the project. Once this has completed, change the netlist type of the game_of_life module to Post-Fit and the fitter preservation level to Placement and Routing. You should now have incremental compilation set up and so if you do not change any of the files within the game_of_life partition, this should not be re-synthesised or re-fitted, significantly reducing the compilation time. Check this has been set up correctly by peforming another compilation. The time taken should now be significantly reduced.

|