Introduction to Computer Architecture

Past Exam Questions

Please note that the course used to be called Computer Design, so past exam questions are under that title: Past Exam Questions in Computer Design

Course Handout

The following materials are available for those in the cam.ac.uk domain. Lectures are being presented live. For videos - see below.

Errata

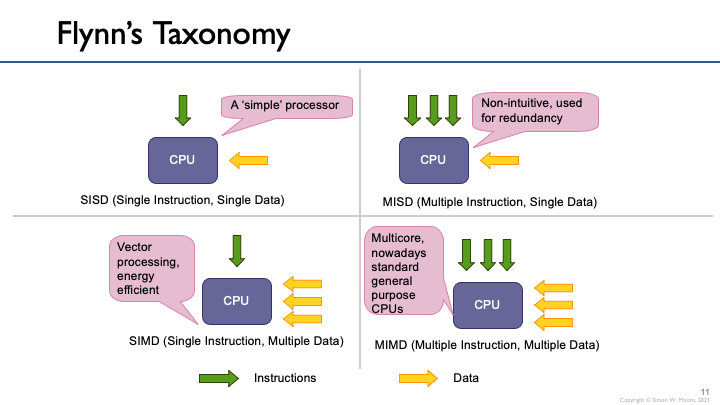

- Lecture 11 slide 11 - SIMD means Single Instruction Multiple

Data

- Lecture 11 slide 20 - this slide refers to "die" meaning a unpackaged silicon chip in this context.

- Lecture 11 slide 27 - The following bullet point is a little opaque: "Concurrency at ranks and banks gives bandwidth". In more detail: since each bank and rank operate independently, then you can be doing multiple operations concurrently instead of having to wait for a single operation to complete. This increases the bandwidth for getting data out of the memory system.

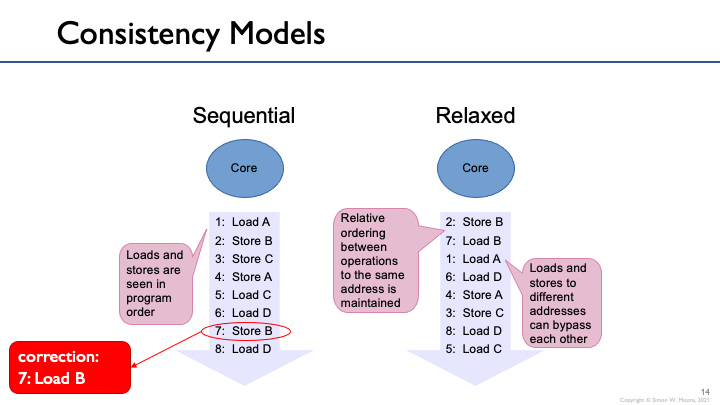

- Lecture 13 slide 14 - There is a minor inconsistency between the

list of sequential memory accesses and the relaxed ones - see

below:

- Lecture 13 slide 37 - The unlock code:

st #0, 0(r1)

uses an immediate as the source, which is not permitted in RISC-V assembler but is allowed in x86-64. Instead we could use thezeroregister to source a zero:

st zero,0(r1)

Similarly, the lock code presented in other slides:

mov r3, #0

st r3, LOCK

Could be replaced with:

st zero, LOCK - Lecture 13 uses

llin assembler for load-linked, which is used by MIPS processors. RISC-V calls the instruction load-reserved withlrused for the assembler mnemonic. The principles are the same.

Videos

Lectures are being presented live. Recordings are also available under the Recordings tab for the local version and the YouTube tab for a YouTube version that includes captions. Please use the local version where possible to conserve bandwidth.

Lectures 1-10 videos are a rerelease of the videos from 2020 with minor corrections and the title slide updated to reflect the change in course title. These are narrated by the current lecturer: Simon Moore.

Lectures 11-16 videos are the 2020 videos under the old course title but the same content as this year but with the 2020 lecturer: Tim Jones. The current lecturer (Simon Moore) is providing live versions of these lectures, which due to their live nature will be less polished than Tim's version. Also please note that Simon has now realised that if he skips backward in slide decks to answer questions it appears to confuse PowerPoint that is being used to present and record the show. This problem has certainly impacted the recording of lecture 13.

Laboratories

The ECAD+Arch laboratory sessions are loosely coupled to this lecture course. Please review the laboratory pages since there is a compulsory component.

Supervision Exercises

Recommended text

Computer Organization and Design - the hardware/software interface (RISC-V edition), Patterson and Hennessy, 2017.

Supervision Guide

Supervision exercises are available here: Supervision Questions (PDF). Supervisors can find sample answers on the supervisors tab.

Additional Material

- The RISC-V instruction set reference manual is available from the RISC-V foundation as a PDF

In the news

A few news articles that relate to the course.

- Silicon manufacture: TSMC in the news

- Apple M1 Pro and M1 Max silicon specs:

AnandTech and

Toms Hardware

Compare the specs. with a recent Intel i9 desktop chip or a recent AMD server chip, e.g. memory bandwidth, though remember the Apple chip has an integrated GPU that will share the memory bandwidth.