ECAD and Architecture Practical Classes

Lablet 1.2 - System on Chip Design and Software

A component is a functional unit with a well-defined interface. The most basic components, from synchronisers to simple processors, are written in a HDL, such as SystemVerilog. We now move away from writing Verilog and focus on building a custom System on Chip (SoC). using existing components as building blocks.

Qsys (Altera's SoC design tool) operates at the component level of abstraction, allowing components to be connected together using streaming (point-to-point) and bus (master-slave) paradigms. Communication with bus devices is memory-mapped: each device is represented as an address range; reading and writing data to these addresses causes the corresponding device to perform some operation.

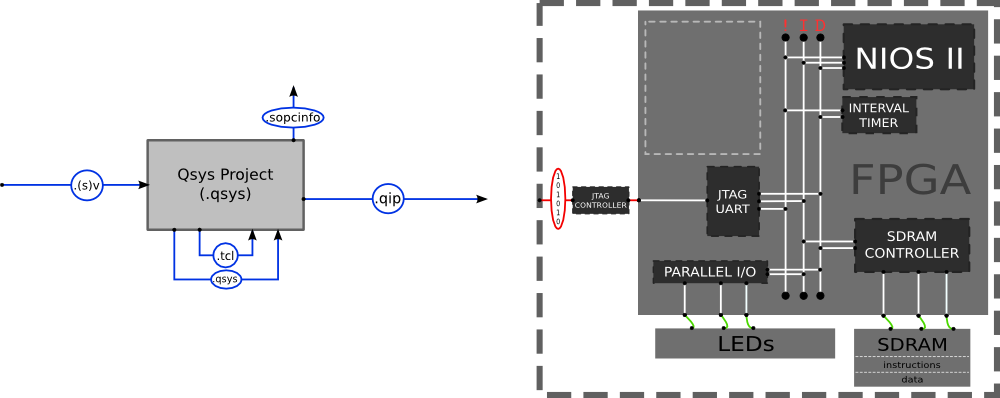

The aim of this section is to guide you through building the FPGA SoC shown in the diagram above. It consists primarily of a NIOS II processor acting as a bus master, with some memory (SDRAM) and Parallel I/O (PIO) adapters as slaves. The PIOs provide a memory-mapped interface to a few board peripherals, such as the red LEDs.

Qsys creates a hierarchy of system-generated verilog modules from your SoC design which you will instantiate in a Quartus project and then synthesise and use to program the FPGA on the tPad.

Getting Started

You first need to create a new Quartus project using the same procedure as for the first lab, calling it ecad_lablet_1_2 this time. Note: don't forget to include the pin definition file and import the assignments. Please don't copy the whole of the the project you created for the last lablet. This tends to result in hard to diagnose bugs.

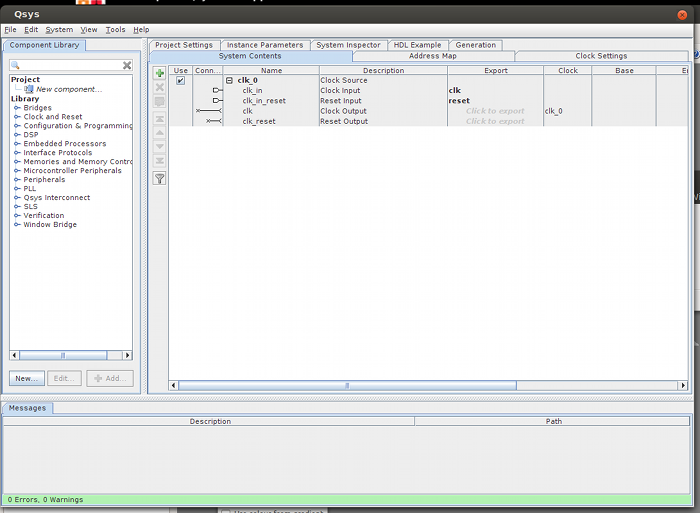

Start Qsys by selecting Tools | Qsys.

On the left of the Qsys window is a list of components, grouped by their type. The main panel has several tabs; System Contents is where components are instantiated and connected together.

There are two standardised interfaces for connecting Qsys components: Avalon-MM components communicate in a memory-mapped (bidirectional, addressed) fashion; Avalon-ST components communicate by streaming (unidirectional, optionally has channels).