Lab 1 - Synthesis, System on Chip Design and Software

This first lab is made up of two parts. We expect that the first part should take you one week and the second part two weeks. You should be familiar with SystemVerilog, a low-level HDL introduced by the online tutor.

Lablet 1.1 - Synthesis

The first part of this lab introduces the tPad board and Quartus. You will write some SystemVerilog HDL and then use Quartus to synthesise it into a form which can be used to program the Cyclone IV FPGA on the tPad.

Lablet 1.2 - System on Chip Design and Software

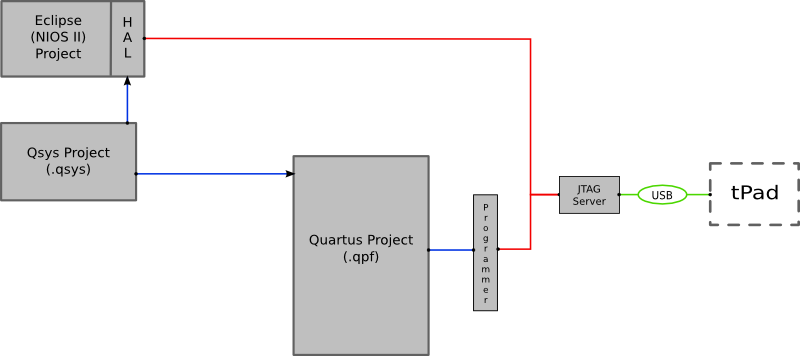

The second part of this lab introduces two additional tools: you will use Qsys to build a simple processor architecture; this will be synthesised to hardware on the tPad via Quartus. You will then use Eclipse for NIOS to write and build a simple C program that will run on a NIOS embedded processor that is synthesised into the FPGA as part of the Qsys System in Chip. This program will interact with other parts of the hardware such as the touchscreen, buttons and memory.

Linux and Tools

We will use the Altera Quartus and Qsys tools under Linux. These tools are available on MCS machines in the path:

/ux/clteach/swm11/altera/

To use the tools some paths and environment variables need to be set up. Use the following command in a terminal to do this:

source /ux/clteach/swm11/setup.bash

You will need to repeat this every time you open a new terminal.

Quartus can then be started using the command:

quartus &

We tend to start other tools (Qsys, Eclipse for NIOS, etc.) using the Quartus GUI.

| Back to ECAD Labs | | | Next |