ECAD and Architecture Practical Classes

Megafunctions

Megafunctions - what are they?

A megafunction is a pre-built module that performs a commonly required function. This prevent the developer having to write these modules themselves, hence saving a lot of development time. Altera ship several megafunctions with Quartus covering a range of tasks such as a FIFO buffer, arithmetic units - add, multiply, divide etc., several DSP modules, and a lot more besides.

Adding a megafunction to a project

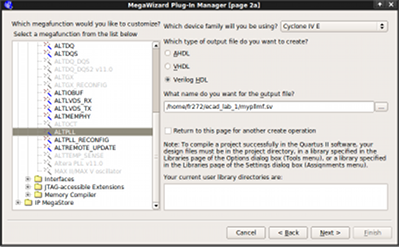

Begin by selecting Tools | MegaWizard Plug-In Manager from the menu, and when prompted, select Create a new custom megafunction variation On the next screen, there is a tree view on the left hand side showing the various megafunctions available. On the right hand side, ensure that Cyclone IV E is the device family selected, and Verilog HDL is the output language. Open up the node marked I/O and select ALTPLL in the list that is produced. Finally, give the file the name mypllmf.sv, ensuring it is saved in the working directory for your project. Click Next

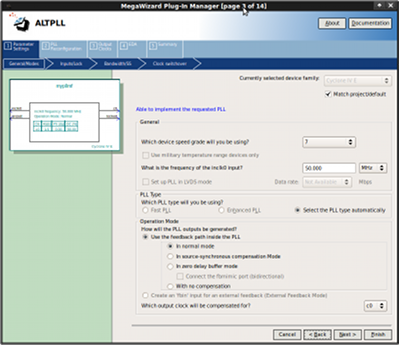

You should now be on page 3 of 10 of the wizard. On this page, set the

Device speed grade to 7 and set the frequency of the

inclock0 input to 50 MHz. Leave the other settings as

default, and click Next. Since we are interested only in

changing the frequency of the clock signal, we do not require the

other features this megafunction provides, such as an asynchronous

reset input, thus, un-tick all check boxes on page 4 of the

wizard. This should leave 2 wires shown on the diagram at the top

left, inclk0 and c0. Click Next until you reach page 8.

You should now be on page 3 of 10 of the wizard. On this page, set the

Device speed grade to 7 and set the frequency of the

inclock0 input to 50 MHz. Leave the other settings as

default, and click Next. Since we are interested only in

changing the frequency of the clock signal, we do not require the

other features this megafunction provides, such as an asynchronous

reset input, thus, un-tick all check boxes on page 4 of the

wizard. This should leave 2 wires shown on the diagram at the top

left, inclk0 and c0. Click Next until you reach page 8.

You should now be on the page titled c0 - Core/External Output Clock.

This page allows you to specify parameters for the output clock of this module.

You can either select Enter output clock parameters and enter a pair of

integers into Multiplication factor and Division factor or select

Enter output clock frequency and enter the desired clock rate in MHz.

You should now be on the page titled c0 - Core/External Output Clock.

This page allows you to specify parameters for the output clock of this module.

You can either select Enter output clock parameters and enter a pair of

integers into Multiplication factor and Division factor or select

Enter output clock frequency and enter the desired clock rate in MHz.

Click Finish to move to page 10 of the wizard, which displays a list of the files that will be created. Click Finish again to create the megafunction.

When asked if you want to add Quartus IP files to the project, tick the box and answer yes. This adds the megafunction to your project.

Open up the toplevel.sv file as follows: in the project window, click on the files tab, look under Device Design Files and double-click on toplevel.sv. At the top of the module insert:

mypllmf pll(.inclk0(CLOCK_50), .c0(clk));

This instantiates the Megafunction module that has just been created. The module definition can be found in the file mypllmf.sv.