ECAD and Architecture Practical Classes

Getting started - an introduction to Quartus

Starting Quartus and making a new project

First, create a new directory for this project in your filespace, perhaps called \lab1\pong.

Important:Some tools in Quartus do not like paths with spaces in, so ensure all file and directory names you choose do not have spaces in them.

Into this folder, download the files:

DE2_pin_assignments.csv

pong.sdc

pong.sv

defines.sv

params.sv

renderer.sv

The files are, respectively, the assignments file to tell Quartus what pins on the FPGA to connect up to port names to be

used in the Verilog code (e.g. LEDR[17:0]); a design constraints

file in Synopsis Design Constrains (SDC) format which tells the

tools about the input clocks; the top level module for the project, which connects all the other modules together;

a file defining several constants used throughout the project; a module producing the VGA parameters; and a module which

does the rendering on screen.

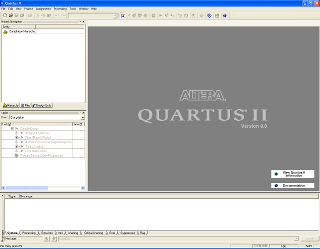

You should now open the Quartus II 10.0 program from the Start menu. It is located under PWF Programs | Teaching Packages | Computer Laboratory | Altera100 If you experience any licensing issues here, refer to the troubleshooting page for help. Once loaded, it should look like the screen on the left. At the bottom there is the status window, which produces compilation messages and warnings, which may be useful when trying to debug your project. On the left is the project outline window, this contains a list of all files that are part of your current project.

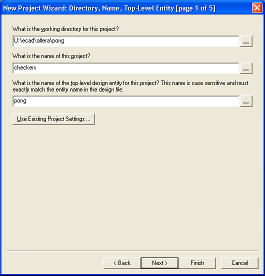

Now, select File | New Project Wizard and click Next to take you to the screen shown on the right.

In the top box, type the directory where you have just saved the 5 files above. In the second box, type the name of the project,

this can be whatever you like, it would be a good idea to name this project "chequers" since you will be displaying a chequered

pattern on the monitor at first.

In the lower box, type "pong" since this is the name of the top-level Verilog module for this

project. Now click Next.

Now, select File | New Project Wizard and click Next to take you to the screen shown on the right.

In the top box, type the directory where you have just saved the 5 files above. In the second box, type the name of the project,

this can be whatever you like, it would be a good idea to name this project "chequers" since you will be displaying a chequered

pattern on the monitor at first.

In the lower box, type "pong" since this is the name of the top-level Verilog module for this

project. Now click Next.

It is useful for the demonstrators to be able to see the progress you make throughout the labs, so it is a good idea to create a new project at each stage. This can be done by copying across the SystemVerilog (*.sv) files and the pin assignment script to a new directory, then following this wizard again.

On the next page, click Add All to add the 4 Verilog files that were downloaded earlier into the project. If these files do not appear in the list, ensure you have saved them in the same directory that you specified as the working directory in the previous step. Alternatively, you can add them one at a time by giving the filename and click Add for each file. Now click Next.

This page lets you select the device you will be programming. In the drop down box at the top, select the family Cyclone II and ensure that Specific device selected in 'Available devices' list is also chequed. Next, in the Available devices list at the bottom, select the chip with name EP2C35F672C6 this is the type of FPGA that is on the DE2 board.

Now click Finish to create your project.

Finally, you need to import the pin assignments from the .csv file you downloaded earlier. To do this, click Assignments | Import Assignments... click on the button labelled "..." and select the DE2_pin_assignments.csv file. Click OK and then click OK again to import the assignments.

Important: Failure to assign pins will result in your design not being connected to the outside world and it will also be optimised to nothing since it doesn't have any used input and output signals, all of which is not very useful. You must import the assignments in every project you create.

Quartus uses Verilog 2001 as the default language. Change this to SystemVerilog using Assignments | Settings | Analysis & Synthesis Settings | Verilog HDL Input and then tick SystemVerilog-2005. Then hit Apply and OK.