We use the terms hard and soft to differentiate between functions are are determined by the fabrication masks and are loaded into the programmable fabric.

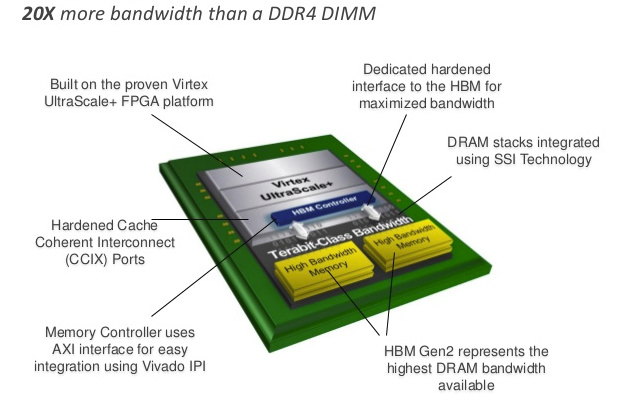

Although it was common to put so-called soft CPU cores in the programmable logic, today's devices have hardened CPUs and many other hard IP blocks. Connecting DRAM to FPGAs has become a common requirement in the last decade and hardened DRAM controllers are now common.

The high cost of ASIC masks now makes FPGA suitable for most medium volume production runs (e.g sub 10,000 units) which includes most recording studio equipment and passenger-in-the-road detection for high-end cars.

The dark silicon trend means we can put all IP blocks on one chip provided we leave them mostly turned off.

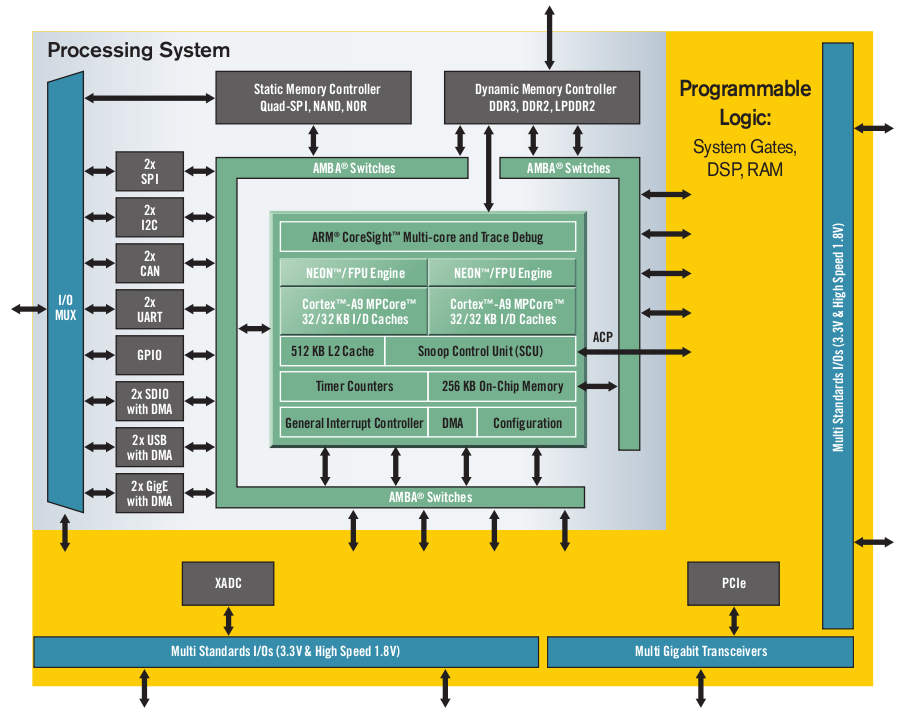

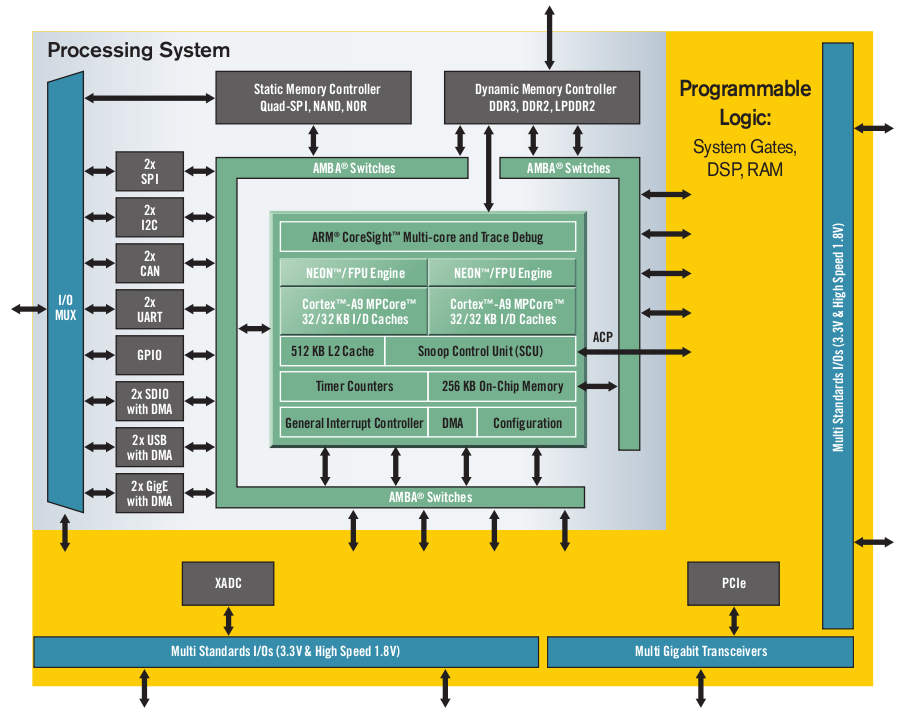

The Zynq from Xilinx has two ARM cores, all the standard SoC IP blocks and an area of FPGA programmable logic, all on one die.

The same DRAM bank is accessible to both the hardened ARMs and the programmable logic.

»Xilinx Zynq-7000 Product Brief (PDF)

Flexible I/O routing means physical pads can be IP block bond outs, GPIOs or FPGA I/O blocks.

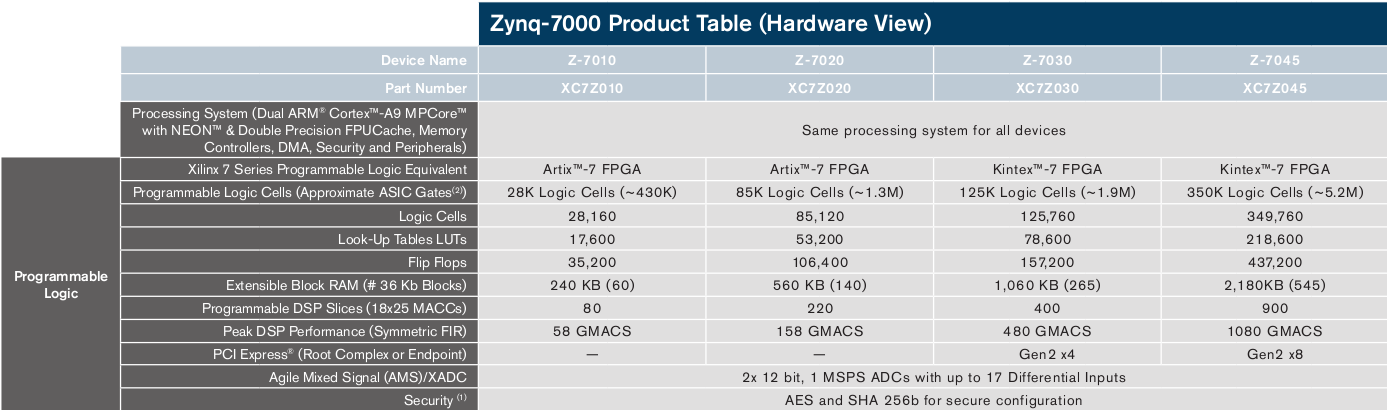

Vital statistics for the first Zynq offerings:

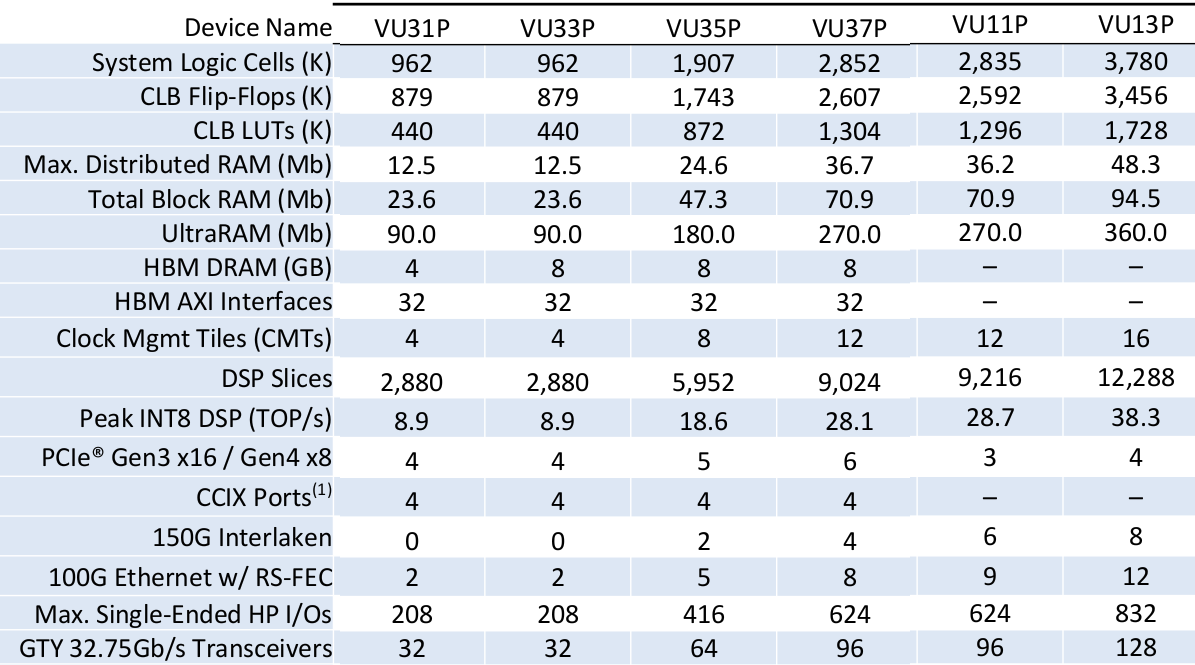

Figures for some more-recent devices:

| 12: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |