Lab 1 - Synthesis, Architecture and Software

This first lab itself contains two parts. As a guideline, the first part should take one week and the second part should take two weeks. You should be familiar with SystemVerilog, a low-level HDL introduced by the online tutor.

Lablet 1.1 - Synthesis

The first part introduces the tPad board and Quartus. You will use Quartus to synthesise some SystemVerilog code you have written into a form which can be used to program the Cyclone IV FPGA on the tPad.

Lablet 1.2 - Architecture and Software

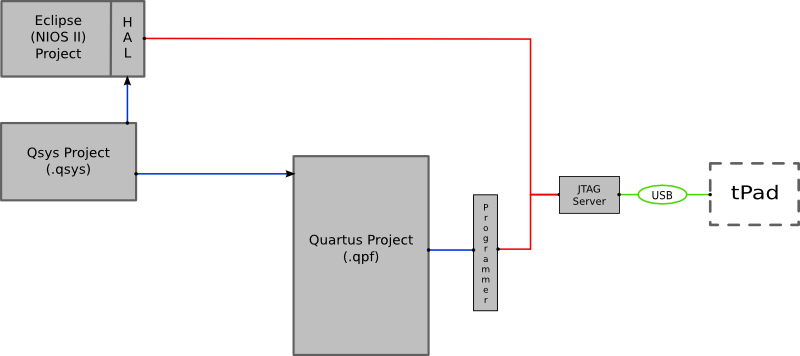

The second part introduces two additional tools: you will use Qsys to build a simple processor architecture; this will be synthesised to hardware on the tPad via Quartus. You will then interact with the hardware by completing a simple C program.

Linux and Tools

Unlike previous years, this year we will use the Altera Quartus and Qsys tools under Linux. These tools are available here:

/ux/clteach/swm11/altera/

To use the tools you will first need to setup paths and environment variables using the following script which needs to be sourced using the following at the command-line:

source /ux/clteach/swm11/setup.bash

Quartus can then be started using:

quartus &

We tend to start other tools (Qsys, Eclipse for NIOS, etc.) using the Quartus GUI.

| Back to ECAD Labs | | | Next |