HOME PREV FURTHER NOTES NEXT (More-advanced behavioural specification:)

Beyond Pure RTL: Behavioural descriptions of hardware.

What has 'synthesisable' RTL traditionally provided ?

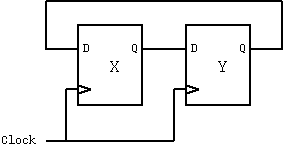

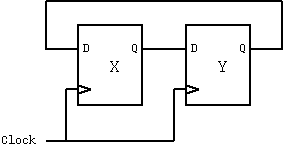

A circuit to swap two registers.

| This PURE RTL form can

always @(posedge clk) begin

x <= y;

y <= x;

end

be expressed with this behavioural program:

always @(posedge clk) begin

t = x;

x = y;

y = t;

end

|

The thread is confined to one always block.

The synchonisation with other circuits is fully manual and not

obvious from the RTL (its just in the head of the designer).

The amount of state and state encoding is chosen completely manually.