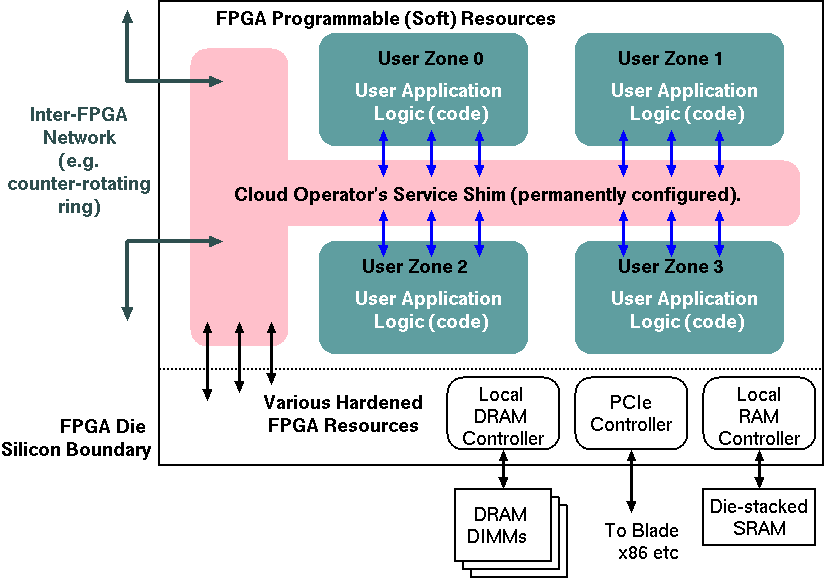

The reconfigurable logic resources of a conventional FPGA can be manually partitioned into user reconfigurable areas and a shell/shim for service access.

FPGA in the datacentre was first deployed by Microsoft for Bing acceleration. A user-programmable FPGA fabric as part of the Cloud offering was made available by Amazon at the start of 2017.

Where customer designs are loadable into the FPGA, security issues arise. Overheating, denial of service and data theft must be avoided and a means to virtualise (share) the FPGA resources is needed.

One approach to virtualisation is to use dynamically-loaded modules under the `Shell' and `App' approach to FPGA real-estate where the customer only has access to the part of the die via partial-reconfiguration. The service shim or shell provides a protected service layer.

Disadvantages of this technique are that quite a lot of real estate (and especially the multiplier resource therein) is consumed with overhead. Also there are design fragmentation inefficiencies. And many of the FPGA resources, such as most of the I/O pins and hardened peripherals go unused (not a problem for a Dark Silicon future!).

All recent FPGA families support dynamic loading of selected parts of the die while the remainder continues operating. The reconfiguration time is typically 10 to 100 ms per zone.

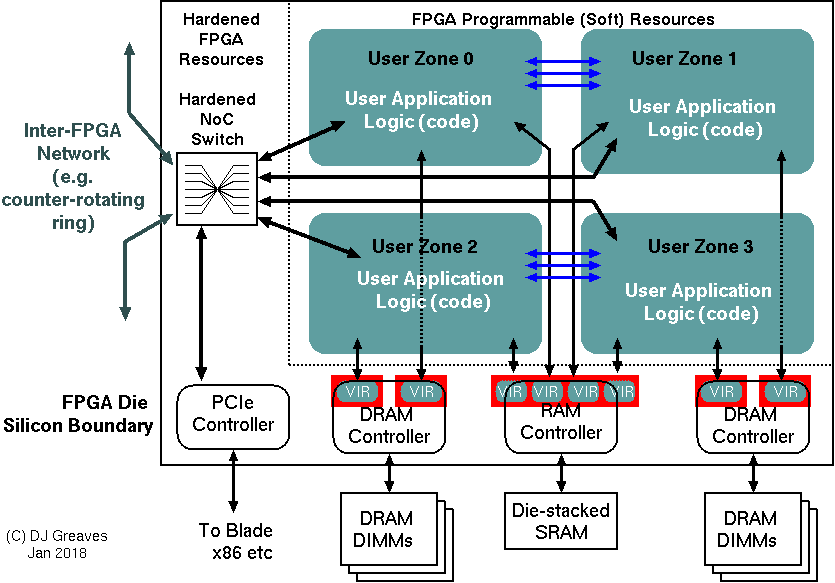

It is a possible that a future generation of FPGA devices will be developed specialised for server blades in the cloud. The user logic will connect to the outside world only through a service network. Kiwi uses such a NoC for O/S access, as does LEAP. But reconfigurable interconnection between adjacent zones that jointly host an application (blue) might be provided. Having the service network hardened makes it about 100-fold more area efficient, allowing much more complexity, security and monitoring.

The local memory devices would also provide virtualisation assistance in their hardened controllers.

»Intel/Altera Acceleration As A Service»Amazon EC2 F1 Instances

| 6: (C) 2012-17, DJ Greaves, University of Cambridge, Computer Laboratory. |