Clock trees consume quite a lot of the power in an ASIC and considerable savings can be made by turning off the clocks to small regions. A region of logic is idle if all of the flip-flops are being loaded with their current contents, either through synchronous clock enables or just through the nature of the design. »EDA DESIGNLINE

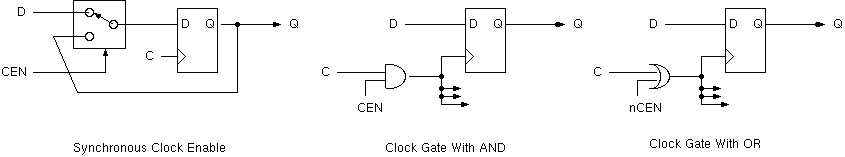

Replace `nice clean' synchronous clock enable with a logic gate.

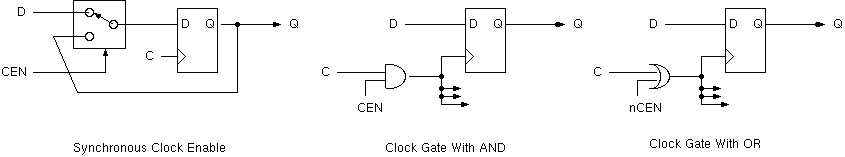

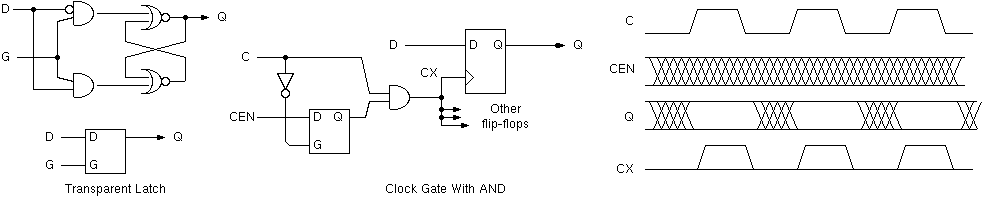

One clock control logic gate serves a number of neighbouring flip-flops: state machine or broadside register.

Problem with AND gate: if CEN changes when clock is high: causes a glitch.

Problem with OR gate: if CEN changes when clock is low: causes a glitch.

Care needed to match clock skew when crossing to/from non-gated domain: avoid shoot-through by building out the non-gated parts as well. Shoot-through occurs when a D-type is supposed to register its current D input value, but this has already changed to its new value before the clock signal arrives.

| 31: (C) 2012-18, DJ Greaves, University of Cambridge, Computer Laboratory. |