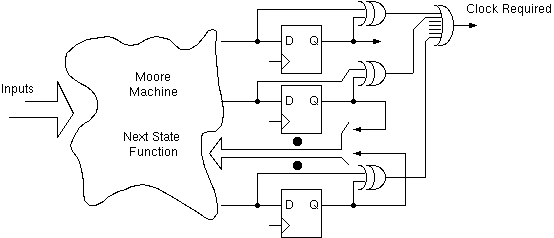

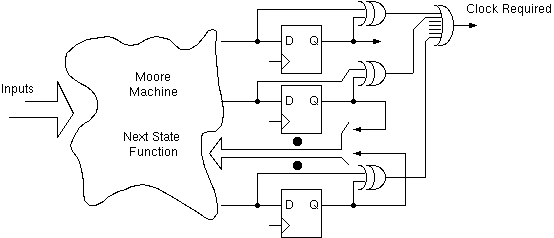

How to generate clock enable conditions ? One could have software control for complete blocks (additional control register flags, as per power gating). But today's designs automatically detect on a finer-grain basis. Synthesiser tools can automatically insert clock required conditions and insert the additional logic. Automatic tools compute `clock needed' conditions.

A clock is `needed' if any register will change on a clock edge.

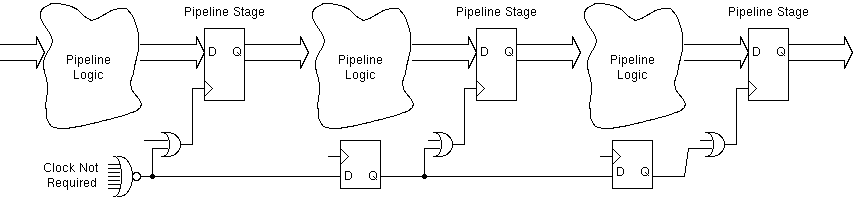

If not a straightforward pipeline, need to be sure there are no `oscillating' stages that retrigger themselves or an `earlier' stage (add further runtime checks or else statically know their maximum settling time and use a counter). The maximum settling time, if it exists, is computed in terms of clock cycles using static analysis. Beyond the settling time, all registers will be being re-loaded with their current data on each clock cycle.

Save further power: shortly we look at dynamic frequency and voltage scaling.

| 32: (C) 2012-18, DJ Greaves, University of Cambridge, Computer Laboratory. |