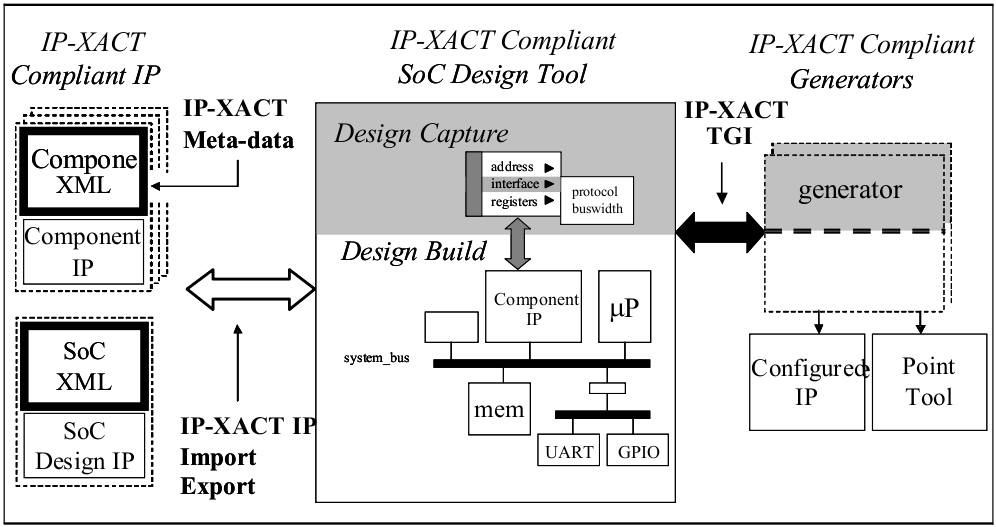

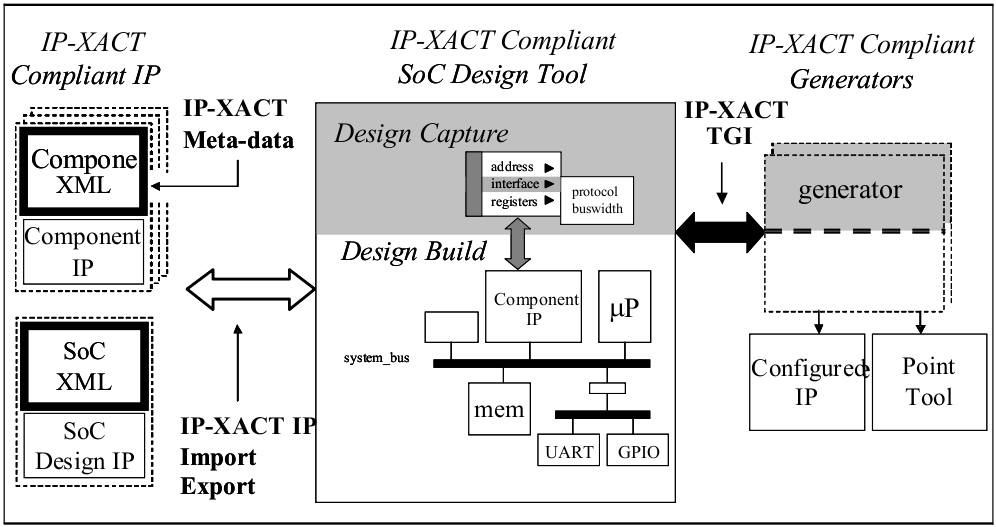

IP blocks and bus standards are stored in libraries and indexed using datasheets for each block in xml according to the IP-XACT schema.

A schematic design capture editor supports creation and editing of a high-level block diagram for the SoC.

The SoC design is then output as IP-XACT conformant XML.

Various synthesis plugins, termed `generators' produce the inter-block structural wiring RTL that is otherwise highly tedious and error prone to manually create. They may also instantiate bus bridges and port multiplexors and other glue logic.

Automatic generation of memory maps and device-driver header files is also normally supported. Header files in RTL and C are kept in synch. Testbenches following OVM/UVM coding standards might also be rendered.

Other outputs, such as power and frequency estimates or user manual documentation are typically generated too.

Greaves+Nam created a glue logic synthesiser »Synthesis of glue logic, transactors, multiplexors and serialisors from protocol specifications.

Perhaps explore the free plugin(s) for Eclipse if you are keen.

| 38: (C) 2012-18, DJ Greaves, University of Cambridge, Computer Laboratory. |