ECAD and Architecture Practical Classes

Thacker's Tiny Computer 3

Introduction

Turing award winner Charles (Chuck) Thacker has many decades of experience designing computer systems. An architecture called the Tiny Computer 3 was designed by him in 2007 as a teaching aid - see the PDF paper.

- ttc.sv

- An implementation of the TTC architecture in SystemVerilog for use in the labs.

- ttcasm.jar

- A Java assembler producing TTC bytecode.

Assembly Guide

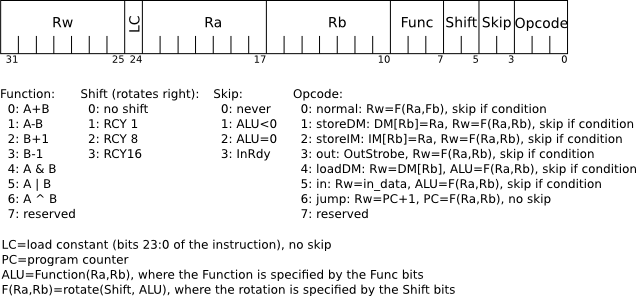

The Computer Design course discusses the architecture of the processor and presents the following instruction format.

The following is an overview of the assembly syntax we chose to represent instructions; the full grammar is more expressive.

- comments

- Start with a # and continue until the end of the line.

- registers

- All 128 registers are general purpose, named r0 through r127.

- constants

- Unsigned. For example, lc r0 1000 assigns r0 to 1000. This is the only immediate instruction statement.

- labels

- End with a colon e.g. mylabel:. Labels are resolved to instruction addresses by the assembler. For example, lc r0 mylabel (no colon) assigns r0 to the address of the first instruction after mylabel.

- functions

- These include add, sub, and, inc, dec. The first three compute using two register operands (as below), the latter use only one register operand.

- <opcode> <func> rw ra rb

- Computes a function of the operands ra and rb; using this result and other inputs, the opcode determines the value assigned to the destination register rw. For example, normal add r2 r2 r2 doubles the value in register r2; if no opcode is given, normal is inserted by the assembler.

- rotate

- The binary result of the function can be rotated to the right by 1, 8 or 16 bits. Append to the above either rot1, rot8 or rot16 as appropriate. For example, if r2 stores the value 1, then and r2 r2 r2 rot1 changes this to 2^32.

- skip

- The next instruction can be conditionally skipped, subject to the result of the function. Append to the general format either sltz or sez to skip if the result is less than (sltz), or equal (sez) to zero.

Pseudo-instructions are also provided for your convenience. Pseudo-instructions get expanded out to one or more TTC instructions. Refer to the full grammar for how to express these in the above syntax.

- ldin rw

- A TTC component has an input stream for receiving data from external sources. This instruction loads a value on the input stream into register rw. Because the stream may not hold a value when the instruction is executed, you may wish to block until the stream is ready (see the example program below).

- stout ra

- A TTC component has an output stream for sending data to an external receiver. This instruction puts the value in register ra into the output stream.

- jmp r1 r0

- Stores the incremented program counter in register r1 and jumps to the address stored by register r0.

- bnez r3 r4 r5

- If the value stored by register r4 is non-zero, store the incremented program counter in r3 and jump to the address stored by register r5.

- bgez r3 r4 r5

- Similar.

The following example program accepts a value from the input stream, calculates the sum of the integers between 0 and the input value, and puts the result on the output stream.