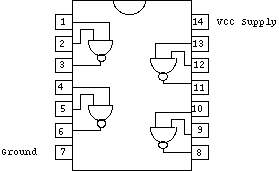

At any one time, there is a choice of implementation technologies. Here is the speed-power product for three versions of the 7400-format quad NAND gate, fabricated from different contemporary technologies in 1985. (This is a board-level part and on-chip much less driving power is needed).

---- ---------- ------ ------------- ------- -------

Year Technology Device Propagation Power Product

delay (ns) (mW) (pJ)

---- ---------- ------ ------------- ------- -------

1975 CMOS CD4011BE 120 ns (10 mW) (1200 pJ)

---- ---------- ------ ------------- ------- -------

1985 CMOS 74HC00 7 ns 1 mW 7 pJ

1985 TTL 74F00 3.4 ns 5 mW 17 pJ

1985 ECL SP92701 0.8 ns 200 mW 160 pJ

---- ---------- ------ ------------- ------- -------

2007 CMOS 74LVC00A 2.1 ns 120 uW 0.25 pJ

---- ---------- ------ ------------- ------- -------

CMOS has been dominant, and in 2007 is the only surviving technology: »74LVC00A.pdf

The 5 volt CMOS gate has the property that it consumes virtually no power when not changing its output. Today's lower voltage CMOS does not turn the transistors off as much, leading to significant static leakage currents.

The ECL gate is an older technology, with a higher speed-power product, but it is still useful since it is the fastest.

Gates of medium complexity or larger (rather than SSI gates as these are) tend to be an order better in speed or power, since they do not have output stages designed for driving long nets.

Alternatives to silicon, such as GaAs have been proposed for general purpose logic. GaAs has four times higher electron mobility and so transistors of a given size switch on and off that much faster. However, increases in the speed of silicon, simply by making things smaller, have turned out to be a more effective way forward. So far!