Flip-flop migration does alter state encoding.

Migration may be manually turned on or off during logic synthesis by typical RTL compiler tools.

It exchanges delay in one path for delay in another - aim to achieve balance.

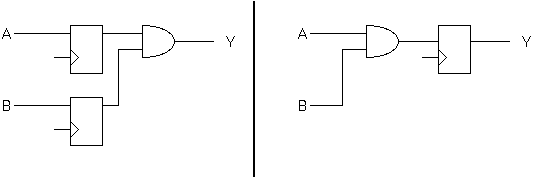

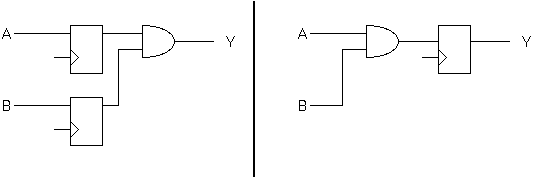

A sequence of such transformations can lead to a shorter critical path overall. In the following example, the first migration is a local transformation that has no global consequences:

Before: Migration 1: Migration 2 (non causal): a <= b + c; b1 <= b; c1 <= c; q1 <= (dd) ? (b+c): 0; q <= (d) ? a:0; q <= (d) ? b1+c1:0; q <= q1;The second migration, that attempts to perform the multiplexing one cycle earlier will require an earlier version of d, here termed dd that might not be available (e.g. if it were an external input we need knowledge of the future).

An earlier version of a given input can sometimes be obtain by delaying all of the inputs (think of delaying all the inputs to a bookmakers shop), but this cannot be done for certain applications where system response time (in-to-out delay) is critical.

Problems arising:

but retiming can overcome structural hazards (e.g. the `write back' cycle in RISC pipeline).

Other rewrites commonly used: automatically introduce one-hot and gray encoding, or invert for reset as preset.

Large FSMs are generally recoded by FPGA tools by default so that the output function is easy to generate. This is critical for good performance with complex HLS sequencers.

| 46: (C) 2012-17, DJ Greaves, University of Cambridge, Computer Laboratory. | |