RAMs vary in their size and number of ports.

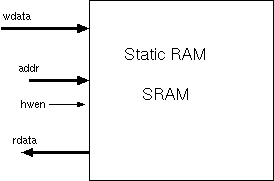

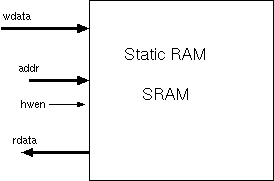

Single-ported SRAM is the most important and most simple resource to connect to our bus. It is a target only.

Today's SoC designs have more than fifty percent of their silicon area devoted to SRAM for various purposes.

The `hren' signal is not shown since the RAM is reading at all times when it is not reading.

Most RAMs in use on SoCs are synchronous with the data that is output being addressed the clock cycle before.

RAMs below a few hundred bits should typically be implemented as register files made of flip-flops.

RAMs for SoCs are normally supplied by companies such as Virage and Artizan. A `RAM compiler' tool is run for each RAM in the SoC. It reads in the user's size, shape, access time and port definitions and creates a suite of models, including the physical data to be sent to the foundry.

High-density RAM (e.g. for L2 caches) may clock at half the main system clock rate and/or might need error correction logic to meet the system-wide reliability goal.