HOME

UP

PREV

NEXT (Rent's Rule Estimate of Wire Length)

Typical macroscopic performance equations: DRAM example.

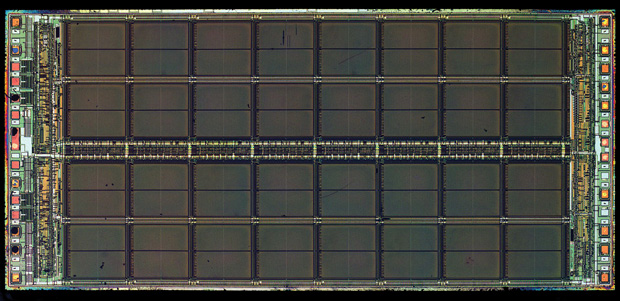

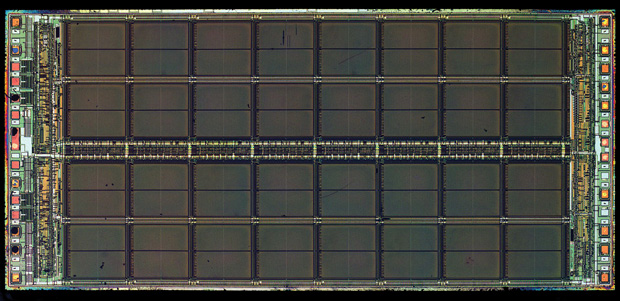

A DRAM channel is some number of DRAM die (eg.\ 16) connected to a set of I/O pads on a controller.

The channel data width could typically be 16, 32 or 64 bits. The capacity might be 16 GByte.

- Controller static power: The pads forming the so-called `phy' will typically consume half a watt or so, even when idle.

- DRAM static power: each die takes about 100 mW when idle but may enter a sleep mode if left unused for a millisecond or so, reducing this to 10 mW or so.

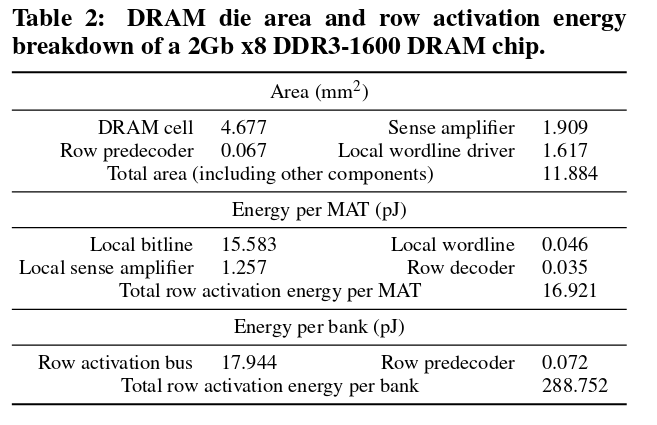

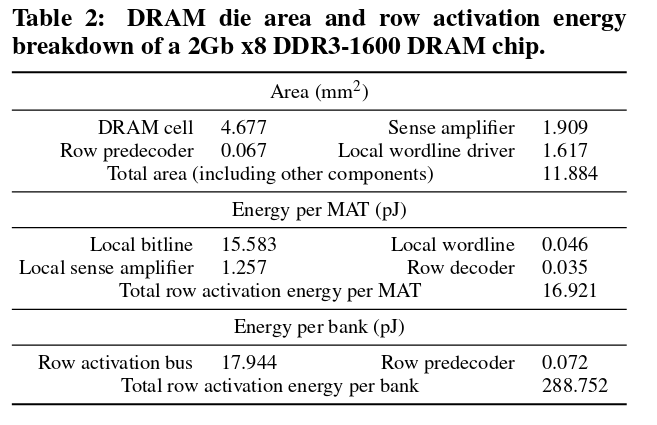

- Each row activation takes dynamic energy (see table).

- Each column burst transfer takes on-chip energy and PCB trace energy.

- Each row closure (writeback/de-activate) takes dynamic energy (see table).

- Refresh operations consume a small mount of dynamic energy (see exercise sheet for numbers).

»Partial Row Activation for Low-Power DRAM System - Lee, Kim and Hong»Calculating Memory System Power for DDR3

»Partial Row Activation for Low-Power DRAM System - Lee, Kim and Hong»Calculating Memory System Power for DDR3

The Prazor virtual platofrm integrates the University of Maryland DRAM simulator.

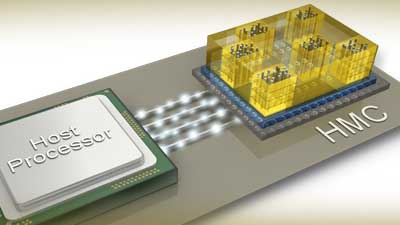

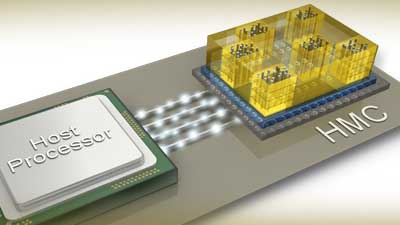

The phy is the set of pads that operate

with high performance to drive the PCB traces. Such power can be minimised if the traces are

kept short with using multi-chip modules or die stacking.

Micron have released a multi-channel DRAM module: the Micron HMC. This can have a number

of host nodes sharing a number of die-stacked DRAM chips.