The four-phase handshake just described is suitable for asynchronous interfaces. It does not refer to a clock.

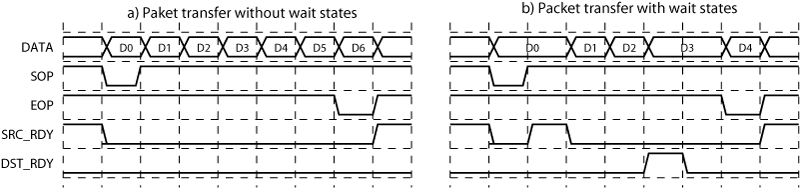

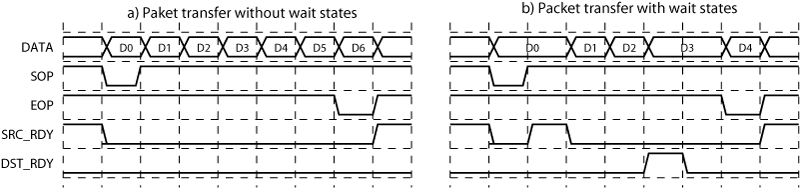

A very common paradigm for synchronous flow control of a uni-directional bus is to have a handshake net in each direction with bus data being qualified as valid on any positive clock edge where both handshake nets are asserted. The nets are typically called `valid' and `ready' with valid being in the direction from initiator to target (or from the data source for simplex protocols).

This paradigm forms the essence of the LocalLink protocol from Xilinx and AXI-streaming protocols defined by ARM.

Like the four-phase handshake, LocalLink has contra-flowing

The interface nets for an eight-bit transmitting interface are:

input clk; output [7:0] xxx_data; // The data word - here just a byte but any size is possible. output xxx_sof_n; // Start of frame output xxx_eof_n; // End of frame output xxx_src_rdy_n; // This is the 'valid' signal input xxx_dst_rdy_n; // reverse direction ready signal.

On top of the word-level handshake signals, LocalLink defines start-of-frame and end-of-frame signals. These provide a packet delineation layer on top of the word-level protocol.

Note: all control signals are active low (denoted with the underscore n RTL suffix ) in LocalLink.

A feature of this protocol is that both sides can freely assert and deassert their handshake net at will. A common implementation error is to wait for the other side to assert its handshake net first. This is a bad idea, since if both sides wait we have deadlock.

| 4: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. | Flash Player Upgrade Needed |