The mainstream RTL languages, Verilog and VHDL, do not provide synthesis of handshake circuits (but this is one of the main innovations in some more recent HLDs such as Bluespec).

We'll use the word transactional for protocol+interface combinations that support flow-control.

If synthesis tools are allowed to adjust the delay through components, all interfaces between components must be transactional and the tools must understand the protocol semantic.

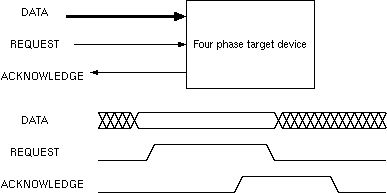

Here are two imperative (behavioural) methods (non-RTL) that embody the above protocol:

//Output transactor:

putbyte(char d)

{

wait_until(!ack); // spin till last complete.

data = d;

settle(); // delay longer than longest data delay

req = 1;

wait_until(ack);

req = 0;

}

| //Input transactor:

char getbyte()

{

wait_until(req);

char r = data;

ack = 1;

wait_until(!req);

ack = 0;

return r;

}

|

Code like this is used to perform programmed I/O (PIO) on GPIO pins (see later). It can also be used as an ESL transactor (see later). It's also sufficient to act as a formal specification of the protocol.

| 3: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. | Flash Player Upgrade Needed |