|  |

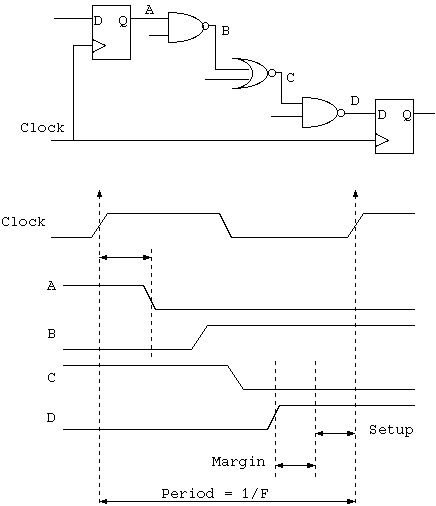

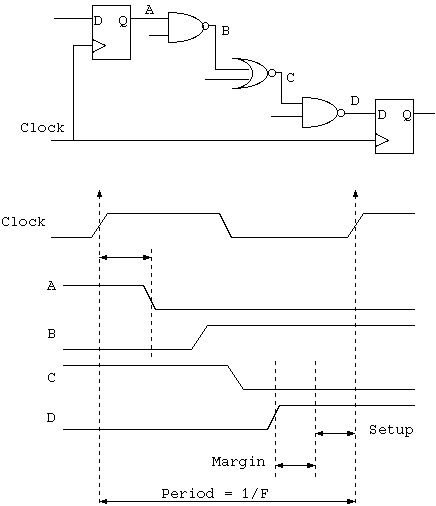

The maximum clock frequency of a synchronous clock domain is set by its critical path.

Total gate delay is then:

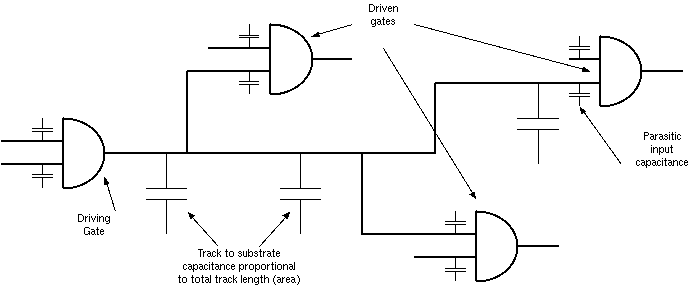

device delay = (intrinsic delay) + (output load x derating factor).

The track-dependent output loading is a library constant times the track area.

The load-dependent part is the sum of the input loads of all of the devices being fed.

For short, non-clock nets (less than 0.1 wavelength), include propagation delay in the gate derating and assume the signal arrives at all points simultaneously.

Only know track length post layout. Pre-layout and pre-synthesis we can predict net lengths from Rent's Rule and RTL-level heuristics.

| 8: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |