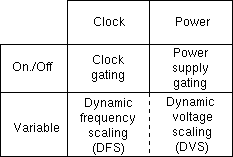

Turning off and slowing down are our friends when it comes to saving power.

Our first power saving technique uses DVFS. We clock quickly and halt or clock slowly and finish just in time. We aim to clock at the lowest suffcient voltage and clock frequency and with the activity ratio as high as possible and minimal halt cycles.

Frequency scaling means adjusting the clock frequency to a subsystem.

The voltage will have to be scaled in tandem to ensure timing is met without wasting energy. Frequency scaling is software controlled by updating divider ratios.

Frequency adjustment can be instant if divider output is directly used. (But when PLLs with analog filters are used, there is inertia, e.g. 1 millisecond).

Voltage adjustment also has inertia and there is design and implementation complexity supporting more than a few voltage regions.

| Clock Gating | Supply Gating | DVFS | |

| Control: | automatic | various | software |

| Granularity: | register / FSM | larger blocks | macroscopic. |

| Clock Tree: | mostly free runs | turned off | slows down. |

| Response time: | instant | 2 to 3 cycles | instant (or ms if PLL adjusted) |

| Proportionally vary voltage: | not possible | n/a | yes. |

| 30: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |