HOME

UP

PREV

FURTHER NOTES

NEXT (DVFS Example)

The Voltage and Frequency Relationship

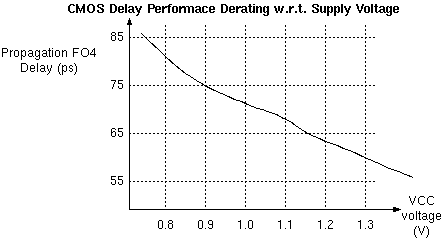

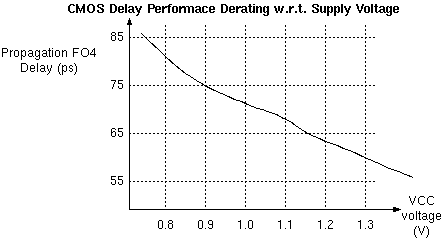

Looking at the derating graph for the standard cell libraries, we

see that in the operating region, the frequency/voltage curve is roughly linear.

CMOS delay is inversely proportional to supply voltage.

A technique that exploits such curves is DVFS -- dynamic voltage with frequency scaling.

Logic with higher-speed capabilities is smaller which means it

consumes greater leakage current which is being wasted while we are

halted. Also leakage energy is proportional to supply voltage (or perhaps sublinear with exponent 0.9ish : as we raise voltage, transistors are indeed turned off more, but P=IV is still increasing).

|

Voltage to a region may be varied dynamically. A higher

supply voltage (at fixed f) uses more power (square law) but allows a higher f.

Operating region of the frequency/voltage curve is roughly linear.

But, logic with higher-speed capabilities is smaller which means it

(generally) consumes greater leakage current which is being wasted while we are halted.

Let's only raise VCC when we ramp up f: classical DVFS.

|

For a fixed task size, energy use is proportional to V squared, so

DVFS is the ideal method (i.e. for predictable, real-time tasks in low-leakage technology):

- Adjust clock f for just-in-time completion (e.g. in time to decode the next frame of a video),

- then adjust VCC to minimal value for reliably meeting the set-up time.

In general servers (ie.\ not for a static/finite workload), ramping voltage up linearly with clock frequency (f) results in dynamic power consumption with a cubic dependence on f.

But work may be bursty, so DVFS is applied (e.g. by a laptop governor).

For all loads, this DVSF approach achieves peak performance under heavy loads and avoids cubic overhead when idle.

In a server farm processing blade we may be thermally limited, so DVFS will be throttled back by rack-level governors or Intel's RAPL.