A DRAM channel is some number of DRAM die (eg.\ 16) connected to a set of I/O pads on a controller. The channel data width could typically be 16, 32 or 64 bits. The capacity might be 16 GByte.

The Prazor virtual platofrm integrates the University of Maryland DRAM simulator.

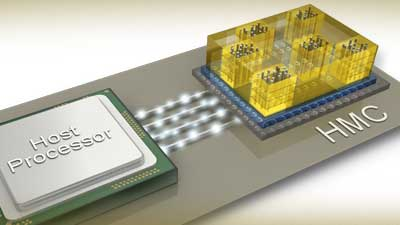

The phy is the set of pads that operate with high performance to drive the PCB traces. Such power can be minimised if the traces are kept short with using multi-chip modules or die stacking.

Micron have released a multi-channel DRAM module: the Micron HMC. This can have a number of host nodes sharing a number of die-stacked DRAM chips. There is /will be an exercise on the sheet where DRAM performance and energy need to be computed/estimated.

| 43: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |