A static analysis tool does not run a program or simulate a design - instead it 'stares' at the source code.

A static timing analyser computes the longest event path through logic gates and clock-to-Q paths of edge-triggered flops.

The longest path is generally the critical path that sets the maximum clock frequency. However, sometimes this is a false result, since this path might never be used during device operation.

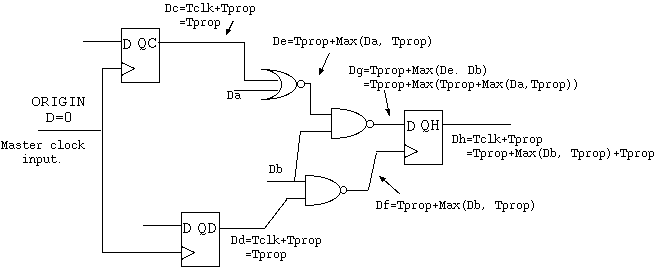

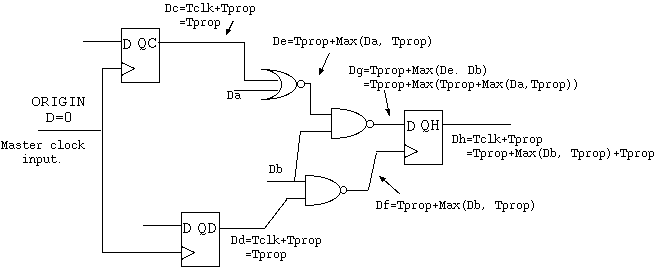

Exercise: (done in lectures): What is the maximum clock freq for this circuit if the output were wrapped round to the input with propagation delays Clk-to-Q=50ps, Nor=40ps, Nand=50ps and 5 ps set-up and 10 ps hold time for the D-types. Is this circuit intrisically horrible and is that spotted by static timing analysis ? (First see Critical Path slide.)

| 55: (C) 2008-17, DJ Greaves, University of Cambridge, Computer Laboratory. | |