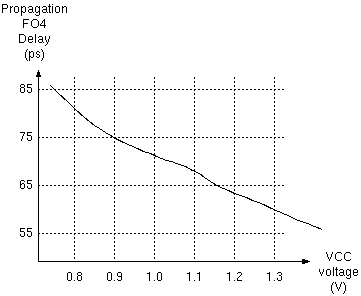

Voltage to a region may be varied dynamically. A higher supply voltage (at fixed f) uses more power (square law) but allows a higher f.

Operating region of the frequency/voltage curve is roughly linear.

But, logic with higher-speed capabilities is smaller which means it consumes greater leakage current which is being wasted while we are halted.

Let's only raise VCC when we ramp up f.