Dynamic clock gating can be fairly fine grain, but we can also turn off power to sections of logic (coarser grain).

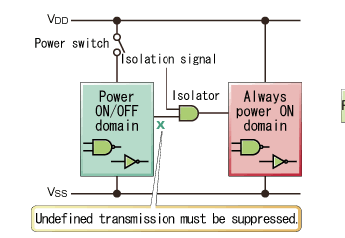

Use power gating cells in series with supply rails.

And use signal isolation and retention cells (t-latches) on data input and output nets.

No register and RAM data retention in block while off.

These techniques typically require some sequencing: several clock cycles to power up/down a region.

Generally, power off/on controlled by software or top-level input pads.

Sometimes power off a whole chip except for a one or two RAMs and register files.

Can also retain volatile contents using a lower supply while clock is off (CMOS RAM data holding voltage).