HOME

UP

PREV

NEXT (Future Trends)

Save Power 4: Dynamic Voltage Scaling

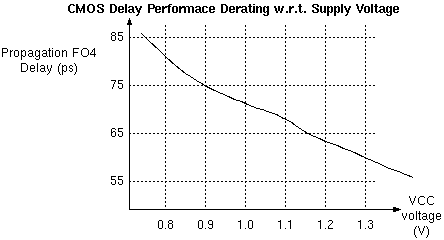

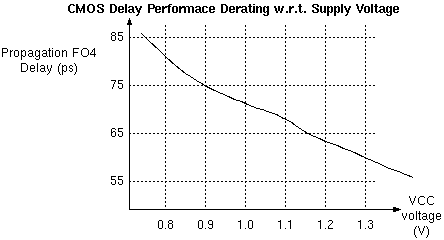

Looking at the derating graph for the standard cell libraries, we

see that in the operating region, the frequency/voltage curve is roughly linear.

CMOS delay is inversely proportional to supply voltage.

Logic with higher-speed capabilities is smaller which means it

consumes greater leakage current which is being wasted while we are

halted. Also leakage energy is proportional to supply voltage (in today's low-voltage logic) (as we raise voltage, transistors are indeed turned off more, but P=IV is still increasing).

|

Voltage to a region may be varied dynamically. A higher

supply voltage (at fixed f) uses more power (square law) but allows a higher f.

Operating region of the frequency/voltage curve is roughly linear.

But, logic with higher-speed capabilities is smaller which means it

(generally) consumes greater leakage current which is being wasted while we are halted.

Let's only raise VCC when we ramp up f.

|

Method:

- Adjust f for just-in-time completion (e.g. in time to decode the next frame of a real-time video),

- then adjust VCC so logic just works.

But Zeno applies still: always aim for

'a'

as high as possible and minimal halt cycles.

Overall: power will then have cubic dependence on f.

But this way we achieve peak performance under heavy loads and avoid cubic overhead when idle.

Combinational logic cannot be clock gated (e.g. PAL and PLA).

For large combinational blocks: can dip power supply to reduce static current

when block is completely idle (detect with XORs).

So a typical SoC uses not only many dynamic clock gated islands, but also some sub-continents with automatic

frequency and voltage variation.

Power isolation originally used on a longer and larger scale (complete continents) but now a lot of power islands

are being used.

It is possible to locally and quickly adjust supply voltage with a series transistor - but wasteful.

An off-chip power supply can be efficiently adjusted, but limited to only a few voltage islands and tens of milliseconds inertia.

For sub 45nm, voltage scaling may not be viable and static leakage may be very high: so clock within the frequency band that works and then power off until next deadline.