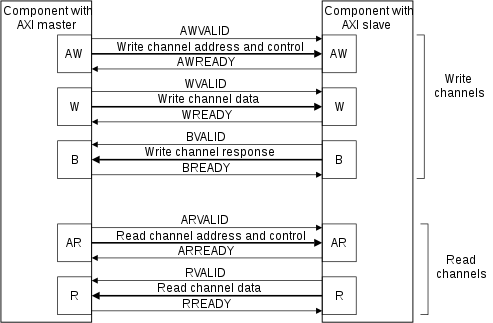

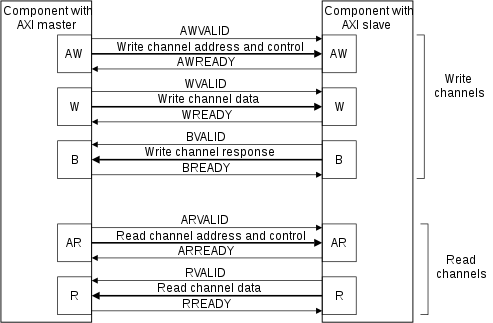

One AXI port if formed of five separate interfaces that are called channels: two for read, three for write.

Each of the five has its own contra-directional READY/VALID pair with all other nets running in the VALID direction and qualified by the conjunction of ready and valid on a clock edge.

In simple applications, the address and data channels for write will run close to lockstep, making a more natural total of four logical interfaces.

Sequential consistency: the complete decoupling of the read and write aspects immediately raises the prospect of RaW and WaR hazards.

AXI can be used with and without (AXI-lite) ordering tokens/tags.

AXI is widely used even for non-ARM products »ARM AXI

| 75: (C) 2008-17, DJ Greaves, University of Cambridge, Computer Laboratory. |