Used, for instance, where one CPU has placed a message in a shared memory region for another to read. Sometimes the interrupter is part of a central interrupt distributor, such as the `GIC' from ARM, that enables any device interrupt to be routed to any core with any priority.

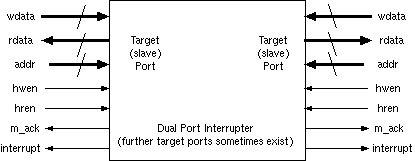

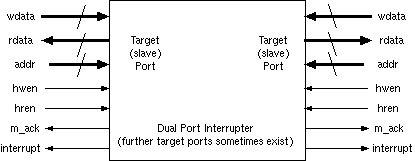

It offers multiple target interfaces, one per client bus.

It generates interrupts to one core at the request of another.

Operational sequence: one core writes a register that asserts an interrupt wire to another core.

The interrupted core, in its service routine, reads or writes a register in the interrupter to clear the interrupt.

Mailbox variant allows small data items to be written to a queue in the interrupter. These are read out by the (or any) core that is (or wants to) handle the interrupt. Link: »Doorbell Driver Fragments.

| 45: (C) 2008-17, DJ Greaves, University of Cambridge, Computer Laboratory. |