A clock-domain-crossing bridge is needed between clock domains.

The basic techniques are the same whether implemented as part of an asynchronous FIFO, a SoC bus bridge or inside an IP block (e.g. network receive front end to network core logic).

The same techniques apply when receiving asynchronous signals into a clock domain.

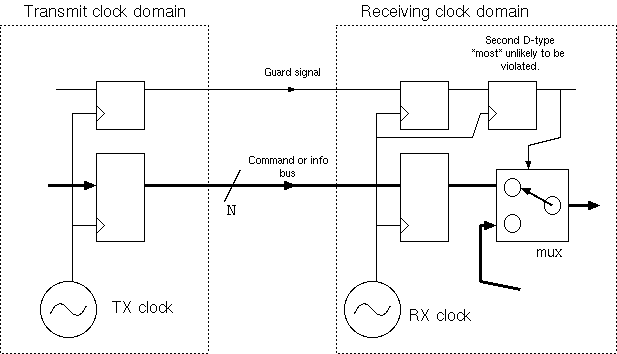

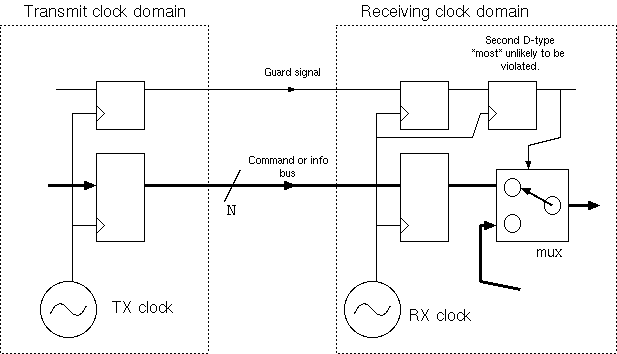

The following figure illustrates the key design aspects for crossing in one direction, but generally these details will be wrapped up into a carefully-design library block like the domain-crossing FIFO shown elsewhere.

Design principle:

| Receiver side RTL: input clk; // receiving domain clock input [31..0] data; input req; output reg ack; |

100 percent utilisation impossible.

| 50: (C) 2008-17, DJ Greaves, University of Cambridge, Computer Laboratory. |