(Not examinable for part II).

Can we consider higher-dimensional interconnect ?

The hypercube has lowest diameter for number of customers. But it has excessive wiring.

Chips are two-dimensional so perhaps it's good to use a 2-D network ? But this may be overly conservative.

Maybe use 2.5-D ? have a small number of `multi-hop' links?

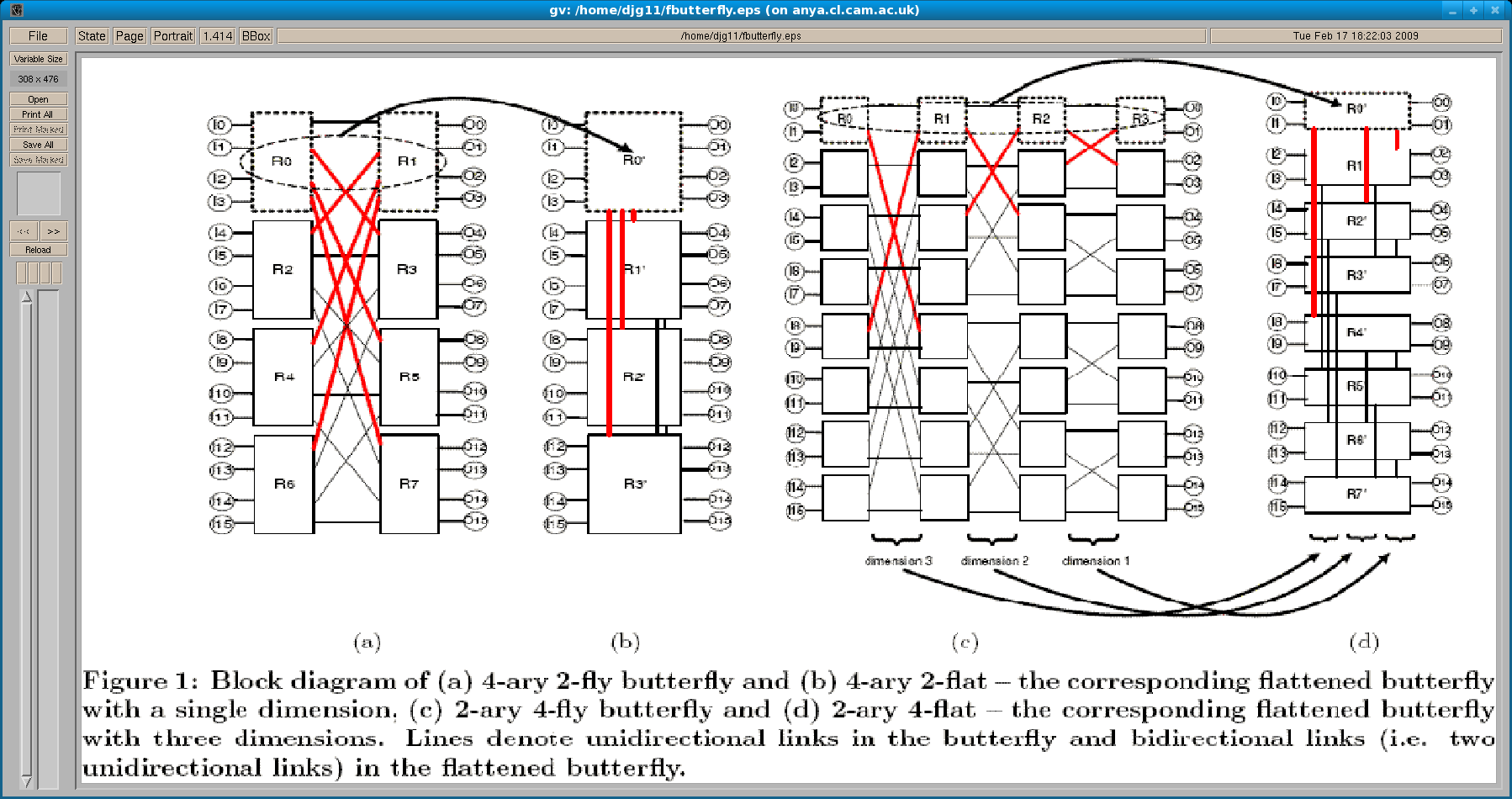

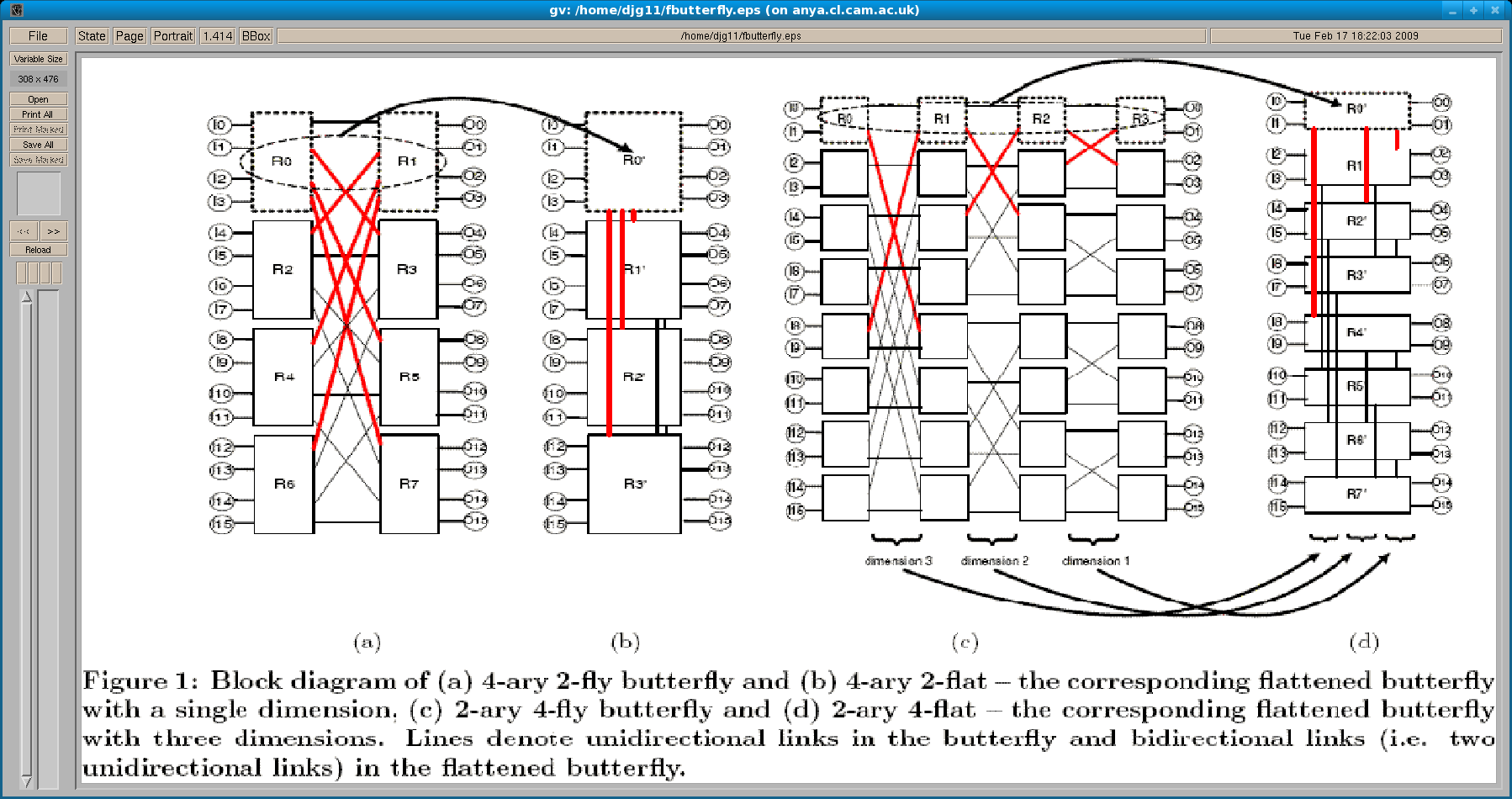

On benign (load-balanced) traffic, the flattened butterfly approaches the cost/performance of a butterfly network and has roughly half the cost of a comparable performance clos network.

Further details (non examinable): "The advantage over the clos is achieved by eliminating redundant hops when they are not needed for load balance." See `Flattened butterfly : a cost-efficient topology for high-radix networks' by John Kim, William J. Dally, Dennis Abts.

Typical NoC designs use credit-based flow control where counters remotely track the amount of receive buffer space available at the destination. The destination could be next hop in a store-and-forward design but could also be a virtual circuit. Cut-through routers using virtual circuits

| 80: (C) 2008-17, DJ Greaves, University of Cambridge, Computer Laboratory. |