This slide non-examinable for part II CST 2015/16.

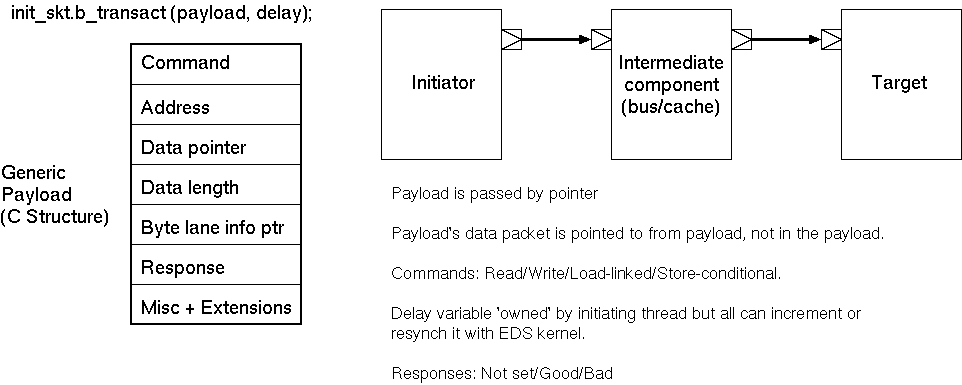

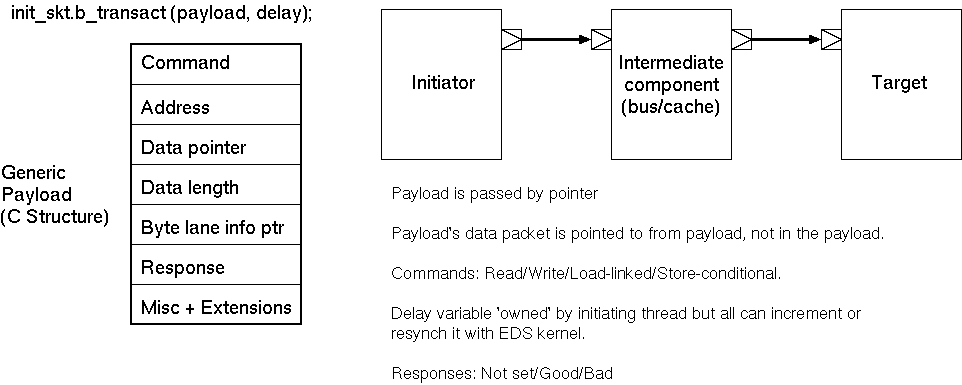

Rather than having application-specific method names, we standardise on a generic bus operation and demultiplex within various IP blocks based on regsiter address.

The generic payload can be extended on a a custom basis and intermediate bus bridges and routers can be polymorphic about this: not needing to know about all the extensions but able to update timestamps to model routing delays.

It also defines memory/garbage ownership and transport primitives with timing. Finally, it provides a raft of useful features, such as automatic conversion between blocking and non-blocking styles.

However, TLM 2.0 it is a bit too complex to get a deep understanding of in the time available for the Part II course, hence the motivation for the 'Toy ESL' practicals in TLM 1.0 style.

| 24: (C) 2008-16, DJ Greaves, University of Cambridge, Computer Laboratory. |