HOME

UP

PREV

NEXT (Detailed Delay Model.)

Chip Dissipation

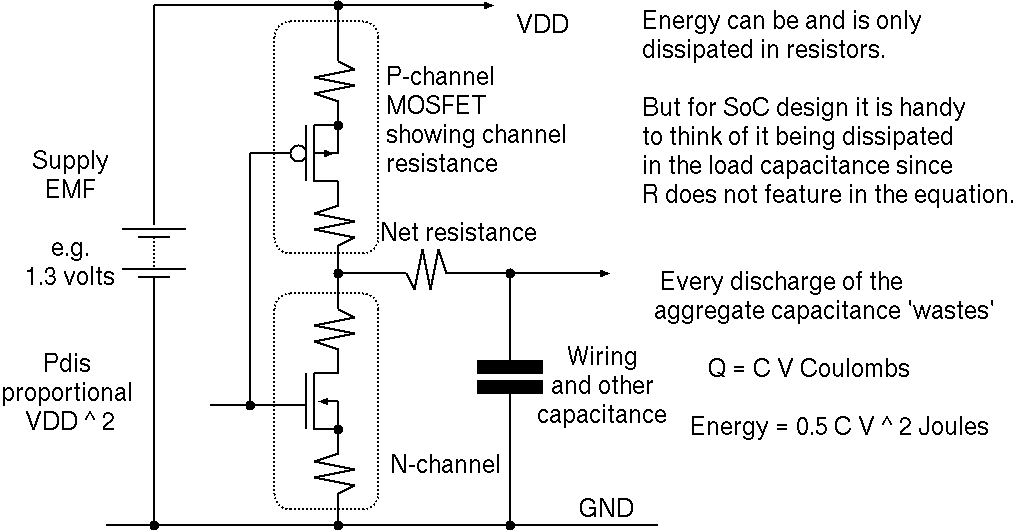

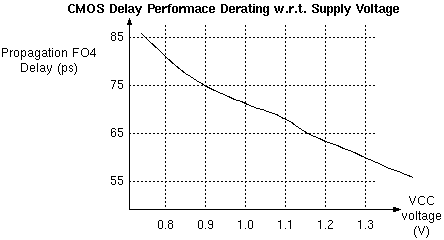

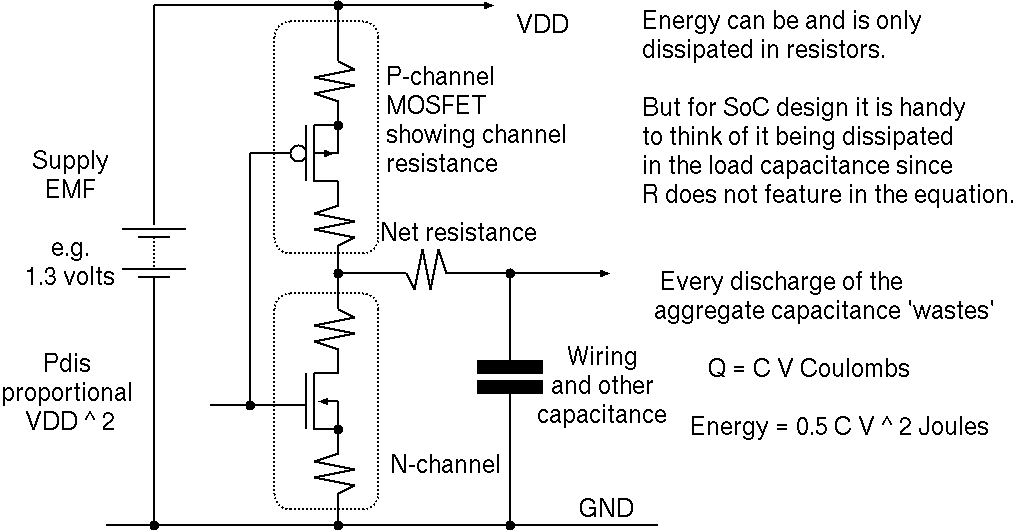

Capacitors do not consume energy - they only store it temporarily.

Only resistors dissipate energy in logic circuits, but their resistance

does not feature in the energy use formula. The energy in the wiring

capacitance is `wasted' on each logic one to zero transistion.

Capacitors do not consume energy - they only store it temporarily.

Only resistors dissipate energy in logic circuits, but their resistance

does not feature in the energy use formula. The energy in the wiring

capacitance is `wasted' on each logic one to zero transistion.

If the clock frequency is f and a net has activity ratio \alpha (the fraction of clock cycles it transitions from one to zero) then the energy used is

Energy = f * alpha * C * V^2 / 2

|

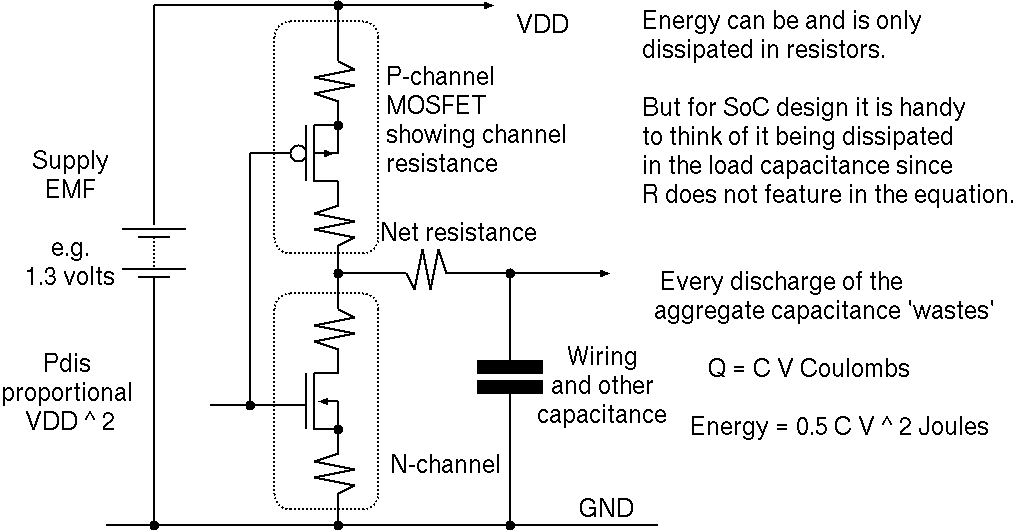

The FO4 delay is the delay through an inverter that is feeding four other nearby inverters (fan out of four).

|

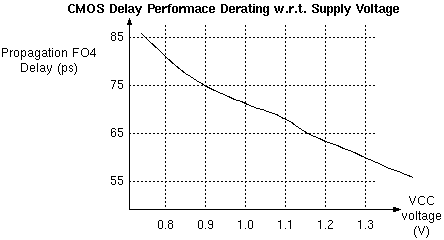

Transistors have a gate threshold voltage around which they switch from off to on. This limits our lowest possible

supply voltage. Above this, logic delay in CMOS is roughly inversely proportional to supply voltage. Accordingly, to operate faster,

we need a higher supply voltage for a given load capacitance.

»CMOS Delay Versus Supply Voltage

Delay = ( beta * C * V ) / ( (V-Vt) ^ 2)