Legacy RTL's (Verilog and VHDL) do not provide synthesis of handshake circuits (but its one of the main innovations in Bluespec).

We'll use the word transactional for interfaces that support flow-control and can span between clock domains (one side may even be asynchronous).

If tools are allowed to retime components, all interfaces between components must be transactional.

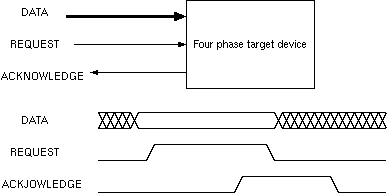

Here is some behavioural (non-RTL) code that embodies the above protocol:

putbyte(char d)

{

wait_until(!ack);

data = d;

settle();

req = 1;

wait_until(ack);

req = 0;

}

| char getbyte()

{

wait_until(req);

char r = data;

ack = 1;

wait_until(!req);

ack = 0;

return r;

}

|