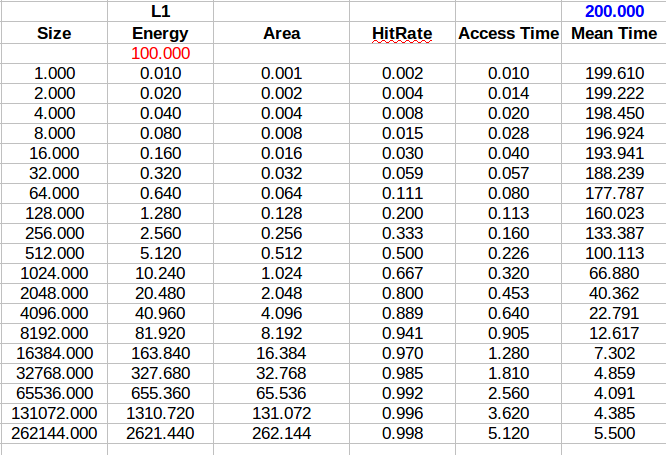

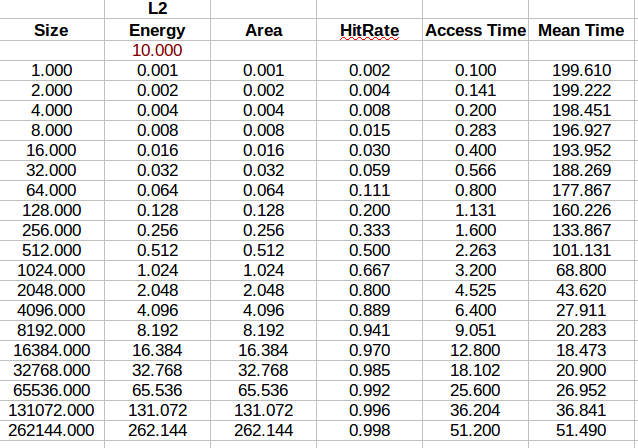

According to wiring structure, associativity, wire length, supply voltage, transistor doping and size and so on, a cache using a given silicon area can be small in capacity and fast in response time or larger in capacity and smaller in response. Here we first show two points in a fictional design space, called L1 and L2. These differ by 10 to 1 in access time and area.

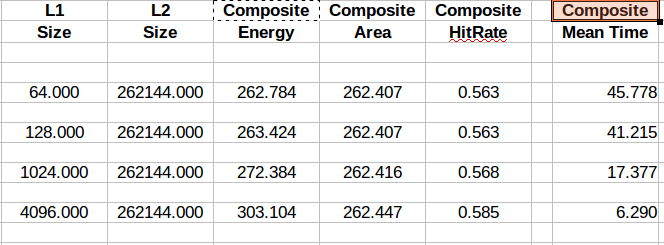

Now we can consider making a two-level cache that uses an L1 backed up by an L2. The aggregate performance for four different combinations is reported.

If we combine a high speed L1 with a low power L2 we can build a large cache with quite good average access time at an energy level far below using just L1 technology alone. Not shown here, but we could also explore a higher-density L2 technology that uses smaller transistors.

Note: the figures in the spreadsheet have arbitrary units but the base technology equations have the correct-shaped trends and their means of combing is correct.

| 16: (C) 2012-16, DJ Greaves, University of Cambridge, Computer Laboratory. |