# Multicore Semantics: Making Sense of Relaxed Memory

Peter Sewell<sup>1</sup>, Christopher Pulte<sup>1</sup>, Shaked Flur<sup>1,2</sup>

with contributions from Mark Batty<sup>3</sup>, Luc Maranget<sup>4</sup>, Alasdair Armstrong<sup>1</sup>

<sup>1</sup> University of Cambridge, <sup>2</sup> Google, <sup>3</sup> University of Kent, <sup>4</sup> INRIA Paris

February – March, 2025

Slides for Part 2 of the Multicore Semantics and Programming course, version of 2026-02-12

Part 1 is by Tim Harris, with separate slides

# These Slides

These are the slides for the Multicore Semantics part of the University of Cambridge *Multicore Semantics and Programming* course (MPhil ACS, Part III, Part II), 2024–2025.

They cover multicore semantics: the concurrency of multiprocessors and programming languages, focussing on the concurrency behaviour one can rely on from mainstream machines and languages, how this can be investigated, and how it can be specified precisely, all linked to usage, microarchitecture, experiment, and proof.

We focus largely on x86; on Arm-A, IBM POWER, and RISC-V; and on C/C++. We use the x86 part also to introduce some of the basic phenomena and the approaches to modelling and testing, and give operational and axiomatic models in detail. For Armv8-A, POWER, and RISC-V we introduce many but not all of the phenomena and again give operational and axiomatic models, but omitting some aspects. For C/C++11 we introduce the programming-language concurrency design space, including the thin-air problem, the C/C++11 constructs, and the basics of its axiomatic model, but omit full explanation of the model.

These lectures are by Peter Sewell, with Christopher Pulte for the Armv8/RISC-V model section. The slides are for around 10 hours of lectures, and include additional material for reference.

The other part of the course, by Tim Harris, covers concurrent programming: simple algorithms, correctness criteria, advanced synchronisation patterns, transactional memory.

# These Slides

The slides include citations to some of the most directly relevant related work, but this is primarily a lecture course focussed on understanding the concurrency semantics of mainstream architectures and languages as we currently see them, for those that want to program above or otherwise use those models, not a comprehensive literature review. There is lots of other relevant research that we do not discuss.

# Acknowledgements

Contributors to these slides: Shaked Flur, Christopher Pulte, Mark Batty, Luc Maranget, Alasdair Armstrong. Ori Lahav and Viktor Vafeiadis for discussion of the current models for C/C++. Paul Durbaba for his 2021 Part III dissertation mechanising the x86-TSO axiomatic/operational correspondence proof.

Our main industry collaborators: Derek Williams (IBM); Richard Grisenthwaite and Will Deacon (Arm); Hans Boehm, Paul McKenney, and other members of the C++ concurrency group; Daniel Lustig and other members of the RISC-V concurrency group

All the co-authors of the directly underlying research [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15] [16, ?, 17, ?, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29], especially all the above, Susmit Sarkar, Jade Alglave, Scott Owens, Kathryn E. Gray, Jean Pichon-Pharabod, and Francesco Zappa Nardelli, and the authors of the language-level research cited later.

The students of this and previous versions of the course, from 2010–2011 to date.

Research funding: ERC Advanced Grant 789108 (ELVER, Sewell); EPSRC grants EP/K008528/1 (Programme Grant REMS: Rigorous Engineering for Mainstream Systems), EP/F036345 (Reasoning with Relaxed Memory Models), EP/H005633 (Leadership Fellowship, Sewell), and EP/H027351 (Postdoc Research Fellowship, Sarkar); the Scottish Funding Council (SICSA Early Career Industry Fellowship, Sarkar); an ARM iCASE award (Pulte); ANR grant WMC (ANR-11-JS02-011, Zappa Nardelli, Maranget); EPSRC IAA KTF funding; Arm donation funding; IBM donation funding; ANR project ParSec (ANR-06-SETIN-010); and INRIA associated team MM. This work is part of the CIFV project sponsored by the Defense Advanced Research Projects Agency (DARPA) and the Air Force Research Laboratory (AFRL), under contract FA8650-18-C-7809. The views, opinions, and/or findings contained in this paper are those of the authors and should not be interpreted as representing the official views or policies, either expressed or implied, of the Department of Defense or the U.S. Government.

|                                           |            |                                             |     |

|-------------------------------------------|------------|---------------------------------------------|-----|

| <b>1. Introduction</b>                    | <b>2</b>   | 5.1.6 Further thread-local subtleties       |     |

| <b>2. Memory</b>                          | <b>6</b>   | 5.1.7 Further Power non-MCA subtleties      |     |

| 2.1 Multiprocessors                       | 9          | 5.2 More features                           | 319 |

| 2.2 Sequential consistency                | 14         | 5.2.1 Armv8-A release/acquire accesses      |     |

| 2.3 Architecture specification            | 26         | 5.2.2 Load-linked/store-conditional (LL/SC) |     |

| 2.4 Litmus tests and candidate executions | 34         | 5.2.3 Atomics                               |     |

| 2.5 Why?                                  | 35         | 5.2.4 Mixed-size                            |     |

| <b>3. x86</b>                             | <b>36</b>  | 5.3 ISA semantics                           | 337 |

| 3.1 x86 basic phenomena                   | 37         | 5.3.1 Integrating ISA and axiomatic models  |     |

| 3.2 Creating a usable model               | 87         | 5.4 Armv8-A/RISC-V operational model        | 346 |

| 3.3 x86-TSO operational model             | 99         | 5.5 Armv8-A/RISC-V axiomatic model          | 396 |

| 3.4 x86-TSO spinlock example and TRF      | 139        | 5.6 Validation                              | 405 |

| 3.5 Axiomatic models                      | 185        | <b>6. Programming language concurrency</b>  | 408 |

| 3.6 x86-TSO axiomatic model               | 206        | 6.1 Introduction                            | 409 |

| <b>4. Validating models</b>               | <b>232</b> | 6.2 Java                                    | 432 |

| <b>5. Arm-A, IBM Power, and RISC-V</b>    | <b>254</b> | 6.3 C/C++11                                 | 436 |

| 5.1 Phenomena                             | 263        | 6.3.1 C/C++11 models and tooling            |     |

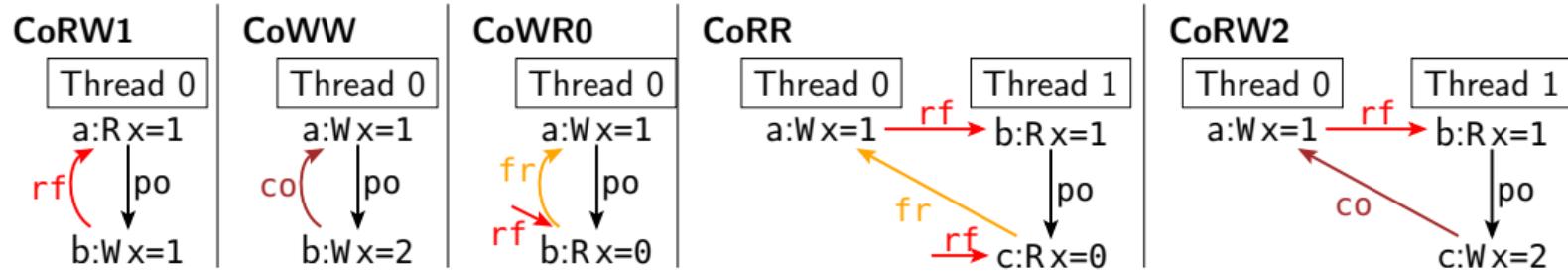

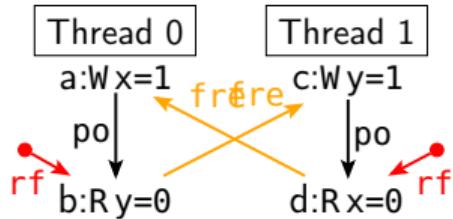

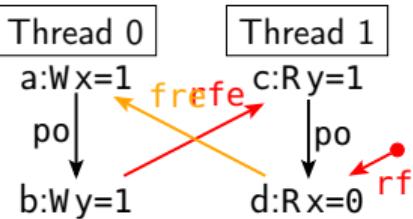

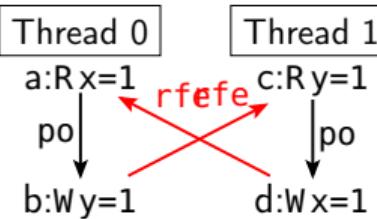

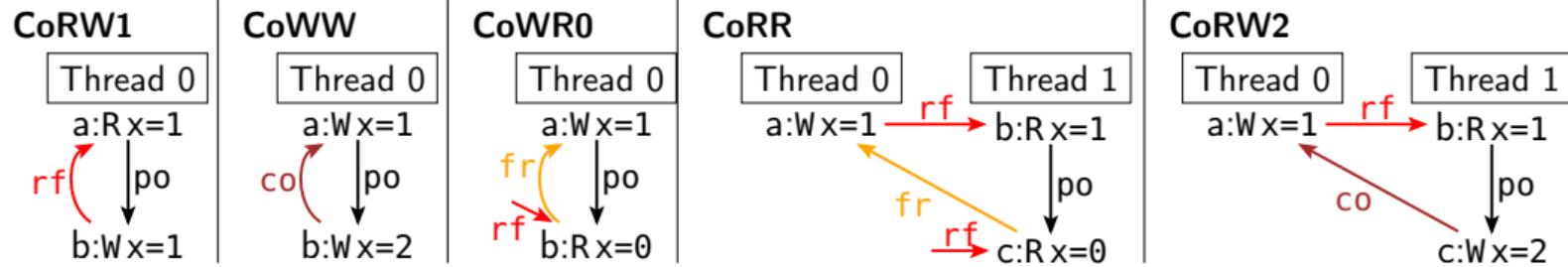

| 5.1.1 Coherence                           |            | 6.3.2 Mappings from C/C++11 to hardware     |     |

| 5.1.2 Out-of-order accesses               |            | 6.4 The thin-air problem                    | 505 |

| 5.1.3 Barriers                            |            | 6.5 Other languages                         | 511 |

| 5.1.4 Dependencies                        |            | <b>7. Conclusion</b>                        | 517 |

| 5.1.5 Multi-copy atomicity                |            | References                                  | 526 |

# Memory

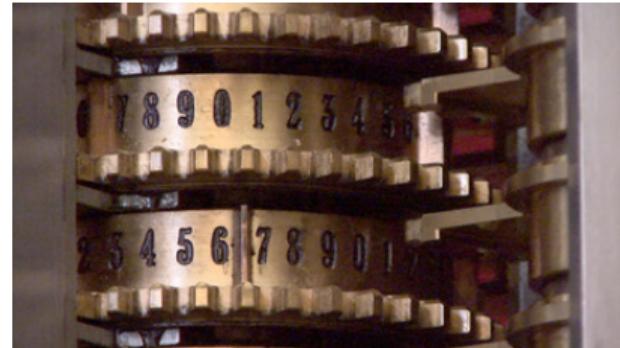

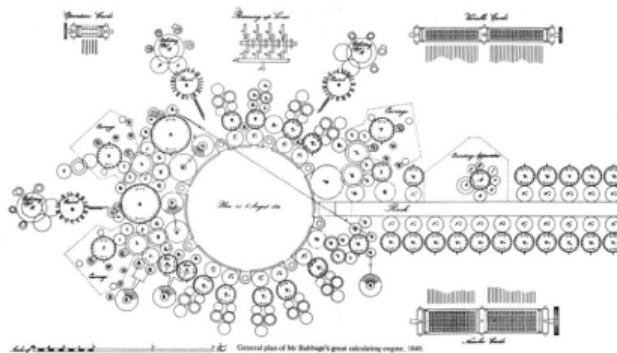

The abstraction of a *memory* goes back some time...

## Memory

*The calculating part of the engine may be divided into two portions*

### 1st *The Mill in which all operations are performed*

**2nd** *The Store in which all the numbers are originally placed and to which the numbers computed by the engine are returned.*

[Dec 1837, *On the Mathematical Powers of the Calculating Engine*, Charles Babbage]

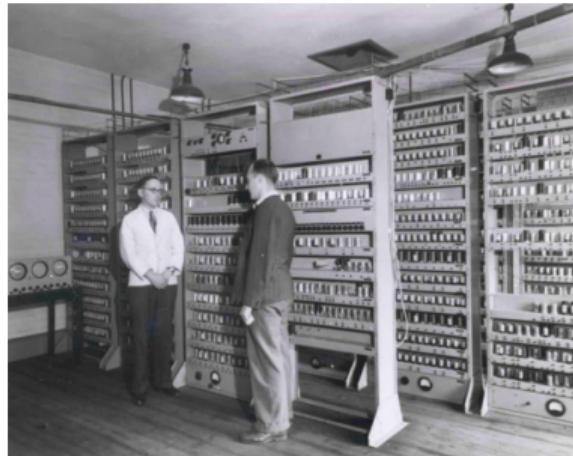

# The Golden Age, (1837–) 1945–1962

# 1962: First(?) Multiprocessor

BURROUGHS D825, 1962

"Outstanding features include truly modular hardware with parallel processing throughout"

FUTURE PLANS The complement of compiling languages is to be expanded."

# Multiprocessors, 1962–now

Niche multiprocessors since 1962

IBM System 370/158MP in 1972

Mass-market since 2005 (Intel Core 2 Duo).

# Multiprocessors, 2019

Intel Xeon E7-8895 v3

36 hardware threads

**ARM**® Commonly 8 hardware threads.

IBM Power 8 server

(up to 1536 hardware threads)

## Why now?

Exponential increases in transistor counts continued — but not per-core performance

- ▶ energy efficiency (computation per Watt)

- ▶ limits of instruction-level parallelism

Concurrency finally mainstream — but how to understand, design, and program concurrent systems? Still very hard.

# Concurrency everywhere

At many scales:

- ▶ intra-core

- ▶ multicore processors ← our focus

- ▶ ...and programming languages ← our focus

- ▶ GPU

- ▶ datacenter-scale

- ▶ internet-scale

explicit message-passing vs shared memory abstractions

# The most obvious semantics: Sequential Consistency

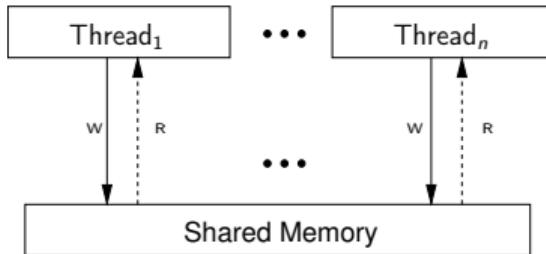

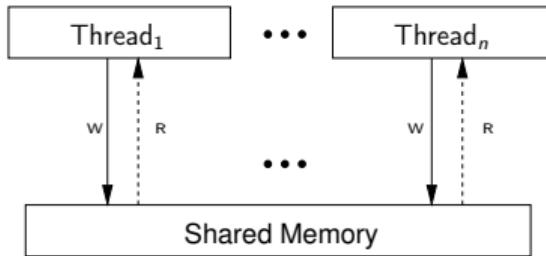

Multiple threads acting on a *sequentially consistent* (SC) shared memory:

the result of any execution is the same as if the operations of all the processors

were executed in some sequential order, respecting the order specified by the

program

[Lamport, 1979]

## A naive two-thread mutual-exclusion algorithm

Initial state:  $x=0$ ;  $y=0$ ;

| Thread 0                                                 | Thread 1                                                 |

|----------------------------------------------------------|----------------------------------------------------------|

| $x=1$ ;<br><b>if</b> ( $y==0$ ) {...critical section...} | $y=1$ ;<br><b>if</b> ( $x==0$ ) {...critical section...} |

Can both be in their critical sections at the same time, in SC?

## A naive two-thread mutual-exclusion algorithm

| Initial state: $x=0$ ; $y=0$ ; |                   |

|--------------------------------|-------------------|

| Thread 0                       | Thread 1          |

| $x=1$ ;<br>$r0=y$              | $y=1$ ;<br>$r1=x$ |

Is a final state with  $r0=0$  and  $r1=0$  possible in SC?

## A naive two-thread mutual-exclusion algorithm

| Initial state: $x=0$ ; $y=0$ ; |                    |

|--------------------------------|--------------------|

| Thread 0                       | Thread 1           |

| $x=1$ ;<br>$r_0=y$             | $y=1$ ;<br>$r_1=x$ |

Is a final state with  $r_0=0$  and  $r_1=0$  possible in SC?

Try all six interleavings of SC model:

Let's try...

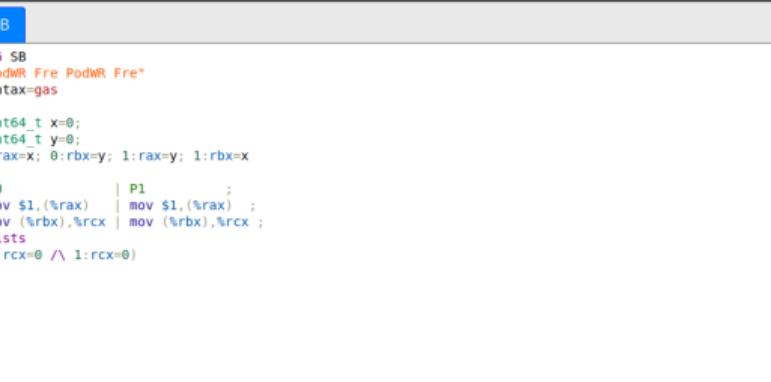

We'll use the `litmus7` tool ([diy.inria.fr](http://diy.inria.fr), Alglave, Maranget, et al. [27])

Write the test in litmus format, in a file `SB.litmus`:

```

1 X86_64 SB

2 "PodWR Fre PodWR Fre"

3 Cycle=Fre PodWR Fre PodWR

4 Relax=

5 Safe=Fre PodWR

6 Generator=diy7 (version 7.55+01(dev))

7 Prefetch=0:x=F,0:y=T,1:y=F,1:x=T

8 Com=Fr Fr

9 Orig=PodWR Fre PodWR Fre

10 Align=

11 {

12     uint64_t y; uint64_t x; uint64_t 1:rax; uint64_t 0:rax;

13

14 }

15 P0 | P1 ;

```

Contents 2.2 Memory: Sequential consistency

Let's try...

To install `litmus7`:

1. install the opam package manager for OCaml: <https://opam.ocaml.org/>

2. `opam install herdtools7` (docs at [diy.inria.fr](https://diy.inria.fr))

Let's try...

```

[...]

Generated assembler

#START _litmus_P1

movq $1,(%r9,%rcx)

movq (%r8,%rcx),%rax

#START _litmus_P0

movq $1,(%r8,%rcx)

movq (%r9,%rcx),%rax

[...]

```

Let's try...

```

$ litmus7 SB.litmus

[...]

Histogram (4 states)

14    *>0:rax=0; 1:rax=0;

499983:>0:rax=1; 1:rax=0;

499949:>0:rax=0; 1:rax=1;

54    :>0:rax=1; 1:rax=1;

[...]

Observation SB Sometimes 14 999986

[...]

```

14 in 1e6, on an Intel Core i7-7500U

(beware: 1e6 is a small number; rare behaviours might need 1e9+, and litmus tuning)

Let's try...

```

Histogram (4 states)

7136481  *> 0:X2=0; 1:X2=0;

596513783:> 0:X2=0; 1:X2=1;

596513170:> 0:X2=1; 1:X2=0;

36566      :> 0:X2=1; 1:X2=1;

[...]

Observation SB Sometimes 7136481 1193063519

```

7e6 in 1.2e9, on an Apple-designed ARMv8-A SoC (Apple A10 Fusion) in an iPhone 7

Let's try...

Why could that be?

1. error in the test

2. error in the litmus7-generated test harness

3. error in the OS

4. error in the hardware processor design

5. manufacturing defect in the particular silicon we're running on

6. error in our calculation of what the SC model allows

7. error in the model

Let's try...

Why could that be?

1. error in the test

2. error in the litmus7-generated test harness

3. error in the OS

4. error in the hardware processor design

5. manufacturing defect in the particular silicon we're running on

6. error in our calculation of what the SC model allows

7. error in the model ← this time

**Sequential Consistency is not a correct model for x86 or Arm processors.**

Let's try...

Why could that be?

1. error in the test

2. error in the litmus7-generated test harness

3. error in the OS

4. error in the hardware processor design

5. manufacturing defect in the particular silicon we're running on

6. error in our calculation of what the SC model allows

7. error in the model ← this time

**Sequential Consistency is not a correct model for x86 or Arm processors.**

...or for IBM Power, RISC-V, C, C++, Java, etc.

Instead, all these have some form of *relaxed memory model* (or *weak memory model*), allowing some non-SC behaviour

# What does it mean to be a good model?

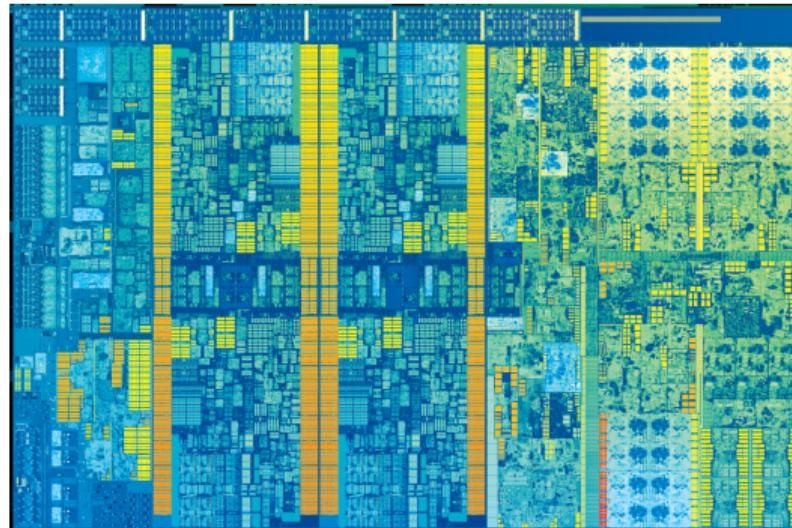

## Processor implementations

Intel i7-8700K, AMD Ryzen 7 1800X, Qualcomm Snapdragon 865, Samsung Exynos 990, IBM Power 9 Nimbus, ...

Each has fantastically complex internal structure:

[Die shot of quad-core Intel i7-7700K (Kaby Lake) processor, [en.wikichip.org](https://en.wikichip.org)]

## Processor implementations

We can't use that as our *programmer's model* – it's:

- ▶ too complex

- ▶ too confidential

- ▶ too *specific*:

software should run correctly on a wide range of hardware implementations,

current and future

## Architecture specifications

An *architecture specification* aims to define an envelope of the *programmer-observable behaviour* of all members of a processor family:

the set of all behaviour that a programmer might see by executing multithreaded programs on any implementation of that family.

The hardware/software interface, serving both as the

1. criterion for correctness of hardware implementations, and the

2. specification of what programmers can depend on.

## Architecture specifications

Thick books:

- ▶ Intel 64 and IA-32 Architectures Software Developer's Manual [30], 5052 pages

- ▶ AMD64 Architecture Programmer's Manual [31], 3165 pages

- ▶ Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile [32], 8248 pages

- ▶ Power ISA Version 3.0B [33], 1258 pages

- ▶ The RISC-V Instruction Set Manual Volume I: Unprivileged ISA [34] and Volume II: Privileged Architecture [35], 238+135 pages

# Architecture specifications

Thick books:

- ▶ Intel 64 and IA-32 Architectures Software Developer's Manual [30], 5052 pages

- ▶ AMD64 Architecture Programmer's Manual [31], 3165 pages

- ▶ Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile [32], 8248 pages

- ▶ Power ISA Version 3.0B [33], 1258 pages

- ▶ The RISC-V Instruction Set Manual Volume I: Unprivileged ISA [34] and Volume II: Privileged Architecture [35], 238+135 pages

Each aims to define the:

- ▶ *architected state* (programmer-visible registers etc.)

- ▶ *instruction-set architecture* (ISA): instruction encodings and sequential behaviour

- ▶ *concurrency architecture* – how those interact

- ▶ ...

## Architecture specifications

Architectures have to be *loose* specifications:

- ▶ accommodating the range of behaviour from runtime nondeterminism of a single implementation (e.g. from timing variations, cache pressure, ...)

- ▶ ...and from multiple implementations, with different microarchitecture

## Desirable properties of an architecture specification

1. Sound with respect to current hardware

2. Sound with respect to future hardware

3. Opaque with respect to hardware microarchitecture implementation detail

4. Complete with respect to hardware?

5. Strong enough for software

6. Unambiguous / precise

7. Executable as a test oracle

8. Incrementally executable

9. Clear

10. Authoritative?

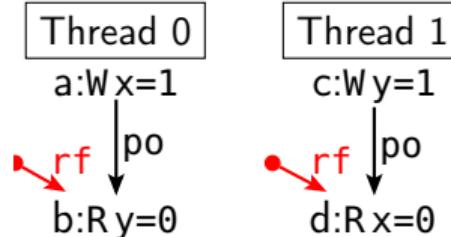

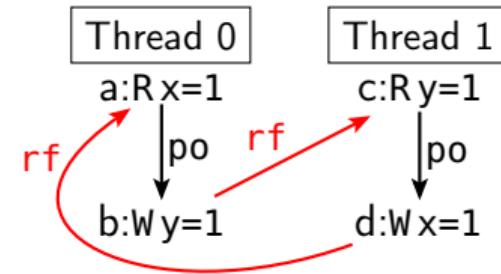

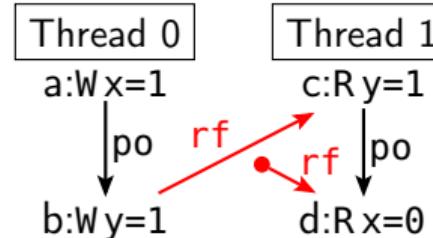

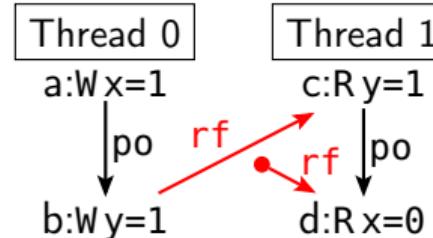

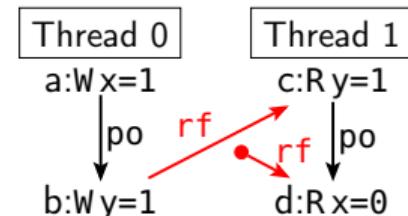

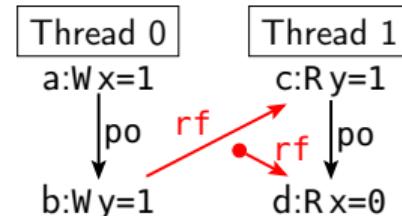

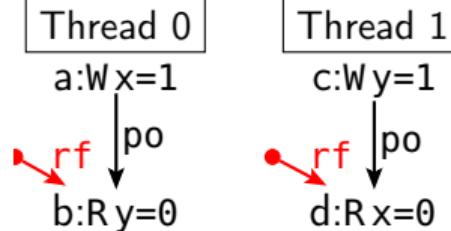

## Litmus tests and candidate executions

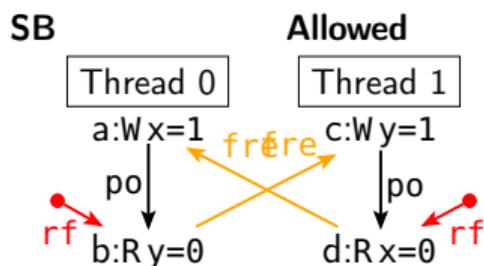

SB

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0                 | Thread 1           |

|--------------------------|--------------------|

| movq \$1, (x) //a        | movq \$1, (y) //c  |

| movq (y), %rax //b       | movq (x), %rax //d |

| Final: 0:rax=0; 1:rax=0; |                    |

Observation: 171/1000000000

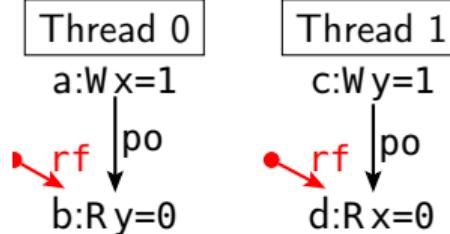

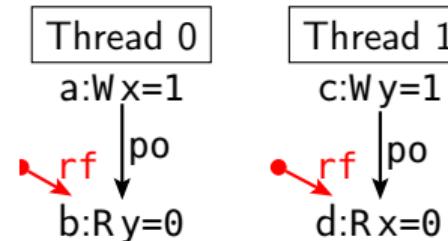

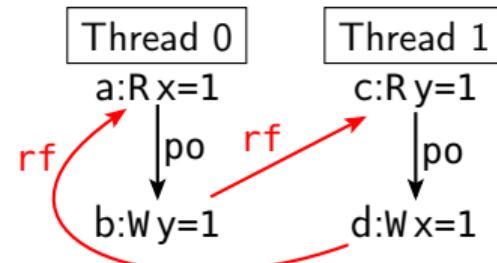

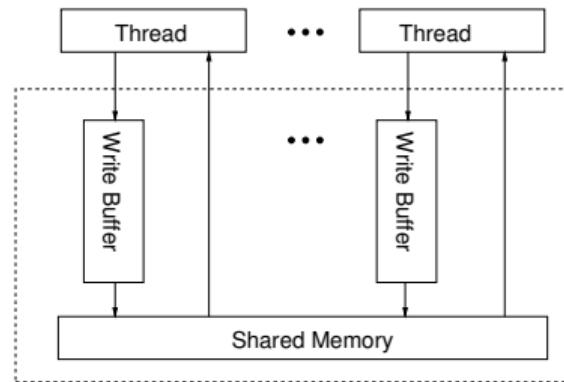

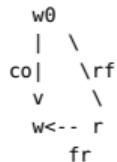

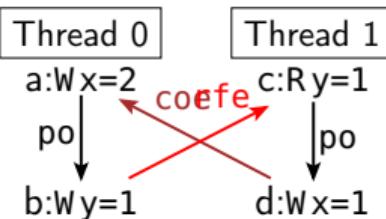

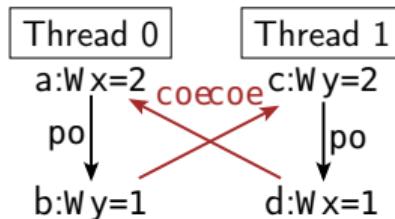

*Candidate executions* consist of:

- ▶ a choice of a control-flow unfolding of the test source

- ▶ a choice, for each memory read, of which write it reads from, or the initial state

- ▶ ...more later

Represented as graphs, with nodes the memory events and various relations, including:

- ▶ *program order* po

- ▶ *reads-from* rf

The final-state condition of the test often identifies a unique candidate execution

...which might be observable or not on h/w, and allowed or not by a model.

## Why is this an academic subject?

Why not just read the manuals?

Those desirable properties turn out to be very hard to achieve, esp. for subtle real-world concurrency

In 2007, many architecture prose texts were too vague to interpret reliably

Research from then to date has clarified much, and several architectures now incorporate precise models based on it (historical survey later)

...and this enables many kinds of research above these models

Much still to do!

x86

# x86 basic phenomena

**Observable relaxed-memory behaviour arises from hardware optimisations

(and compiler optimisations for language-level relaxed behaviour)**

**Observable relaxed-memory behaviour arises from hardware optimisations

(and compiler optimisations for language-level relaxed behaviour)**

so we should be able to understand and explain them in those terms

## Scope: “user” concurrency

Focus for now on the behaviour of memory accesses and barriers, as used in most concurrent algorithms (in user or system modes, but without systems features).

Coherent write-back memory, assuming:

- ▶ no misaligned or mixed-size accesses

- ▶ no exceptions

- ▶ no self-modifying code

- ▶ no page-table changes

- ▶ no ‘non-temporal’ operations

- ▶ no device memory

Most of those are active research areas. We also ignore fairness properties, considering finite executions only

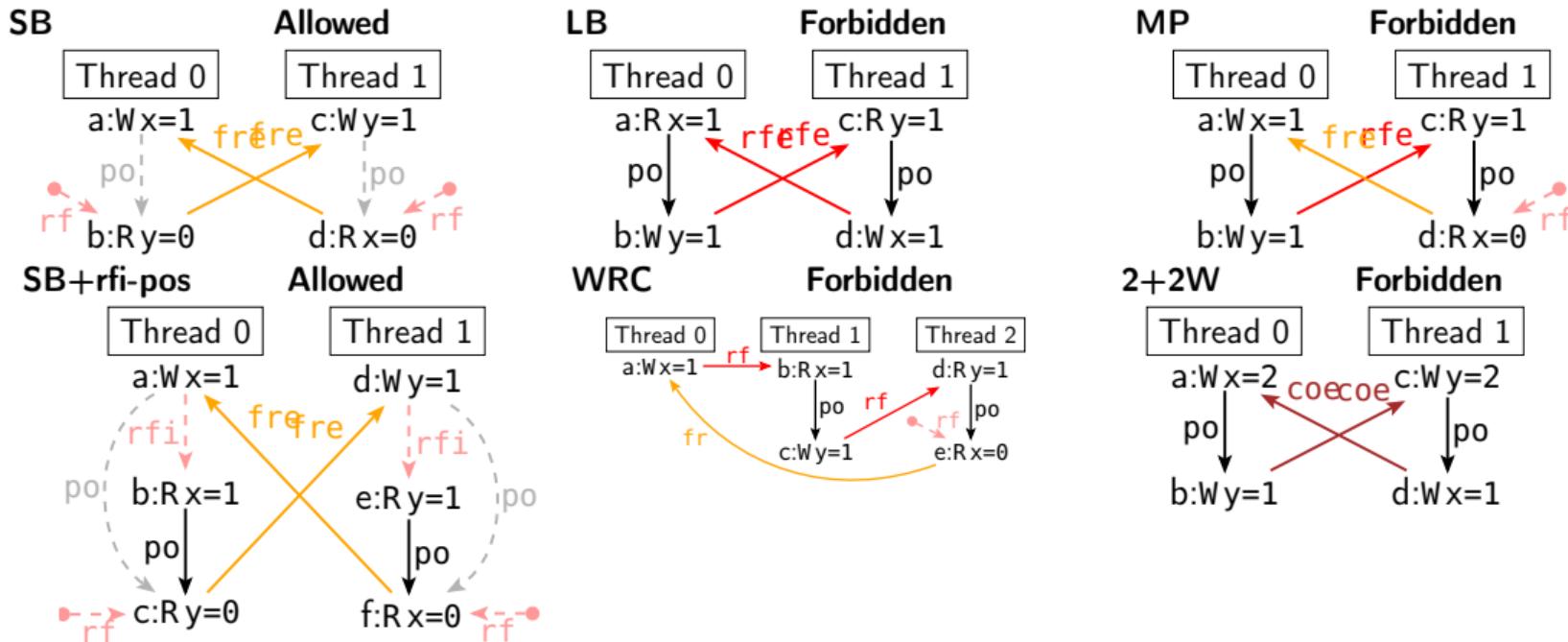

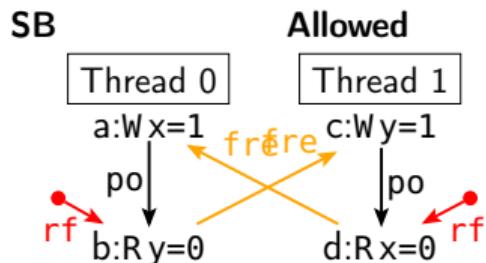

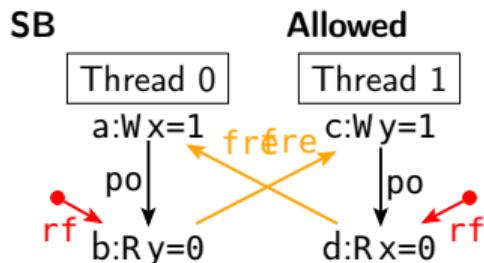

SB

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //c  |

| movq (y), %rax //b | movq (x), %rax //d |

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //c  |

| movq (y), %rax //b | movq (x), %rax //d |

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

- ▶ experimentally: observed

x86

SB

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //c  |

| movq (y), %rax //b | movq (x), %rax //d |

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

- ▶ experimentally: observed

- ▶ possible microarchitectural explanation?

SB

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0                    | Thread 1           |

|-----------------------------|--------------------|

| movq \$1, (x) //a           | movq \$1, (y) //c  |

| movq (y), %rax //b          | movq (x), %rax //d |

| Final: 0:rax=0; 1:rax=0;    |                    |

| Observation: 171/1000000000 |                    |

- ▶ experimentally: observed

- ▶ possible microarchitectural explanation?

buffer stores? out-of-order execution?

SB

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //c  |

| movq (y), %rax //b | movq (x), %rax //d |

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

- ▶ experimentally: observed

- ▶ possible microarchitectural explanation?

buffer stores? out-of-order execution?

- ▶ architecture prose and intent?

*Reads may be reordered with older writes to different locations but not with older writes to the same location. [Intel SDM,§8.2.2, and Example 8-3]*

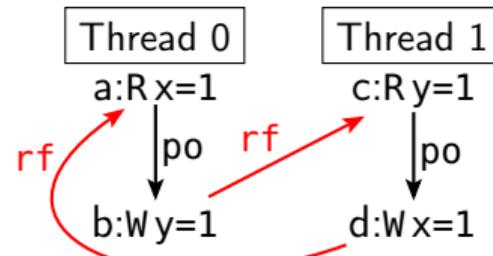

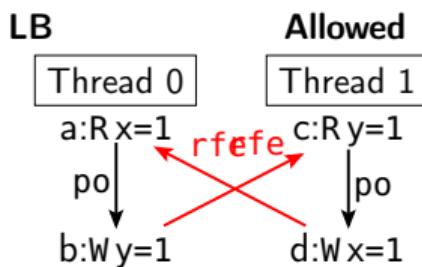

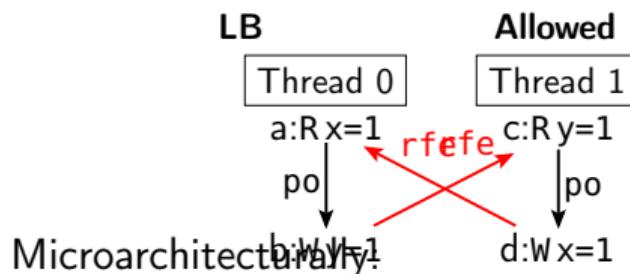

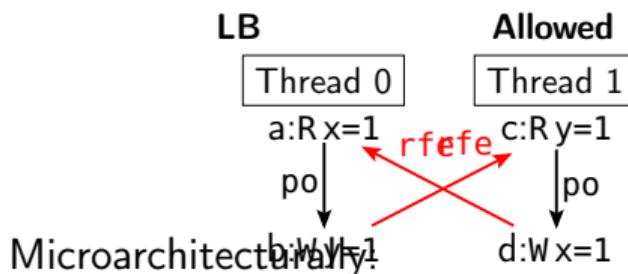

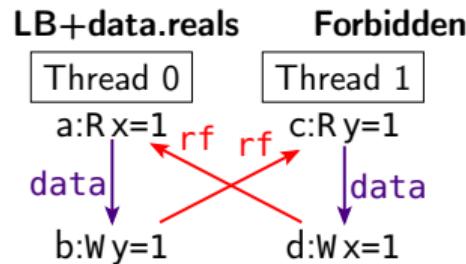

LB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq (x), %rax //a | movq (y), %rax //c |

| movq \$1, (y) //b  | movq \$1, (x) //d  |

Final: 0:rax=1; 1:rax=1;

Observation: 0/0

x86

LB

| x86                                        |                                         |

|--------------------------------------------|-----------------------------------------|

| Initial state: 0:rax=0; 1:rax=0; y=0; x=0; |                                         |

| Thread 0                                   | Thread 1                                |

| movq (x), %rax //a<br>movq \$1, (y) //b    | movq (y), %rax //c<br>movq \$1, (x) //d |

| Final: 0:rax=1; 1:rax=1;                   |                                         |

Observation: 0/0

- ▶ experimentally: not observed

LB

| x86                                        |                                         |

|--------------------------------------------|-----------------------------------------|

| Initial state: 0:rax=0; 1:rax=0; y=0; x=0; |                                         |

| Thread 0                                   | Thread 1                                |

| movq (x), %rax //a<br>movq \$1, (y) //b    | movq (y), %rax //c<br>movq \$1, (x) //d |

| Final: 0:rax=1; 1:rax=1;                   |                                         |

Observation: 0/0

- ▶ experimentally: not observed

- ▶ possible microarchitectural explanation?

LB

| x86                                        |                                         |

|--------------------------------------------|-----------------------------------------|

| Initial state: 0:rax=0; 1:rax=0; y=0; x=0; |                                         |

| Thread 0                                   | Thread 1                                |

| movq (x), %rax //a<br>movq \$1, (y) //b    | movq (y), %rax //c<br>movq \$1, (x) //d |

| Final: 0:rax=1; 1:rax=1;                   |                                         |

Observation: 0/0

- ▶ experimentally: not observed

- ▶ possible microarchitectural explanation?

- Buffer load requests?

- Out-of-order execution?

LB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq (x), %rax //a | movq (y), %rax //c |

| movq \$1, (y) //b  | movq \$1, (x) //d  |

Final: 0:rax=1; 1:rax=1;

Observation: 0/0

- ▶ experimentally: not observed

- ▶ possible microarchitectural explanation?

- Buffer load requests?

- Out-of-order execution?

- ▶ architecture prose and intent?

*Reads may be reordered with older writes to different locations but not with older writes to the same location. [Intel SDM,§8.2.2]*

So?

x86

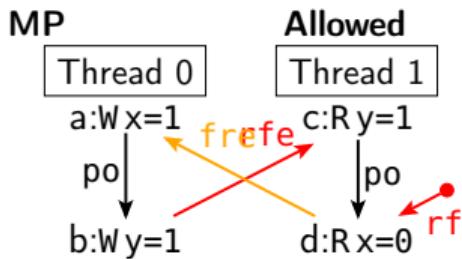

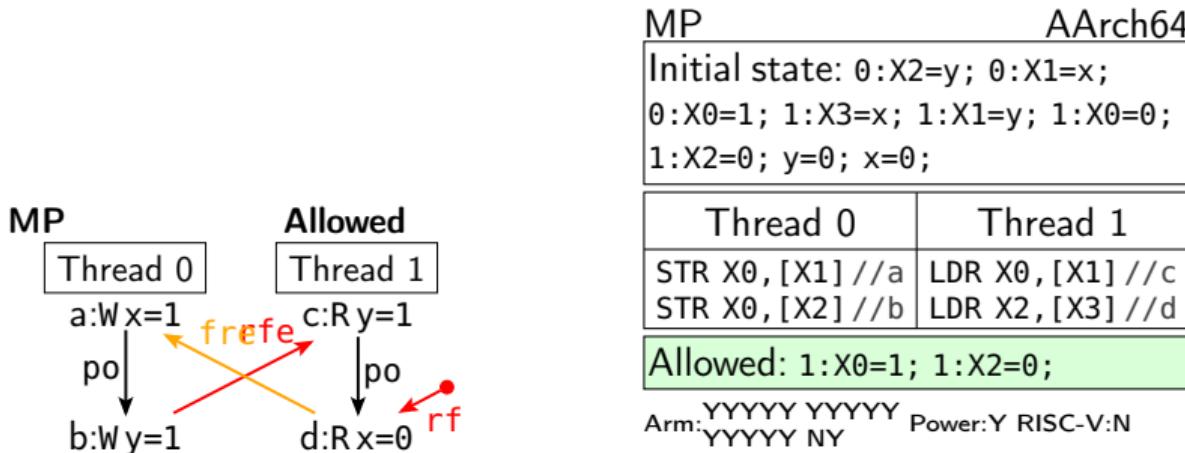

MP

x86

Initial state: 1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0          | Thread 1           |

|-------------------|--------------------|

| movq \$1, (x) //a | movq (y), %rax //c |

| movq \$1, (y) //b | movq (x), %rbx //d |

Final: 1:rax=1; 1:rbx=0;

Observation: 0/1000000000

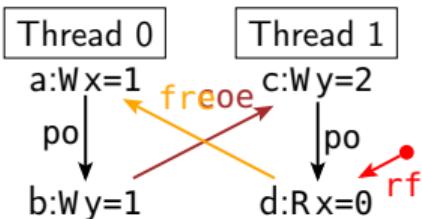

Thread 0

a:W x=1

po

b:W y=1

Thread 1

c:R y=1

po

d:R x=0

rf

rf

|                                            |

|--------------------------------------------|

| Initial state: 1:rax=0; 1:rbx=0; y=0; x=0; |

|--------------------------------------------|

| Thread 0          | Thread 1           |

|-------------------|--------------------|

| movq \$1, (x) //a | movq (y), %rax //c |

| movq \$1, (y) //b | movq (x), %rbx //d |

|                          |

|--------------------------|

| Final: 1:rax=1; 1:rbx=0; |

|--------------------------|

Observation: 0/100000000

- ▶ experimentally: not observed

(but it is on Armv8-A and IBM Power)

|                                            |

|--------------------------------------------|

| Initial state: 1:rax=0; 1:rbx=0; y=0; x=0; |

|--------------------------------------------|

| Thread 0          | Thread 1           |

|-------------------|--------------------|

| movq \$1, (x) //a | movq (y), %rax //c |

| movq \$1, (y) //b | movq (x), %rbx //d |

|                          |

|--------------------------|

| Final: 1:rax=1; 1:rbx=0; |

|--------------------------|

Observation: 0/1000000000

- ▶ experimentally: not observed

(but it is on Armv8-A and IBM Power)

- ▶ possible microarchitectural explanation?

Out-of-order pipeline execution is another important hardware optimisation – but not *programmer-visible* here

Initial state: 1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                       | Thread 1                        |

|--------------------------------|---------------------------------|

| <code>movq \$1, (x) //a</code> | <code>movq (y), %rax //c</code> |

| <code>movq \$1, (y) //b</code> | <code>movq (x), %rbx //d</code> |

Final: 1:rax=1; 1:rbx=0;

Observation: 0/1000000000

- ▶ experimentally: not observed

(but it is on Armv8-A and IBM Power)

- ▶ possible microarchitectural explanation?

Out-of-order pipeline execution is another important hardware optimisation – but not *programmer-visible* here

- ▶ consistent with model sketch?

Initial state: 1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                       | Thread 1                        |

|--------------------------------|---------------------------------|

| <code>movq \$1, (x) //a</code> | <code>movq (y), %rax //c</code> |

| <code>movq \$1, (y) //b</code> | <code>movq (x), %rbx //d</code> |

Final: 1:rax=1; 1:rbx=0;

Observation: 0/1000000000

- ▶ experimentally: not observed

(but it is on Armv8-A and IBM Power)

- ▶ possible microarchitectural explanation?

Out-of-order pipeline execution is another important hardware optimisation – but not *programmer-visible* here

- ▶ consistent with model sketch?

- ▶ architecture prose and intent?

*Reads are not reordered with other reads. Writes to memory are not reordered with other writes, except non-temporal moves and string operations. Example 8-1*

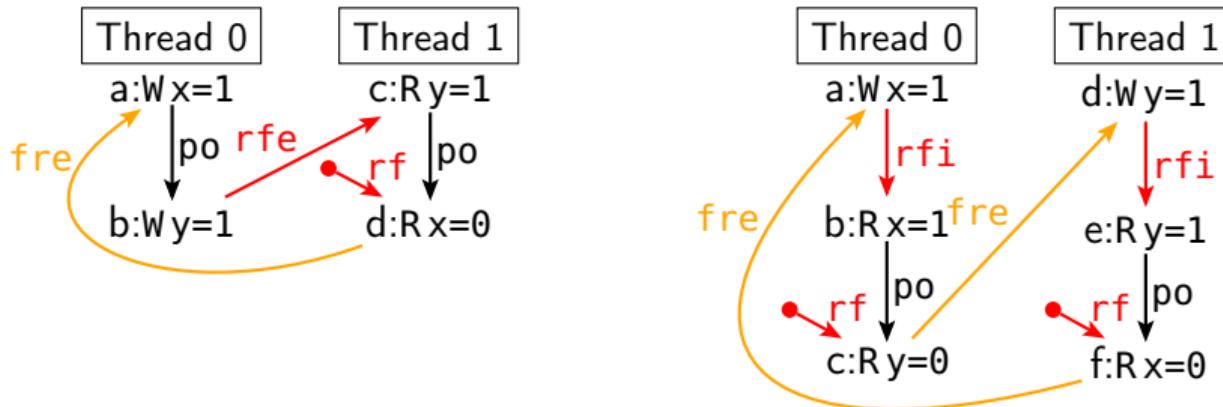

SB+rfi-pos

x86

Initial state: 0:rax=0; 0:rbx=0;

1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                                      | Thread 1           |

|-----------------------------------------------|--------------------|

| movq \$1, (x) //a                             | movq \$1, (y) //d  |

| movq (x), %rax //b                            | movq (y), %rax //e |

| movq (y), %rbx //c                            | movq (x), %rbx //f |

| Final: 0:rax=1; 0:rbx=0; 1:rax=1;<br>1:rbx=0; |                    |

Observation: 320/1000000000

SB+rfi-pos

x86

Initial state: 0:rax=0; 0:rbx=0;

1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                                      | Thread 1           |

|-----------------------------------------------|--------------------|

| movq \$1, (x) //a                             | movq \$1, (y) //d  |

| movq (x), %rax //b                            | movq (y), %rax //e |

| movq (y), %rbx //c                            | movq (x), %rbx //f |

| Final: 0:rax=1; 0:rbx=0; 1:rax=1;<br>1:rbx=0; |                    |

Observation: 320/1000000000

- ▶ is that allowed in the previous model sketch?

## SB+rfi-pos

x86

Initial state: 0:rax=0; 0:rbx=0;

1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                                      | Thread 1           |

|-----------------------------------------------|--------------------|

| movq \$1, (x) //a                             | movq \$1, (y) //d  |

| movq (x), %rax //b                            | movq (y), %rax //e |

| movq (y), %rbx //c                            | movq (x), %rbx //f |

| Final: 0:rax=1; 0:rbx=0; 1:rax=1;<br>1:rbx=0; |                    |

Observation: 320/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the pairs of reads are not reordered – so no

## SB+rfi-pos

x86

Initial state: 0:rax=0; 0:rbx=0;

1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                                      | Thread 1           |

|-----------------------------------------------|--------------------|

| movq \$1, (x) //a                             | movq \$1, (y) //d  |

| movq (x), %rax //b                            | movq (y), %rax //e |

| movq (y), %rbx //c                            | movq (x), %rbx //f |

| Final: 0:rax=1; 0:rbx=0; 1:rax=1;<br>1:rbx=0; |                    |

Observation: 320/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the pairs of reads are not reordered – so no

- ▶ experimentally: observed

## SB+rfi-pos

x86

Initial state: 0:rax=0; 0:rbx=0;

1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                                      | Thread 1           |

|-----------------------------------------------|--------------------|

| movq \$1, (x) //a                             | movq \$1, (y) //d  |

| movq (x), %rax //b                            | movq (y), %rax //e |

| movq (y), %rbx //c                            | movq (x), %rbx //f |

| Final: 0:rax=1; 0:rbx=0; 1:rax=1;<br>1:rbx=0; |                    |

Observation: 320/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the pairs of reads are not reordered – so no

- ▶ experimentally: observed

- ▶ microarchitectural refinement: allow – actually, *require* – reading from the store buffer

SB+rfi-pos

x86

Initial state: 0:rax=0; 0:rbx=0;

1:rax=0; 1:rbx=0; y=0; x=0;

| Thread 0                                      | Thread 1           |

|-----------------------------------------------|--------------------|

| movq \$1, (x) //a                             | movq \$1, (y) //d  |

| movq (x), %rax //b                            | movq (y), %rax //e |

| movq (y), %rbx //c                            | movq (x), %rbx //f |

| Final: 0:rax=1; 0:rbx=0; 1:rax=1;<br>1:rbx=0; |                    |

Observation: 320/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the pairs of reads are not reordered – so no

- ▶ experimentally: observed

- ▶ microarchitectural refinement: allow – actually, *require* – reading from the store buffer

- ▶ architecture prose and intent?

*Principles? But Example 8-5*

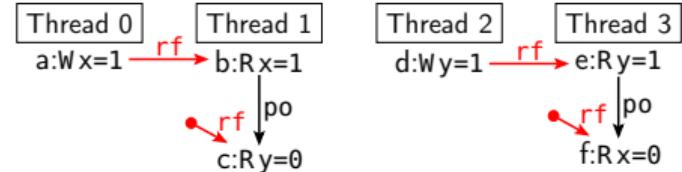

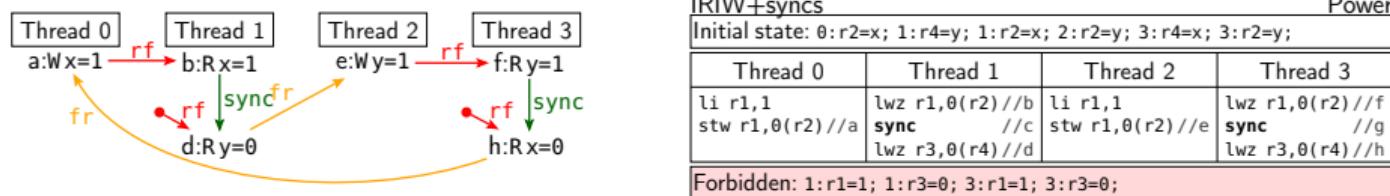

## IRIW

x86

Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0;

| Thread 0                                   | Thread 1                                 | Thread 2          | Thread 3                                 |

|--------------------------------------------|------------------------------------------|-------------------|------------------------------------------|

| movq \$1, (x) //a                          | movq (x), %rax //b<br>movq (y), %rbx //c | movq \$1, (y) //d | movq (y), %rax //e<br>movq (x), %rbx //f |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0; |                                          |                   |                                          |

Observation: 0/1000000000

IRIW

| x86                                                           |                                                               |          |          |

|---------------------------------------------------------------|---------------------------------------------------------------|----------|----------|

| Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0;  |                                                               |          |          |

| Thread 0                                                      | Thread 1                                                      | Thread 2 | Thread 3 |

| movq \$1, (x) //a<br>movq (x), %rax //b<br>movq (y), %rbx //c | movq \$1, (y) //d<br>movq (y), %rax //e<br>movq (x), %rbx //f |          |          |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0;                    |                                                               |          |          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

## IRIW

| x86                                                           |                                          |                                                               |          |

|---------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------|----------|

| Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0;  |                                          |                                                               |          |

| Thread 0                                                      | Thread 1                                 | Thread 2                                                      | Thread 3 |

| movq \$1, (x) //a<br>movq (x), %rax //b<br>movq (y), %rbx //c | movq (x), %rax //b<br>movq (y), %rbx //c | movq \$1, (y) //d<br>movq (y), %rax //e<br>movq (x), %rbx //f |          |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0;                    |                                          |                                                               |          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T2,3 read pairs are not reorderable – so no

## IRIW

| x86                                                           |          |                                                               |          |

|---------------------------------------------------------------|----------|---------------------------------------------------------------|----------|

| Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0;  |          |                                                               |          |

| Thread 0                                                      | Thread 1 | Thread 2                                                      | Thread 3 |

| movq \$1, (x) //a<br>movq (x), %rax //b<br>movq (y), %rbx //c |          | movq \$1, (y) //d<br>movq (y), %rax //e<br>movq (x), %rbx //f |          |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0;                    |          |                                                               |          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T2,3 read pairs are not reorderable – so no

- ▶ is it microarchitecturally plausible?

| x86                                                          |                                          |                   |                                          |

|--------------------------------------------------------------|------------------------------------------|-------------------|------------------------------------------|

| Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0; |                                          |                   |                                          |

| Thread 0                                                     | Thread 1                                 | Thread 2          | Thread 3                                 |

| movq \$1, (x) //a                                            | movq (x), %rax //b<br>movq (y), %rbx //c | movq \$1, (y) //d | movq (y), %rax //e<br>movq (x), %rbx //f |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0;                   |                                          |                   |                                          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T2,3 read pairs are not reorderable – so no

- ▶ is it microarchitecturally plausible? yes, e.g. with shared store buffers or fancy cache protocols

| x86                                                          |                                          |                   |                                          |

|--------------------------------------------------------------|------------------------------------------|-------------------|------------------------------------------|

| Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0; |                                          |                   |                                          |

| Thread 0                                                     | Thread 1                                 | Thread 2          | Thread 3                                 |

| movq \$1, (x) //a                                            | movq (x), %rax //b<br>movq (y), %rbx //c | movq \$1, (y) //d | movq (y), %rax //e<br>movq (x), %rbx //f |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0;                   |                                          |                   |                                          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T2,3 read pairs are not reorderable – so no

- ▶ is it microarchitecturally plausible? yes, e.g. with shared store buffers or fancy cache protocols

- ▶ experimentally: not observed

| x86                                                          |                                          |                   |                                          |

|--------------------------------------------------------------|------------------------------------------|-------------------|------------------------------------------|

| Initial state: 1:rax=0; 1:rbx=0; 3:rax=0; 3:rbx=0; y=0; x=0; |                                          |                   |                                          |

| Thread 0                                                     | Thread 1                                 | Thread 2          | Thread 3                                 |

| movq \$1, (x) //a                                            | movq (x), %rax //b<br>movq (y), %rbx //c | movq \$1, (y) //d | movq (y), %rax //e<br>movq (x), %rbx //f |

| Final: 1:rax=1; 1:rbx=0; 3:rax=1; 3:rbx=0;                   |                                          |                   |                                          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T2,3 read pairs are not reorderable – so no

- ▶ is it microarchitecturally plausible? yes, e.g. with shared store buffers or fancy cache protocols

- ▶ experimentally: not observed

- ▶ architecture prose and intent?

*Any two stores are seen in a consistent order by processors other than those performing the stores;

Example 8-7*

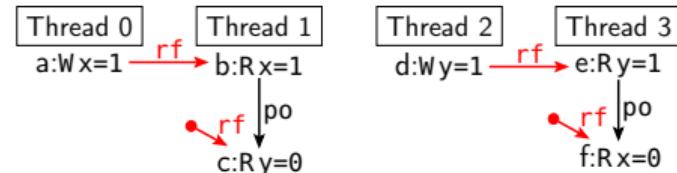

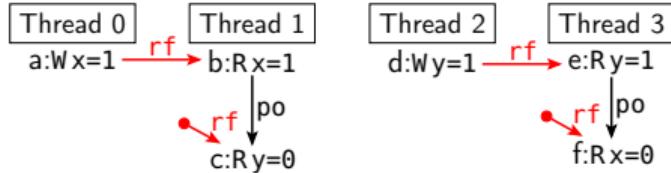

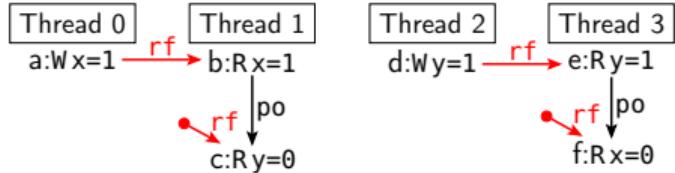

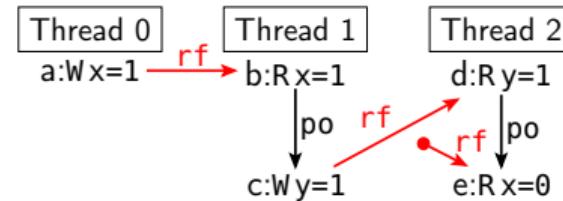

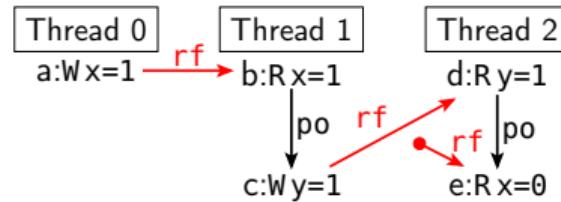

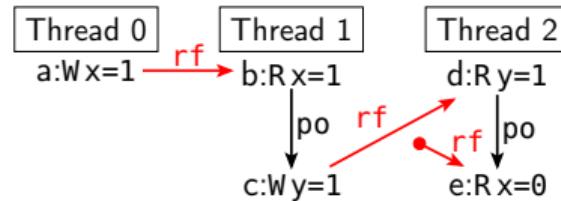

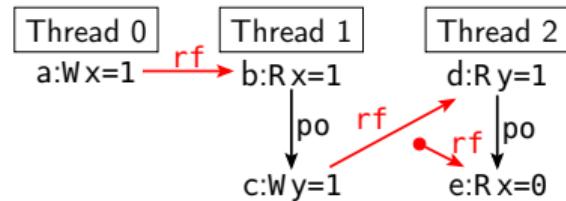

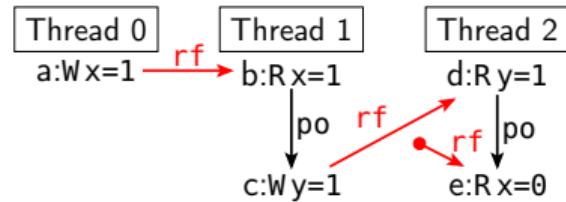

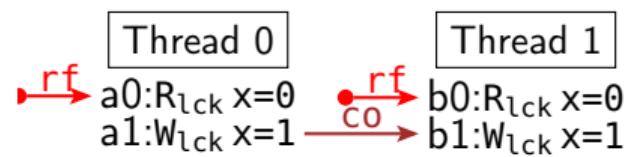

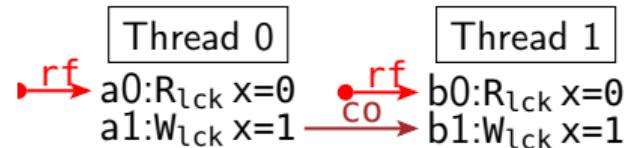

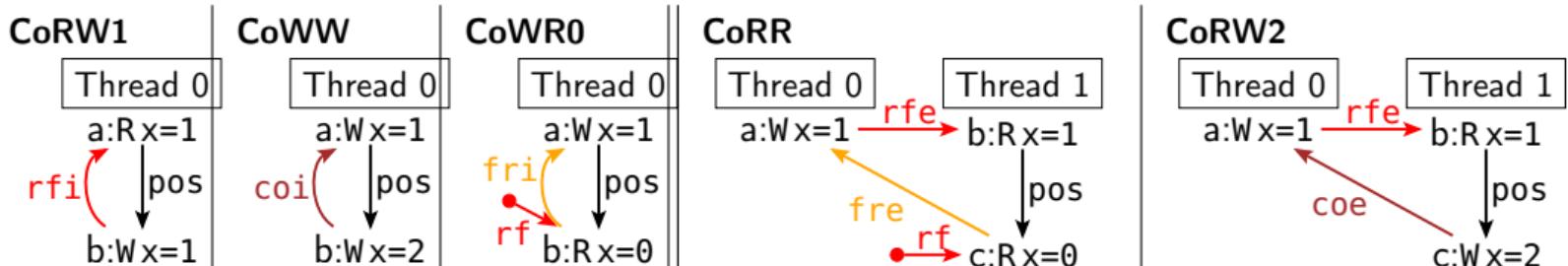

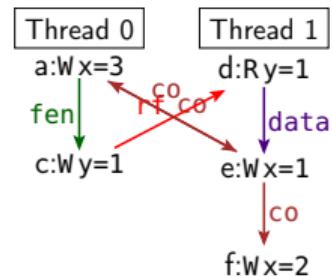

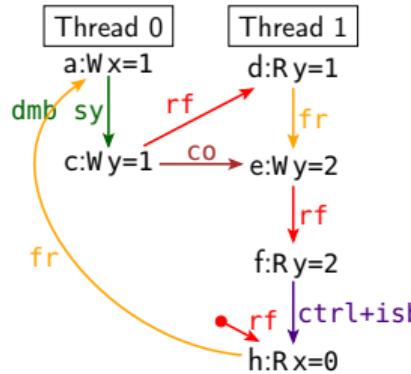

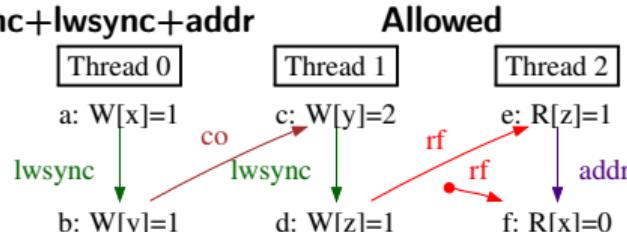

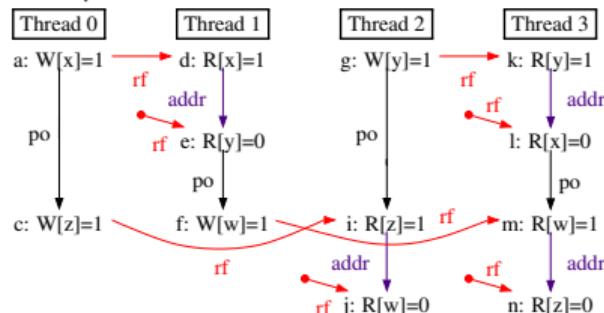

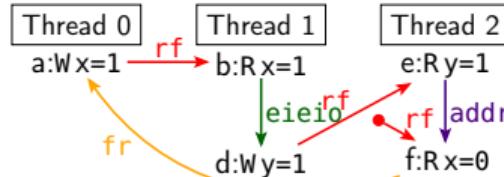

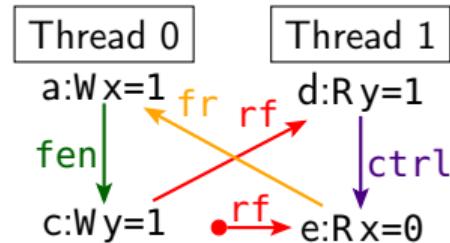

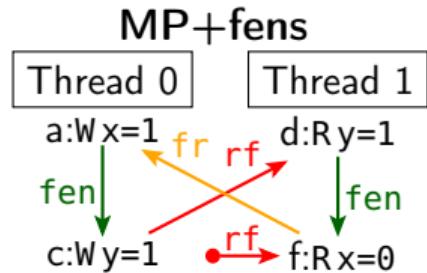

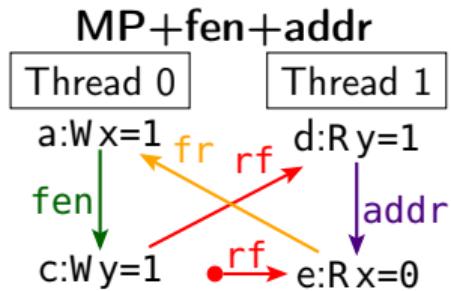

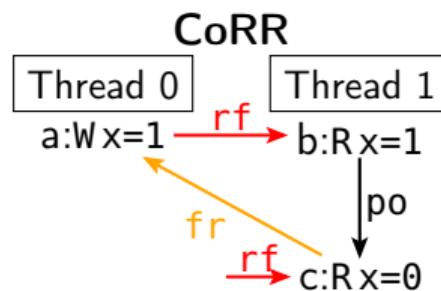

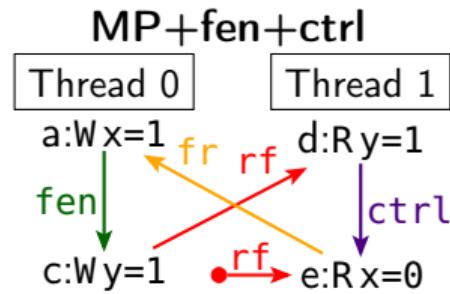

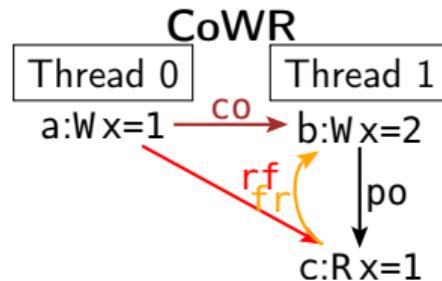

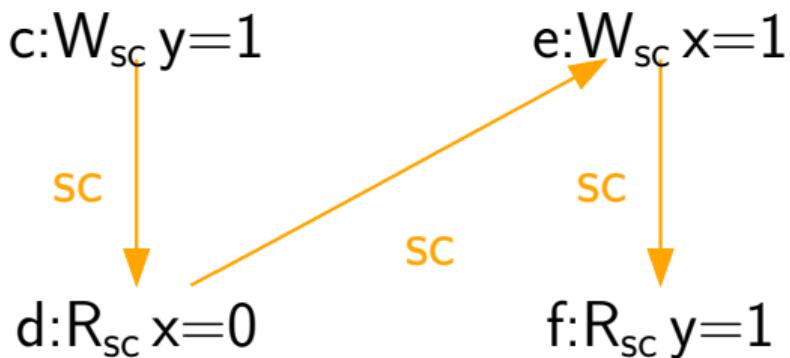

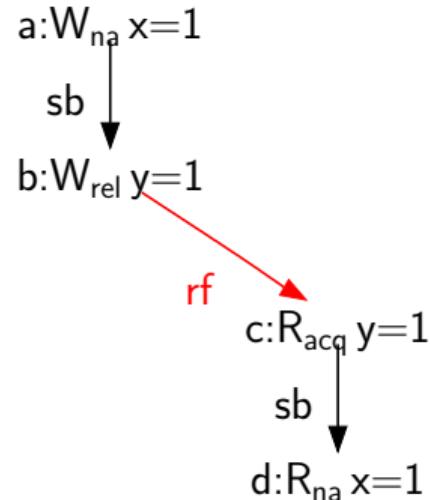

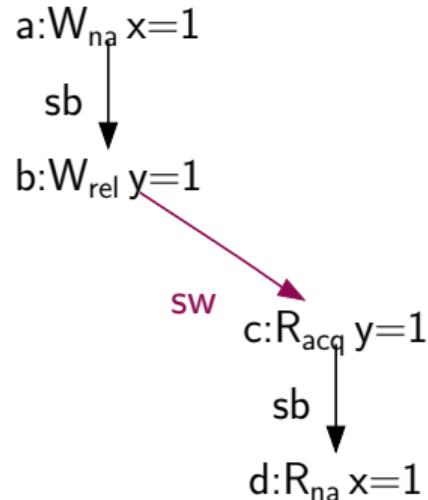

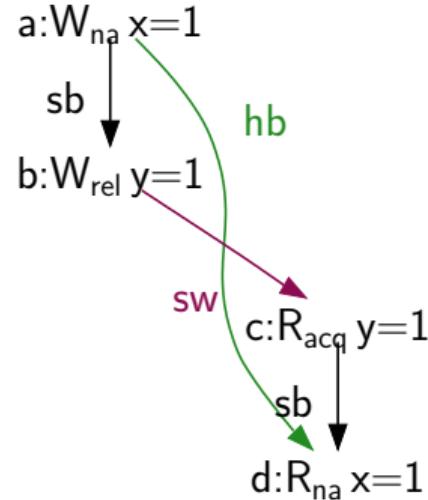

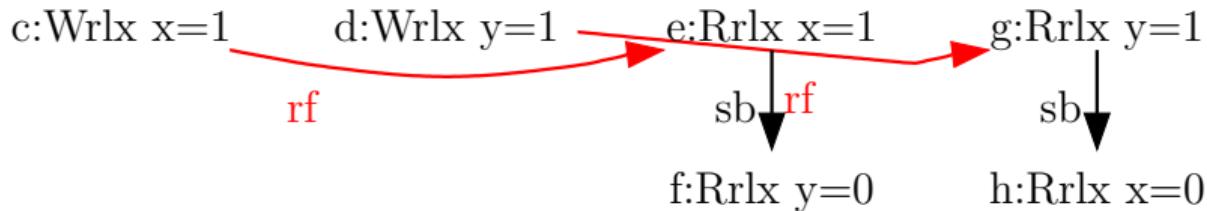

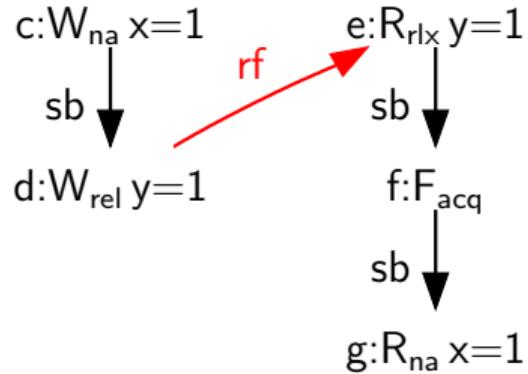

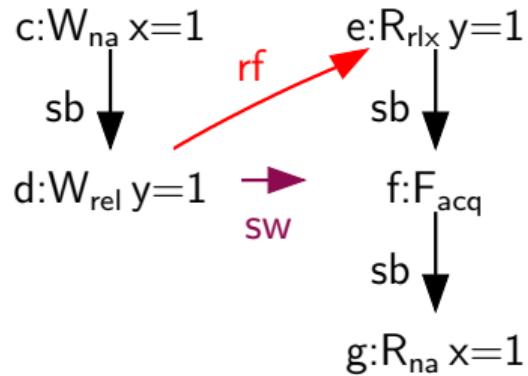

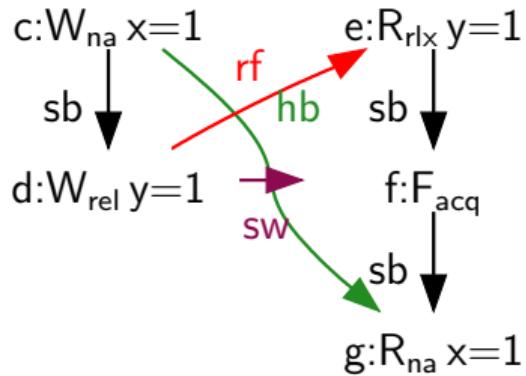

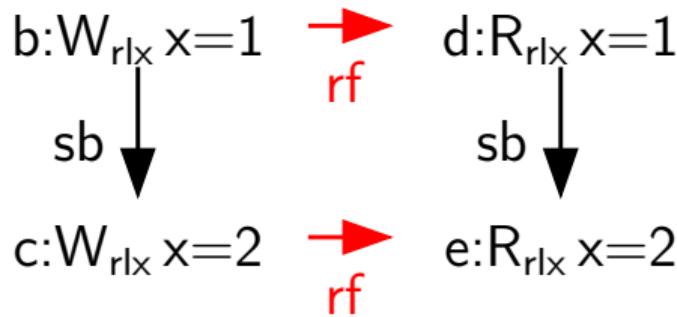

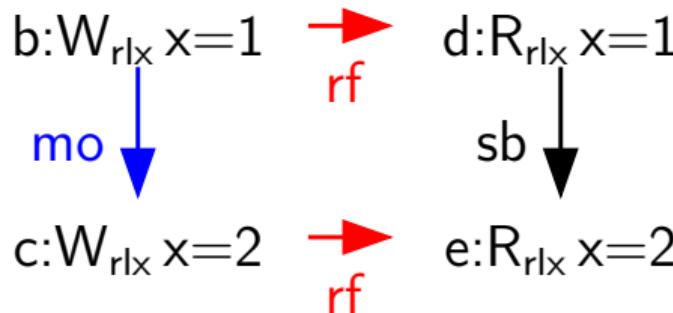

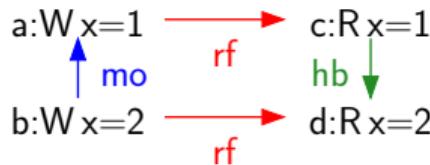

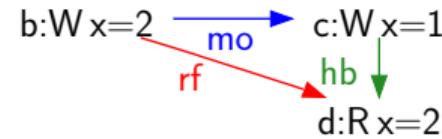

## WRC

| x86                                                 |                                          |                    |

|-----------------------------------------------------|------------------------------------------|--------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0; |                                          |                    |

| Thread 0                                            | Thread 1                                 | Thread 2           |

| movq \$1, (x) //a<br>movq \$1, (y) //c              | movq (x), %rax //b<br>movq (x), %rbx //e | movq (y), %rax //d |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                   |                                          |                    |

Observation: 0/1000000000

## WRC

| x86                                                 |                                          |                    |

|-----------------------------------------------------|------------------------------------------|--------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0; |                                          |                    |

| Thread 0                                            | Thread 1                                 | Thread 2           |

| movq \$1, (x) //a<br>movq \$1, (y) //c              | movq (x), %rax //b<br>movq (x), %rbx //e | movq (y), %rax //d |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                   |                                          |                    |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

## WRC

| x86                                                          |                                          |                                          |

|--------------------------------------------------------------|------------------------------------------|------------------------------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0;          |                                          |                                          |

| Thread 0                                                     | Thread 1                                 | Thread 2                                 |

| movq \$1, (x) //a<br>movq (x), %rax //b<br>movq \$1, (y) //c | movq (x), %rax //b<br>movq (x), %rbx //e | movq (y), %rax //d<br>movq (x), %rbx //e |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                            |                                          |                                          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T1 read-write pair and T2 read pair are not reorderable – so no

## WRC

| x86                                                 |                    |                    |

|-----------------------------------------------------|--------------------|--------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0; |                    |                    |

| Thread 0                                            | Thread 1           | Thread 2           |

| movq \$1, (x) //a                                   | movq (x), %rax //b | movq (y), %rax //d |

| movq \$1, (y) //c                                   |                    | movq (x), %rbx //e |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                   |                    |                    |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T1 read-write pair and T2 read pair are not reorderable – so no or in this one?

## WRC

| x86                                                 |                                 |                                 |

|-----------------------------------------------------|---------------------------------|---------------------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0; |                                 |                                 |

| Thread 0                                            | Thread 1                        | Thread 2                        |

| <code>movq \$1, (x) //a</code>                      | <code>movq (x), %rax //b</code> | <code>movq (y), %rax //d</code> |

|                                                     | <code>movq \$1, (y) //c</code>  | <code>movq (x), %rbx //e</code> |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                   |                                 |                                 |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T1 read-write pair and T2 read pair are not reorderable – so no

- ▶ experimentally: not observed

## WRC

| x86                                                          |                                          |                                          |

|--------------------------------------------------------------|------------------------------------------|------------------------------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0;          |                                          |                                          |

| Thread 0                                                     | Thread 1                                 | Thread 2                                 |

| movq \$1, (x) //a<br>movq (x), %rax //b<br>movq \$1, (y) //c | movq (x), %rax //b<br>movq (x), %rbx //e | movq (y), %rax //d<br>movq (x), %rbx //e |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                            |                                          |                                          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T1 read-write pair and T2 read pair are not reorderable – so no

- ▶ experimentally: not observed

- ▶ architecture prose and intent?

*Memory ordering obeys causality (memory ordering respects transitive visibility). Example 8-5*

## WRC

| x86                                                          |                                          |                                          |

|--------------------------------------------------------------|------------------------------------------|------------------------------------------|

| Initial state: 1:rax=0; 2:rax=0; 2:rbx=0; y=0; x=0;          |                                          |                                          |

| Thread 0                                                     | Thread 1                                 | Thread 2                                 |

| movq \$1, (x) //a<br>movq (x), %rax //b<br>movq \$1, (y) //c | movq (x), %rax //b<br>movq (x), %rbx //e | movq (y), %rax //d<br>movq (x), %rbx //e |

| Final: 1:rax=1; 2:rax=1; 2:rbx=0;                            |                                          |                                          |

Observation: 0/1000000000

- ▶ is that allowed in the previous model sketch?

- ▶ we think the T1 read-write pair and T2 read pair are not reorderable – so no

- ▶ experimentally: not observed

- ▶ architecture prose and intent?

*Memory ordering obeys causality (memory ordering respects transitive visibility). Example 8-5*

- ▶ model sketch remains experimentally plausible, but interpretation of vendor prose unclear

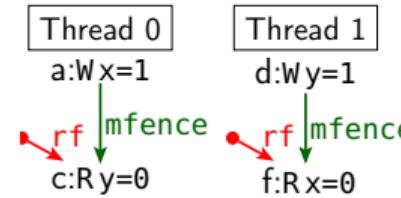

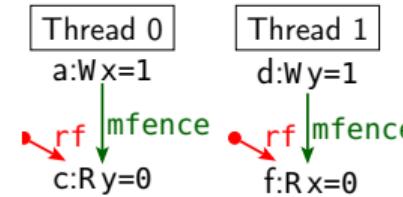

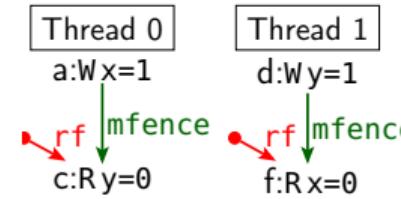

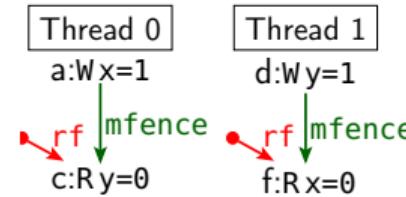

## SB+mfences

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //d  |

| <b>mfence</b> //b  | <b>mfence</b> //e  |

| movq (y), %rax //c | movq (x), %rax //f |

Final: 0:rax=0; 1:rax=0;

Observation: 0/1000000000

## SB+mfences

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //d  |

| <b>mfence</b> //b  | <b>mfence</b> //e  |

| movq (y), %rax //c | movq (x), %rax //f |

Final: 0:rax=0; 1:rax=0;

Observation: 0/1000000000

- ▶ experimentally: not observed

|                                            |

|--------------------------------------------|

| Initial state: 0:rax=0; 1:rax=0; y=0; x=0; |

|--------------------------------------------|

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //d  |

| <b>mfence</b> //b  | <b>mfence</b> //e  |

| movq (y), %rax //c | movq (x), %rax //f |

|                          |

|--------------------------|

| Final: 0:rax=0; 1:rax=0; |

|--------------------------|

Observation: 0/1000000000

- ▶ experimentally: not observed

- ▶ architecture prose and intent?

*Reads and writes cannot pass earlier MFENCE instructions. MFENCE instructions cannot pass earlier reads or writes.*

*MFENCE serializes all store and load operations that occurred prior to the MFENCE instruction in the program instruction stream.*

## SB+mfences

x86

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0           | Thread 1           |

|--------------------|--------------------|

| movq \$1, (x) //a  | movq \$1, (y) //d  |

| <b>mfence</b> //b  | <b>mfence</b> //e  |

| movq (y), %rax //c | movq (x), %rax //f |

Final: 0:rax=0; 1:rax=0;

Observation: 0/1000000000

- ▶ experimentally: not observed

- ▶ architecture prose and intent?

*Reads and writes cannot pass earlier MFENCE instructions. MFENCE instructions cannot pass earlier reads or writes.*

*MFENCE serializes all store and load operations that occurred prior to the MFENCE instruction in the program instruction stream.*

- ▶ in the model sketch: ...waits for local write buffer to drain? (or forces it to – it that observable?)

NB: no inter-thread synchronisation

# Adding Read-Modify-Write instructions

x86 is not RISC – there are many instructions that read and write memory, e.g.

| INC x86                   |                  |

|---------------------------|------------------|

| Initial state: x=0;       |                  |

| Thread 0                  | Thread 1         |

| incq (x) //a0,a1          | incq (x) //b0,b1 |

| Final: x=1;               |                  |

| Observation: 1441/1000000 |                  |

# Adding Read-Modify-Write instructions

x86 is not RISC – there are many instructions that read and write memory, e.g.

| INC x86                   |                  |

|---------------------------|------------------|

| Initial state: x=0;       |                  |

| Thread 0                  | Thread 1         |

| incq (x) //a0,a1          | incq (x) //b0,b1 |

| Final: x=1;               |                  |

| Observation: 1441/1000000 |                  |

Non-atomic (even in SC semantics)

# Adding Read-Modify-Write instructions

One can add the LOCK prefix (literally a one-byte opcode prefix) to make INC atomic

| LOCKINC                |                       | x86 |

|------------------------|-----------------------|-----|

| Initial state: x=0;    |                       |     |

| Thread 0               | Thread 1              |     |

| lock incq (x) //a0,a1  | lock incq (x) //b0,b1 |     |

| Final: x=1;            |                       |     |

| Observation: 0/1000000 |                       |     |

## Adding Read-Modify-Write instructions

One can add the LOCK prefix (literally a one-byte opcode prefix) to make INC atomic

LOCKINC x86

|                        |                       |

|------------------------|-----------------------|

| Initial state: x=0;    |                       |

| Thread 0               | Thread 1              |

| lock incq (x) //a0,a1  | lock incq (x) //b0,b1 |

| Final: x=1;            |                       |

| Observation: 0/1000000 |                       |

Also LOCK'd add, sub, xchg, etc., and cmpxchg

Being able to do that atomically is important for many low-level algorithms. On x86 can also do for other sizes, including for 8B and 16B adjacent-doublesize quantities

In early hardware implementations, this would literally lock the bus. Now, interconnects are much fancier.

Compare-and-swap (CAS):

```

lock cmpxchq src, dest

```

compares rax with dest, then:

- ▶ if equal, set ZF=1 and load src into dest,

- ▶ otherwise, clear ZF=0 and load dest into rax

All this is one *atomic* step.

Can use to solve *consensus* problem...

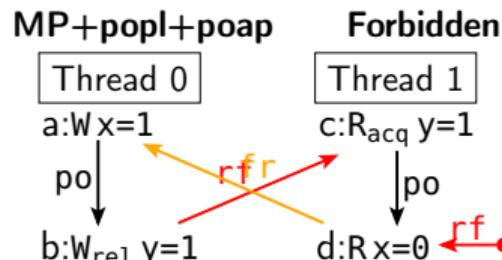

## Synchronising power of locked instructions

“Loads and stores are not reordered with locked instructions”

Intel Example 8-9: SB with xchg for the stores, forbidden

Intel Example 8-10: MP with xchg for the first store, forbidden

“Locked instructions have a total order”

Intel Example 8-8: IRIW with xchg for the stores, forbidden

# A rough guide to synchronisation costs

The costs of operations can vary widely between implementations and workloads, but for a very rough intuition, from Paul McKenney (<http://www2.rdrop.com/~paulmck/RCU/>):

Want to be here!

Heavily optimized reader-writer lock might get here for readers (but too bad about those poor writers...)

| Operation                               | Cost (ns) | Ratio |

|-----------------------------------------|-----------|-------|

| Clock period                            | 0.4       | 1     |

| “Best-case” CAS                         | 12.2      | 33.8  |

| Best-case lock                          | 25.6      | 71.2  |

| Single cache miss                       | 12.9      | 35.8  |

| CAS cache miss                          | 7.0       | 19.4  |

| Single cache miss ( <b>off-core</b> )   | 31.2      | 86.6  |

| CAS cache miss ( <b>off-core</b> )      | 31.2      | 86.5  |

| Single cache miss ( <b>off-socket</b> ) | 92.4      | 256.7 |

| CAS cache miss ( <b>off-socket</b> )    | 95.9      | 266.4 |

Typical synchronization mechanisms do this a lot, plus suffer from contention

11 © 2015 IBM Corporation

See Tim Harris's lectures for more serious treatment of performance

# Creating a usable model

## History of x86 concurrency specs

- ▶ Before Aug. 2007 (Era of Vagueness): A Cautionary Tale

# History of x86 concurrency specs

## ► Before Aug. 2007 (Era of Vagueness): A Cautionary Tale

*Intel 'Processor Ordering' model, informal prose*

Example: Linux Kernel mailing list, Nov–Dec 1999 (143 posts)

Keywords: speculation, ordering, cache, retire, causality

A one-instruction programming question; a microarchitectural debate!

### 1. `spin_unlock()` Optimization On Intel

20 Nov 1999 - 7 Dec 1999 (143 posts) Archive Link: "[spin\\_unlock optimization\(i386\)](#)"

Topics: [BSD](#), [FreeBSD](#), [SMP](#)

People: [Linus Torvalds](#), [Jeff V. Merkey](#), [Erich Boleyn](#), [Manfred Spraul](#), [Peter Samuelson](#), [Ingo Molnar](#)

Manfred Spraul thought he'd found a way to shave `spin_unlock()` down from about 22 ticks for the "`lock; btrl $0,%0`" asm code, to 1 tick for a simple "`movl $0,%0`" instruction, a huge gain. Later, he reported that Ingo Molnar noticed a 4% speed-up in a benchmark test, making the optimization very valuable. Ingo also added that the same optimization cropped up in the FreeBSD mailing list a few days previously. But Linus Torvalds poured cold water on the whole thing, saying:

It does NOT WORK!

Let the FreeBSD people use it, and let them get faster timings.

They will crash, eventually.

The window may be small, but if you do this, then suddenly spin-locks aren't reliable any more.

The issue is not writes being issued in-order (although all the Intel CPU books warn you NOT to assume that in-order write behaviour - I bet it won't be the case in the long run).

The issue is that you have to have a serializing instruction in order to make sure that the processor doesn't re-order things around the unlock.

For example, with a simple write, the CPU can legally delay a read that happened inside the critical region (maybe it missed a cache line), and get a stale value for any of the reads that should have been serialized by the spinlock.

Note that I actually thought this was a legal optimization, and for a while I had this in the kernel. It crashed. In random ways.

# History of x86 concurrency

## ► Before Aug. 2007

*Resolved only by appeal to an oracle:*

pins, reads (cache miss) and writes appear in-order." He concluded from this that the second CPU would never see the `spin_unlock()` before the "b=a" line. Linus agreed that on a Pentium, Manfred was right. However, he quoted in turn from the Pentium Pro manual, "The only enhancement in the PentiumPro processor is the added support for speculative reads and store-buffer forwarding." He explained:

A Pentium is a in-order machine, without any of the interesting speculation wrt reads etc. So on a Pentium you'll never see the problem.

But a Pentium is also very uninteresting from a SMP standpoint these days. It's just too weak with too little per-CPU cache etc..

This is why the PPro has the MTRR's - exactly to let the core do speculation (a Pentium doesn't need MTRR's, as it won't re-order anything external to the CPU anyway, and in fact won't even re-order things internally).

Jeff V. Merkey added:

What Linus says here is correct for PPro and above. Using a `mov` instruction to unlock does work fine on a 486 or Pentium SMP system, but as of the PPro, this was no longer the case, though the window is so infinitesimally small, most kernels don't hit it (Netware 4/5 uses this method but it's spinlocks understand this and the code is written to handle it. The most obvious aberrant behavior was that cache inconsistencies would occur randomly. PPro uses lock to signal that the pipelines are no longer invalid and the buffers should be blown out.

I have seen the behavior Linus describes on a hardware analyzer, BUT ONLY ON SYSTEMS THAT WERE PPRO AND ABOVE. I guess the BSD people must still be on older Pentium hardware and that's why they don't know this can bite in some cases.

Erich Boleyn, an Architect in an IA32 development group at Intel, also replied to Linus, pointing out a possible misconception in his proposed exploit. Regarding the code Linus posted, Erich replied:

It will always return 0. You don't need "`spin_unlock()`" to be serializing.

The only thing you need is to make sure there is a store in "`spin_unlock()`", and that is kind of true by the fact that you're changing something to be observable on other processors.

## History of x86 concurrency specs

- ▶ Before Aug. 2007 (Era of Vagueness): A Cautionary Tale

## History of x86 concurrency specs

- ▶ Before Aug. 2007 (Era of Vagueness): A Cautionary Tale

- ▶ IWP and AMD64, Aug. 2007/Oct. 2008 (Era of Causality)

- Intel published a white paper (IWP) defining 8 informal-prose principles, e.g.

- P1 Loads are not reordered with older loads

- P2 Stores are not reordered with older stores

- P5 Intel 64 memory ordering ensures **transitive visibility of stores** — i.e. stores that are **causally related** appear to execute in an order consistent with **the causal relation**

- supported by 10 litmus tests illustrating allowed or forbidden behaviours.

## History of x86 concurrency specs

- ▶ Before Aug. 2007 (Era of Vagueness): A Cautionary Tale

- ▶ IWP and AMD64, Aug. 2007/Oct. 2008 (Era of Causality)

- Intel published a white paper (IWP) defining 8 informal-prose principles, e.g.

- P1 Loads are not reordered with older loads

- P2 Stores are not reordered with older stores

- P5 Intel 64 memory ordering ensures **transitive visibility of stores** — i.e. stores that are **causally related** appear to execute in an order consistent with **the causal relation**

- supported by 10 litmus tests illustrating allowed or forbidden behaviours.

- ▶ We codify these principles in an axiomatic model, x86-CC [1, POPL 2009]

## History of x86 concurrency specs

- ▶ Before Aug. 2007 (Era of Vagueness): A Cautionary Tale

- ▶ IWP and AMD64, Aug. 2007/Oct. 2008 (Era of Causality)

- Intel published a white paper (IWP) defining 8 informal-prose principles, e.g.

- P1 Loads are not reordered with older loads

- P2 Stores are not reordered with older stores

- P5 Intel 64 memory ordering ensures **transitive visibility of stores** — i.e. stores that are **causally related** appear to execute in an order consistent with **the causal relation**

supported by 10 litmus tests illustrating allowed or forbidden behaviours.

- ▶ We codify these principles in an axiomatic model, x86-CC [1, POPL 2009]

But there are problems:

1. the principles are ambiguous (we interpret them as w.r.t. a single causal order)

2. the principles (and our model) leave IRIW allowed, even with mfences, but the Sun implementation of the Java Memory Model assumes that mfences recovers SC

3. the model is unsound w.r.t. observable behaviour, as noted by Paul Loewenstein, with an example that is allowed in the store-buffer model

## History of x86 concurrency specs

- ▶ Intel SDM rev.27– and AMD 3.17–, Nov. 2008–

Now explicitly excludes IRIW:

- ▶ Any two stores are seen in a consistent order by processors other than those performing the stores

But, still ambiguous w.r.t. causality, and the view by those processors is left unspecified

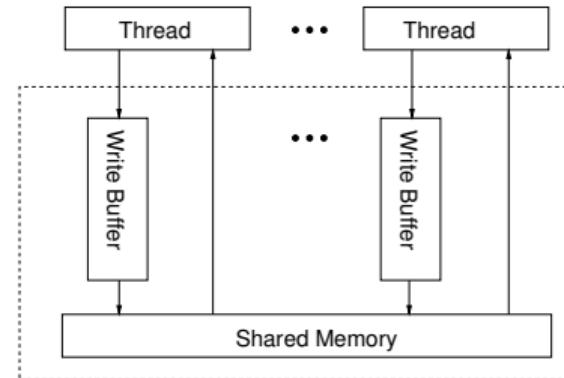

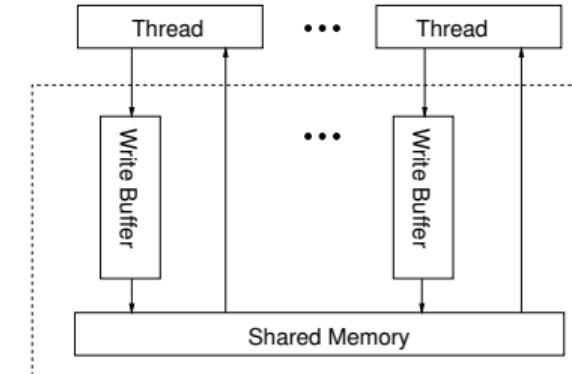

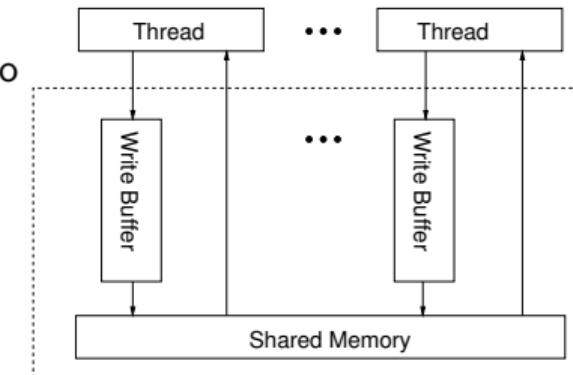

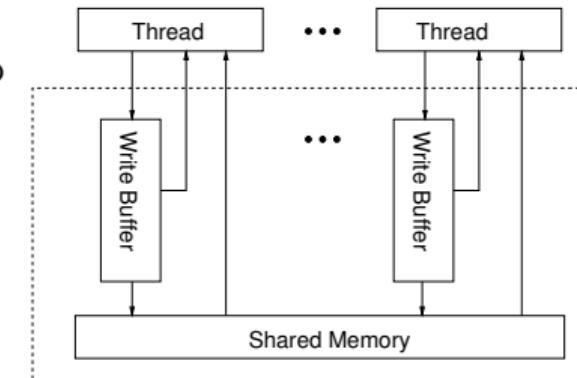

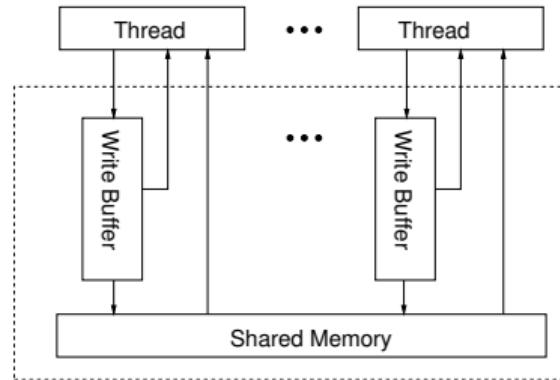

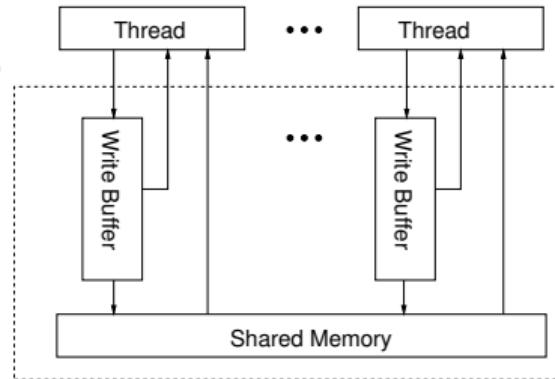

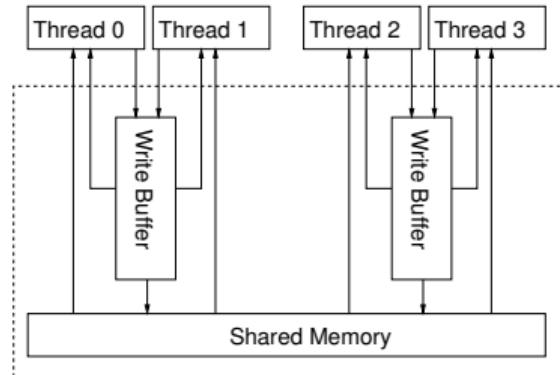

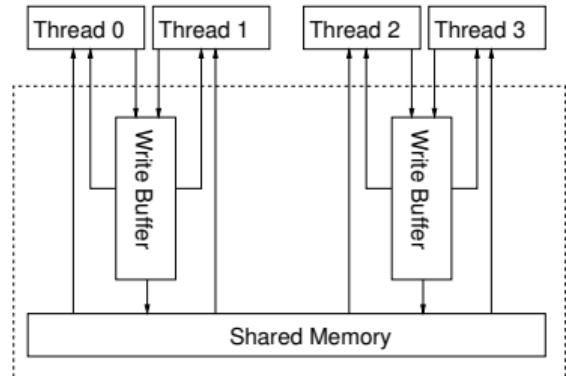

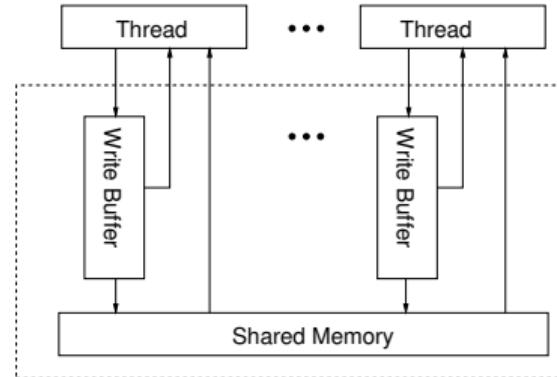

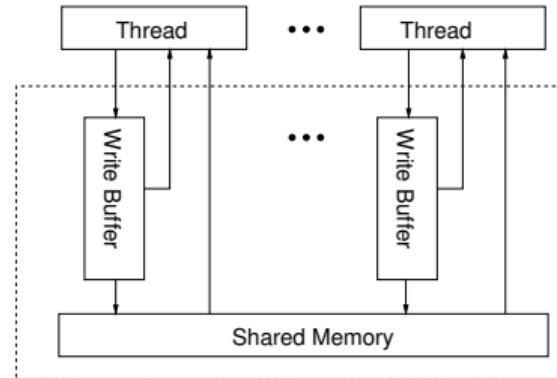

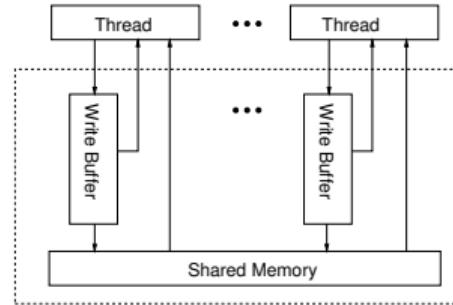

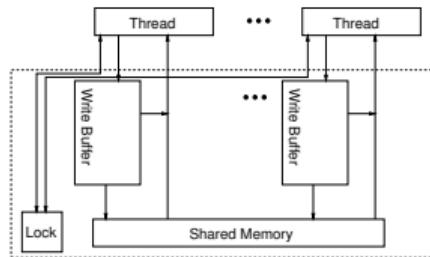

## Creating a good x86 concurrency model

We had to *create* a good concurrency model for x86 – “good” meaning the desirable properties listed before

Key facts:

- ▶ Store buffering (with forwarding) is observable

- ▶ These store buffers appear to be FIFO

- ▶ We don't see observable buffering of read requests

- ▶ We don't see other observable out-of-order or speculative execution

- ▶ IRIW and WRC not observable, and now forbidden by the docs – so *multicopy atomic*

- ▶ mfence appears to wait for the local store buffer to drain

- ▶ as do LOCK'd instructions, before they execute

- ▶ Various other reorderings are not observable and are forbidden

These suggested that x86 is, in practice, like SPARC TSO: the observable effects of store buffers are the only observable relaxed-memory behaviour

Our **x86-TSO** model codifies this, adapting SPARC TSO

Owens, Sarkar, Sewell [4, TPHOLs 2009] [5, CACM 2010]

# Operational and axiomatic concurrency model definitions

Two styles:

## Operational

- ▶ an *abstract machine*

- ▶ incrementally executable

- ▶ often *abstract-microarchitectural operational models*

## Axiomatic

- ▶ a *predicate on candidate executions*

- ▶ usually (but not always) further from microarchitecture

(more concise, but less hardware intuition)

- ▶ not straightforwardly incrementally executable

# Operational and axiomatic concurrency model definitions

Two styles:

## Operational

- ▶ an *abstract machine*

- ▶ incrementally executable

- ▶ often *abstract-microarchitectural operational models*

## Axiomatic

- ▶ a *predicate on candidate executions*

- ▶ usually (but not always) further from microarchitecture

(more concise, but less hardware intuition)

- ▶ not straightforwardly incrementally executable

Ideally both, proven equivalent

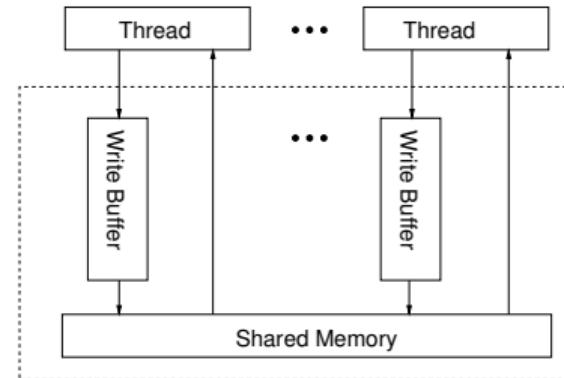

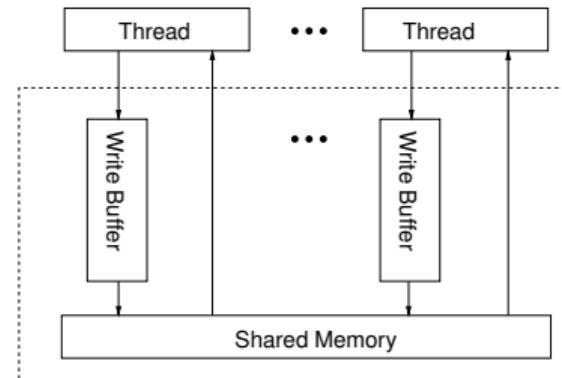

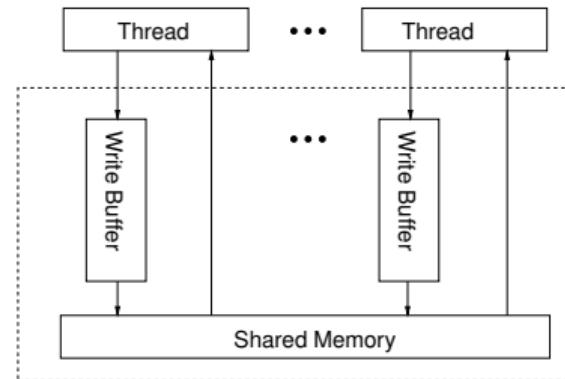

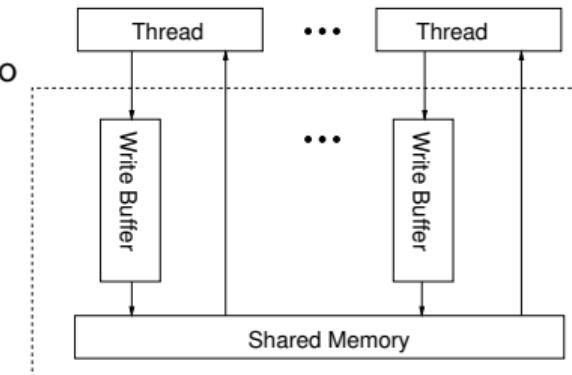

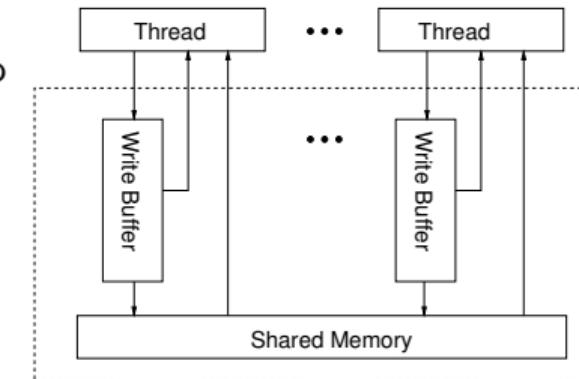

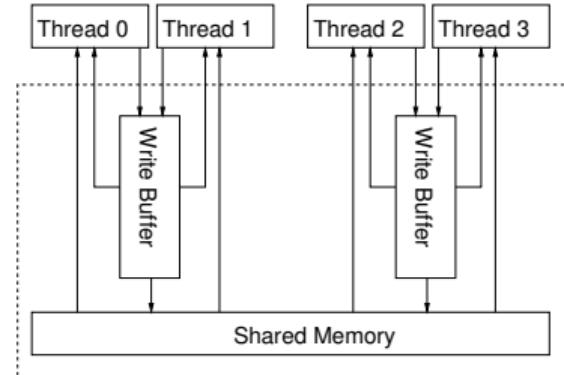

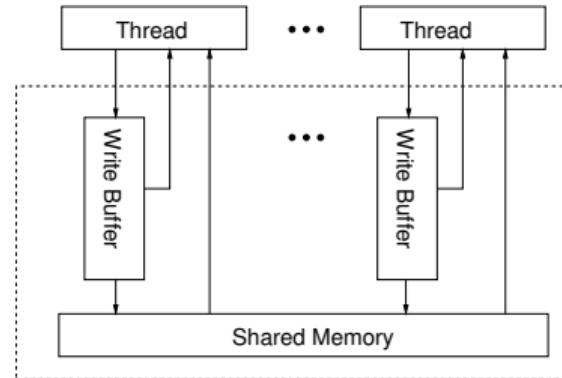

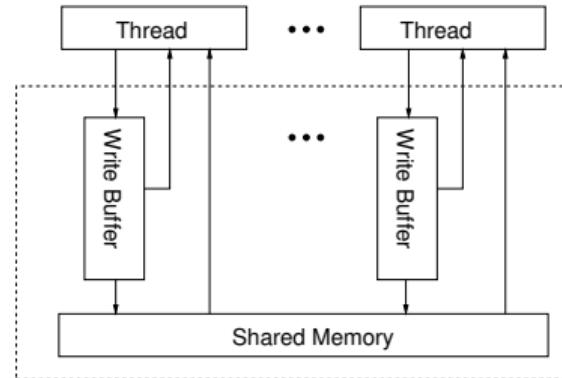

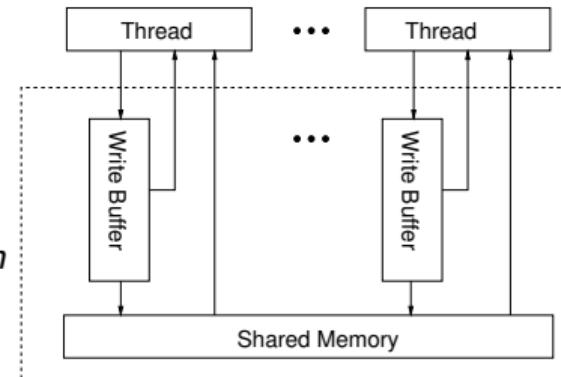

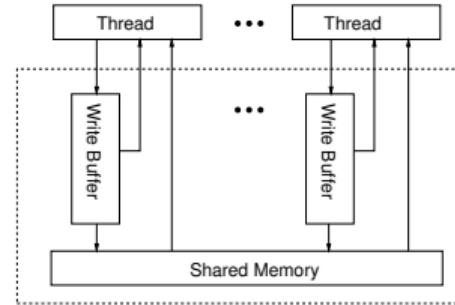

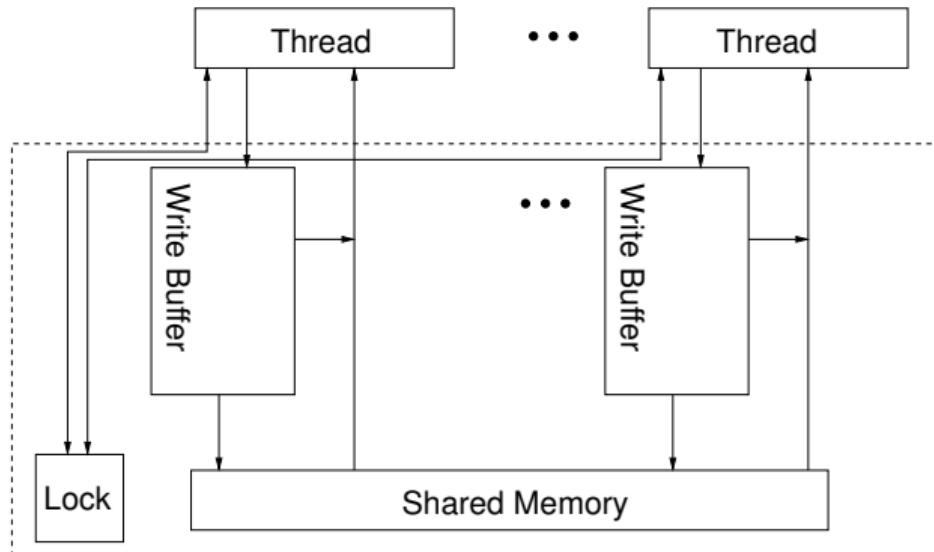

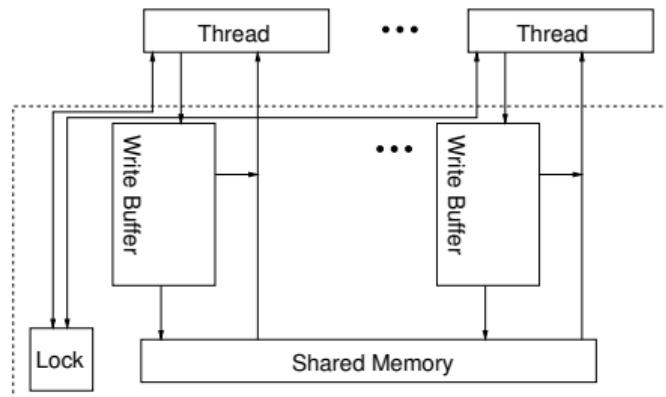

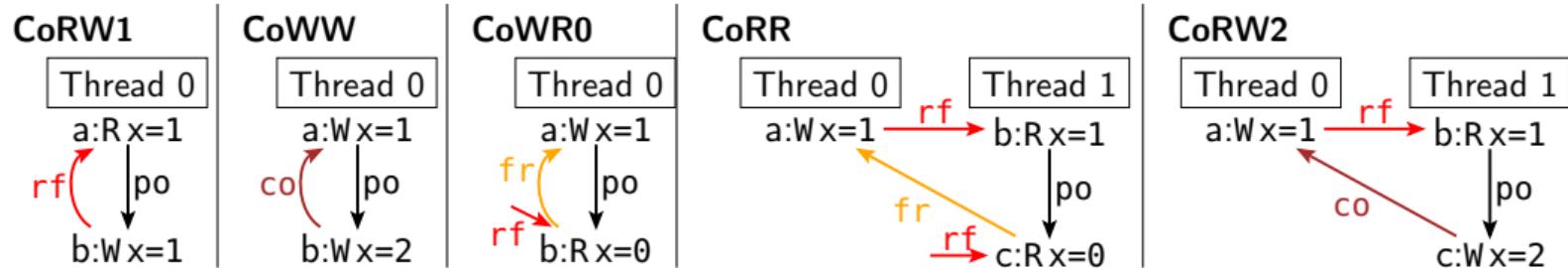

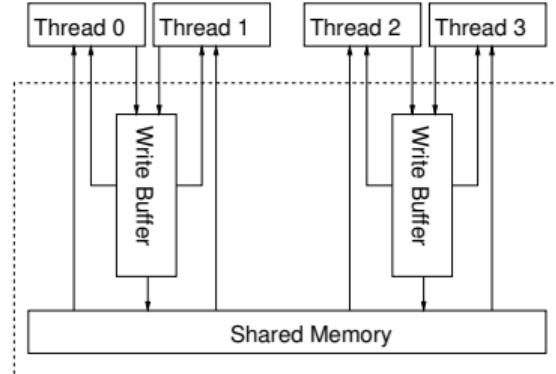

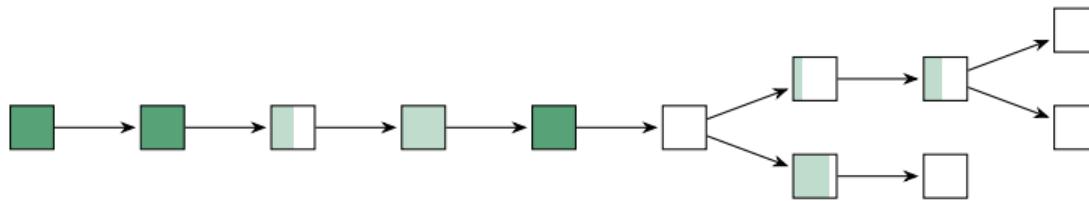

# x86-TSO operational model

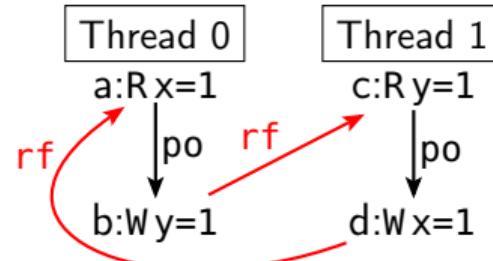

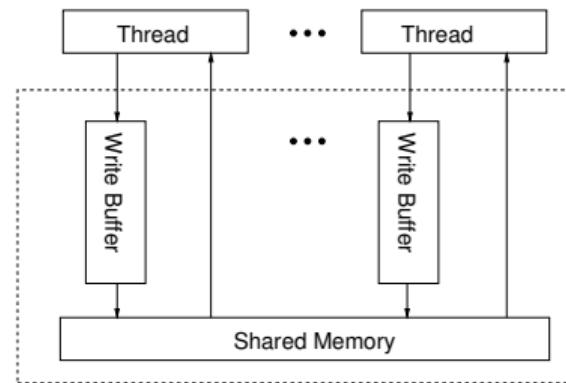

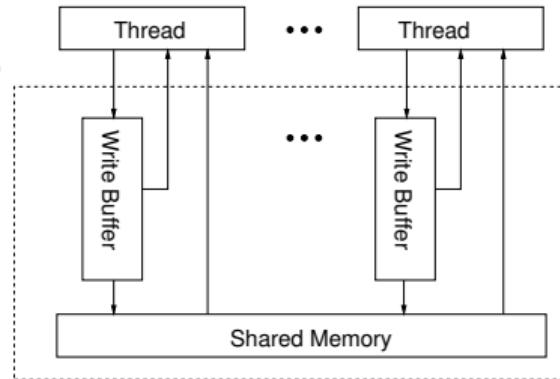

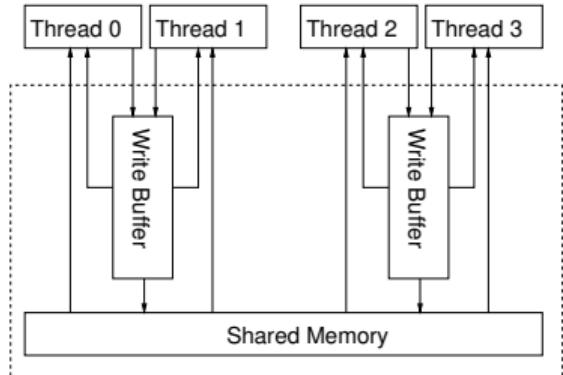

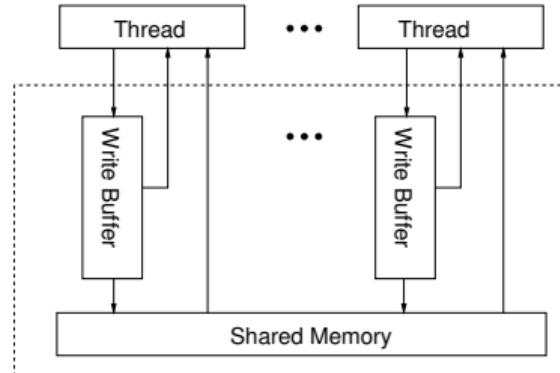

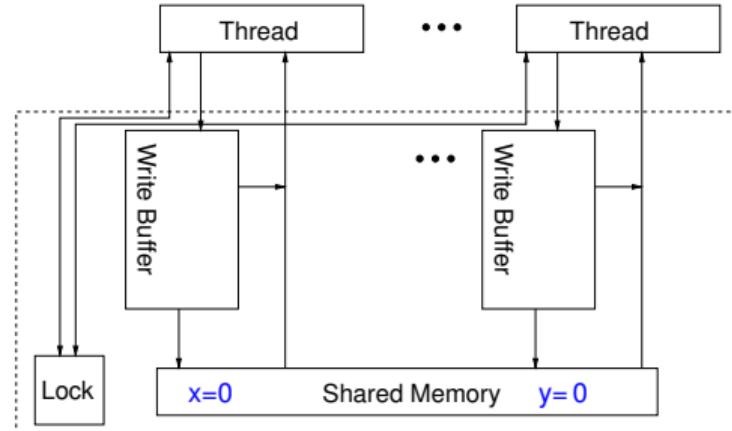

# x86-TSO Abstract Machine

Like the sketch except with state recording which (if any) thread has the machine lock

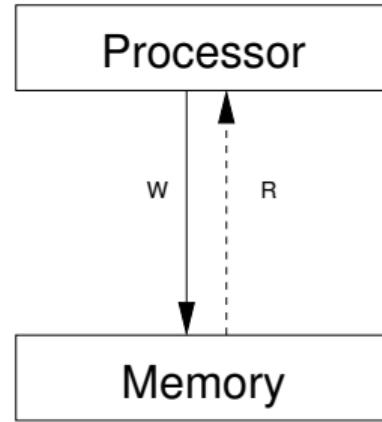

# x86-TSO Abstract Machine

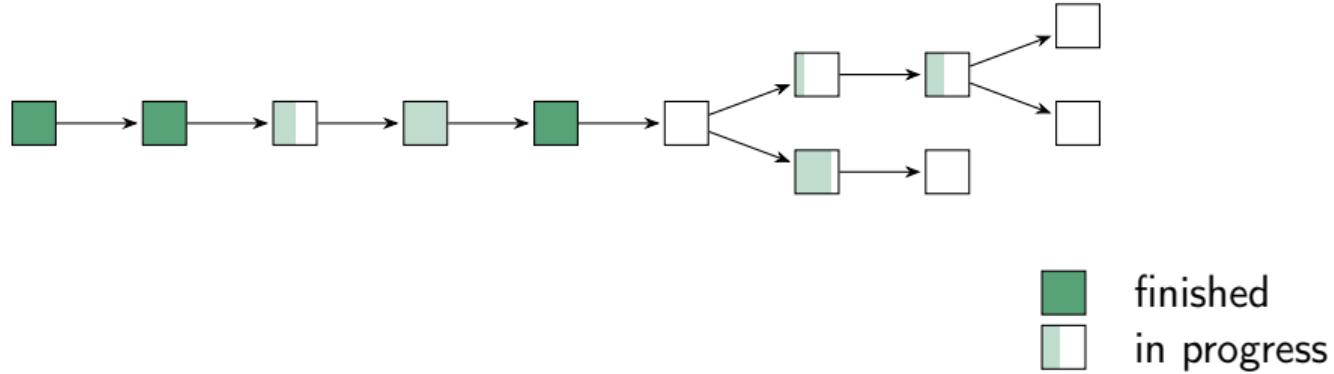

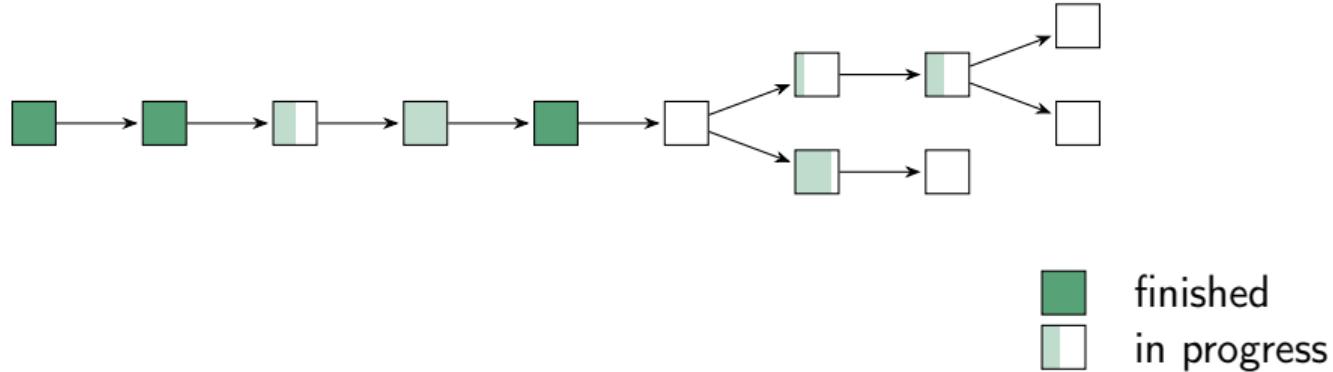

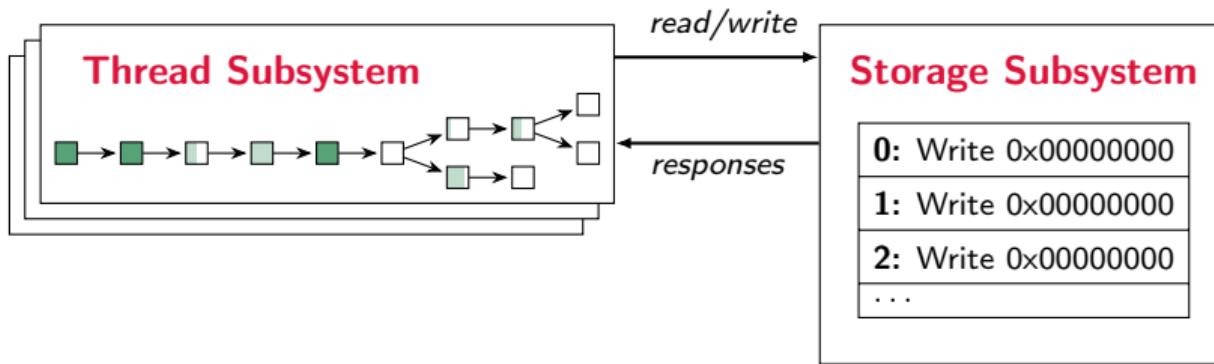

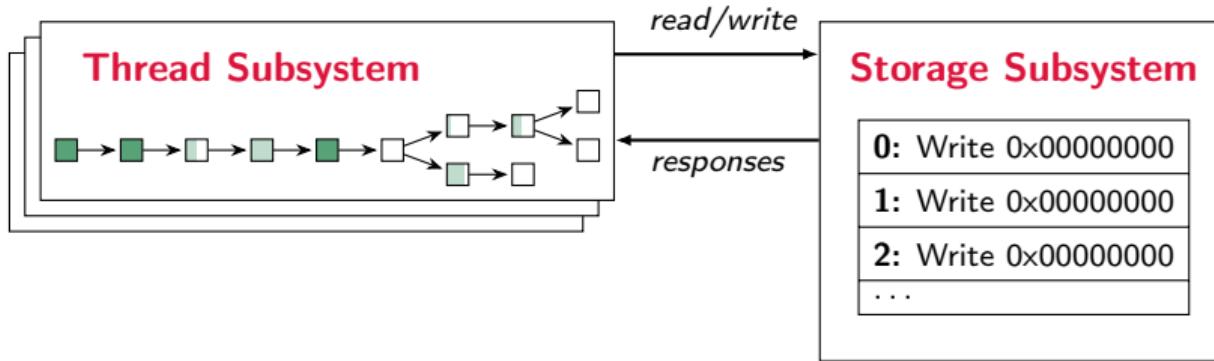

We factor the model into the *thread semantics* and the *memory model*.

The x86-TSO thread semantics just executes each instruction in program order

The whole machine is modelled as a parallel composition of the thread semantics (for each thread) and the x86-TSO memory-model abstract machine...

...exchanging messages for reads, writes, barriers, and machine lock/unlock events

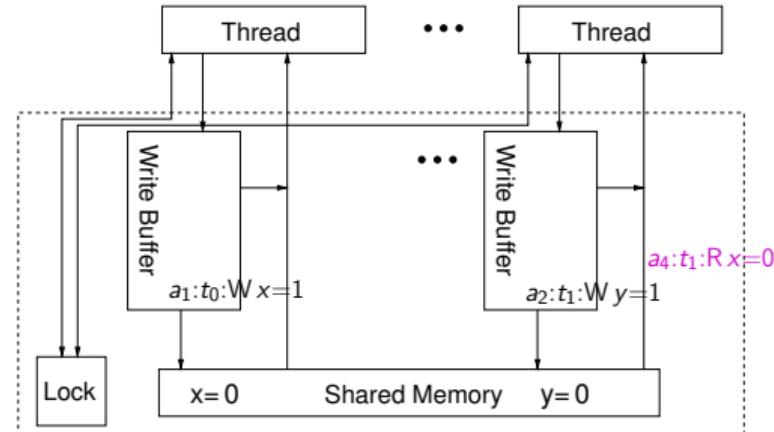

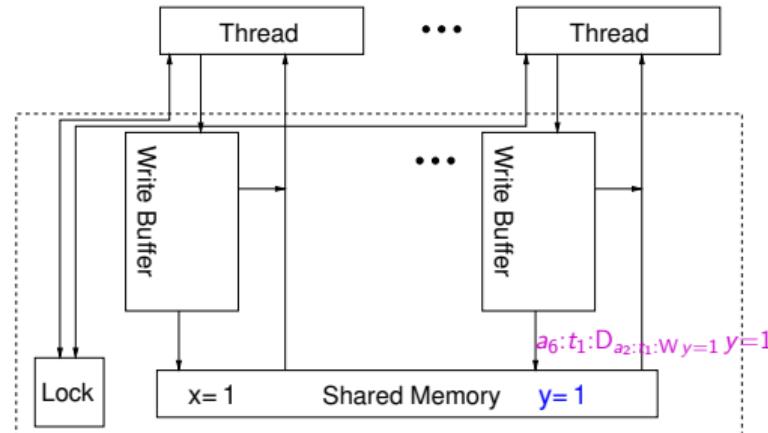

## x86-TSO Abstract Machine: Memory Behaviour

We formalise the x86-TSO memory-model abstract machine as a transition system

$$m \xrightarrow{e} m'$$

Read as: memory in state  $m$  can do a transition with event  $e$  to memory state  $m'$

## x86-TSO Abstract Machine: threads/memory interface

|                |               |                                                                                                                                 |

|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| Events $e ::=$ | $a:t:W x=v$   | a write of value $v$ to address $x$ by thread $t$ , ID $a$                                                                      |

|                | $a:t:R x=v$   | a read of $v$ from $x$ by $t$                                                                                                   |

|                | $a:t:D_w x=v$ | an internal action of the abstract machine, dequeuing<br>$w = (a':t:W x=v)$ from thread $t$ 's write buffer<br>to shared memory |

|                | $a:t:F$       | an MFENCE memory barrier by $t$                                                                                                 |

|                | $a:t:L$       | start of an instruction with LOCK prefix by $t$                                                                                 |

|                | $a:t:U$       | end of an instruction with LOCK prefix by $t$                                                                                   |

where

- ▶  $a$  is a unique event ID, of type  $eid$

- ▶  $t$  is a hardware thread id, of type  $tid$

- ▶  $x$  and  $y$  are memory addresses, of type  $addr$

- ▶  $v$  and  $w$  are memory values, of type  $value$

- ▶  $w$  is a write event  $a:t:W x=v$ , of type  $write\_event$

## x86-TSO Abstract Machine: Memory States

An x86-TSO abstract-machine memory state  $m$  is a record with fields  $M$ ,  $B$ , and  $L$ :

$$m : \langle M : \text{addr} \rightarrow \text{value}; \\ B : \text{tid} \rightarrow \text{write\_event list}; \\ L : \text{tid option} \rangle$$

Here:

- ▶  $m.M$  is the shared memory, mapping addresses to values

- ▶  $m.B$  gives the store buffer for each thread, a list of write events, most recent first (we use a list of write events for simplicity in proofs, but the event and thread IDs are erasable)

- ▶  $m.L$  is the global machine lock, indicating when some thread has exclusive access to memory. It is a *tid option*, either `None`, or `Some t` for some thread ID  $t$

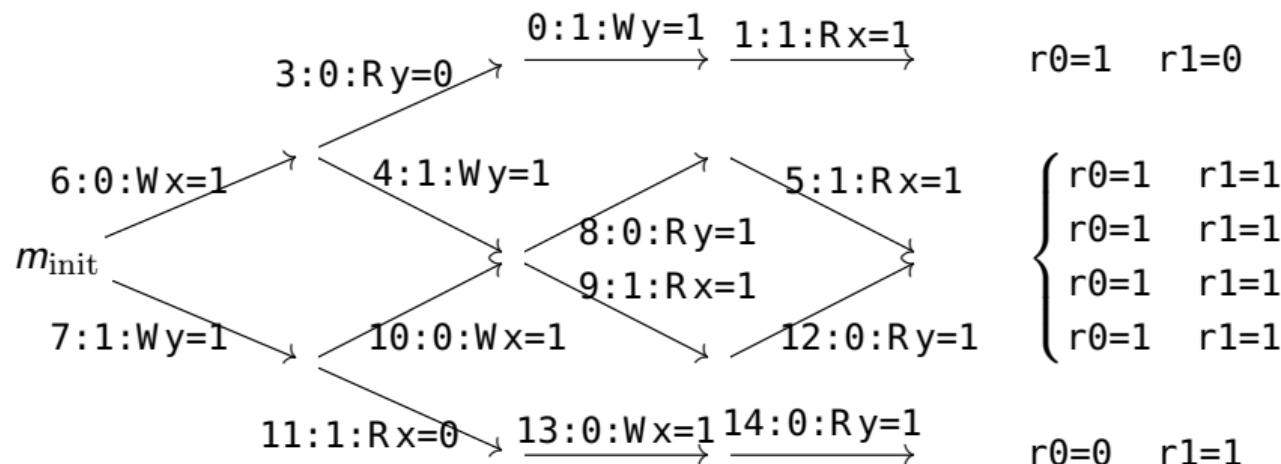

The initial state  $m_{\text{init}}$  has  $m_{\text{init}}.M$  zero for each address,  $m_{\text{init}}.B$  empty for all threads, and  $m_{\text{init}}.L = \text{None}$  (lock not taken).

## Notation

Some and None construct optional values

$(\cdot, \cdot)$  builds tuples

$[]$  builds lists

$@$  appends lists

$\cdot \oplus \langle \cdot := \cdot \rangle$  updates records

$\cdot \oplus (\cdot \mapsto \cdot)$  updates functions.

$\text{id}(e)$ ,  $\text{thread}(e)$ ,  $\text{addr}(e)$ ,  $\text{value}(e)$  extract the respective components of event  $e$

$\text{isread}(e)$ ,  $\text{iswrite}(e)$ ,  $\text{isdequeue}(e)$ ,  $\text{ismfence}(e)$  identify the corresponding kinds

## x86-TSO Abstract Machine: Auxiliary Definitions

Say there are *no pending* writes in  $t$ 's buffer  $m.B(t)$  for address  $x$  if there are no write events  $w$  in  $m.B(t)$  with  $\text{addr}(w) = x$ .

Say  $t$  is *not blocked* in machine state  $m$  if either it holds the lock ( $m.L = \text{Some } t$ ) or the lock is not held ( $m.L = \text{None}$ ).

# x86-TSO Abstract Machine: Behaviour

## RM: Read from memory

$$\frac{\text{not\_blocked}(m, t) \quad m.M(x) = v \quad \text{no\_pending}(m.B(t), x)}{m \xrightarrow{a:t:\text{R } x=v} m}$$

Thread  $t$  can read  $v$  from memory at address  $x$  if  $t$  is not blocked, the memory does contain  $v$  at  $x$ , and there are no writes to  $x$  in  $t$ 's store buffer.

(the event ID  $a$  is left unconstrained by the rule)

# x86-TSO Abstract Machine: Behaviour

## RB: Read from write buffer

not\_blocked( $m, t$ )

$\exists a' b_1 b_2. m.B(t) = b_1 @ [a':t:W x=v] @ b_2$

no\_pending( $b_1, x$ )

---

$m \xrightarrow{a:t:R x=v} m$

Thread  $t$  can read  $v$  from its store buffer for address  $x$  if  $t$  is not blocked and has  $v$  as the value of the most recent write to  $x$  in its buffer.

# x86-TSO Abstract Machine: Behaviour

## WB: Write to write buffer

---

$$m \xrightarrow{a:t:W x=v} m \oplus \langle B := m.B \oplus (t \mapsto ([a:t:W x=v] @ m.B(t))) \rangle$$

Thread  $t$  can write  $v$  to its store buffer for address  $x$  at any time.

## x86-TSO Abstract Machine: Behaviour

### DM: Dequeue write from write buffer to memory

not\_blocked( $m, t$ )

$m.B(t) = b @ [a':t:W x=v]$

---

$$m \xrightarrow{a:t:D_{a':t:W} x=v} m \oplus \langle M := m.M \oplus (x \mapsto v) \rangle \oplus \langle B := m.B \oplus (t \mapsto b) \rangle$$

If Thread  $t$  is not blocked, it can silently dequeue the oldest write from its store buffer and update memory at that address with the new value, without coordinating with any hardware thread.

(we record the write in the dequeue event just to simplify proofs.)

## x86-TSO Abstract Machine: Behaviour

**M: MFENCE**

$$\frac{m.B(t) = []}{m \xrightarrow{a:t:F} m}$$

If Thread  $t$ 's store buffer is empty, it can execute an MFENCE (otherwise the MFENCE blocks until that becomes true).

## Adding LOCK'd instructions to the model

We define the instruction semantics for locked instructions to bracket the transitions of their unlocked variant with  $a:t:L$  and  $a':t:U$ .

For example, a `lock inc x`, in thread  $t$ , will do

1.  $a_1:t:L$

2.  $a_2:t:R x=v$  for an arbitrary  $v$

3.  $a_3:t:W x=(v+1)$

4.  $a_4:t:U$

This lets us reuse the `inc` semantics for `lock inc`, and to do so uniformly for all RMWs.

# x86-TSO Abstract Machine: Behaviour

## L: Lock

$$\frac{m.L = \text{None} \quad m.B(t) = []}{m \xrightarrow{a:t:L} m \oplus \langle L := \text{Some}(t) \rangle}$$

If the lock is not held and its buffer is empty, thread  $t$  can begin a LOCK'd instruction.

Note that if a hardware thread  $t$  comes to a LOCK'd instruction when its store buffer is not empty, the machine can take one or more  $a:t:D_w x=v$  steps to empty the buffer and then proceed.

# x86-TSO Abstract Machine: Behaviour

## U: Unlock

$$\frac{m.L = \text{Some}(t) \quad m.B(t) = []}{m \xrightarrow{a:t:U} m \oplus \langle L := \text{None} \rangle}$$

If  $t$  holds the lock, and its store buffer is empty, it can end a LOCK'd instruction, resetting the lock.

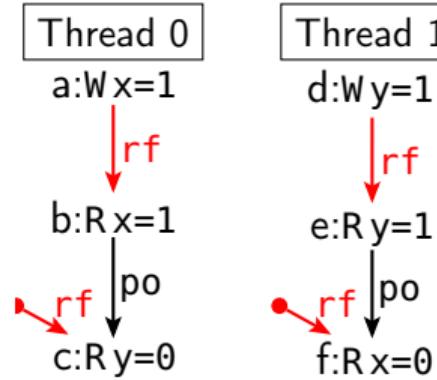

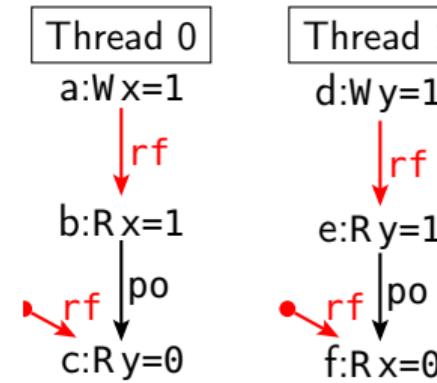

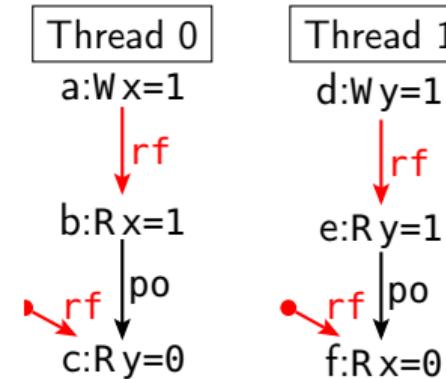

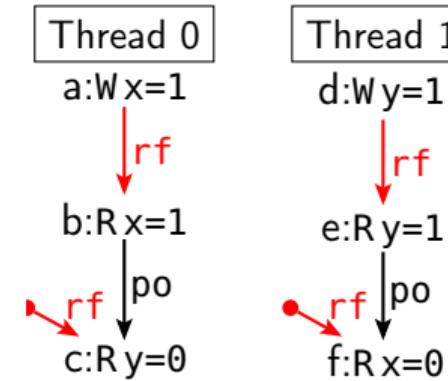

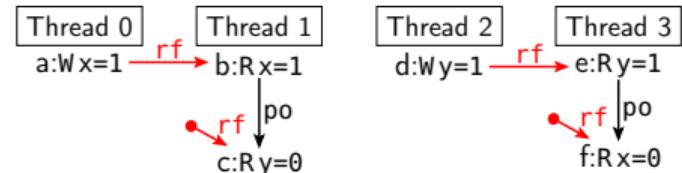

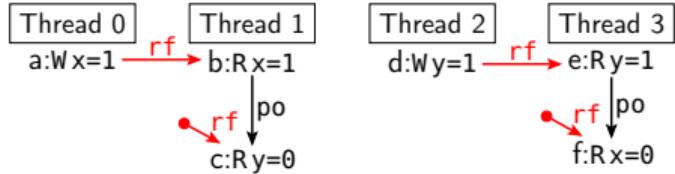

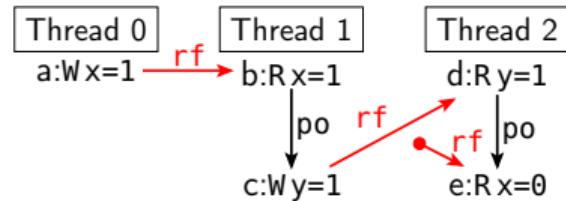

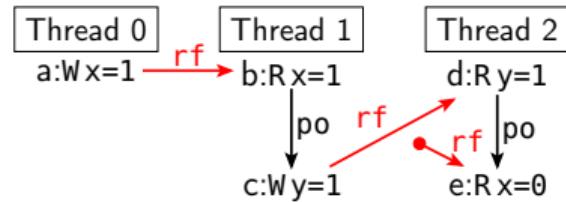

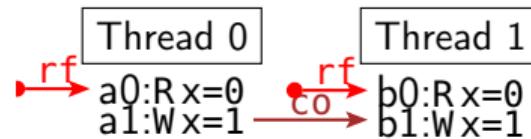

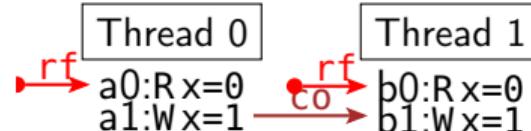

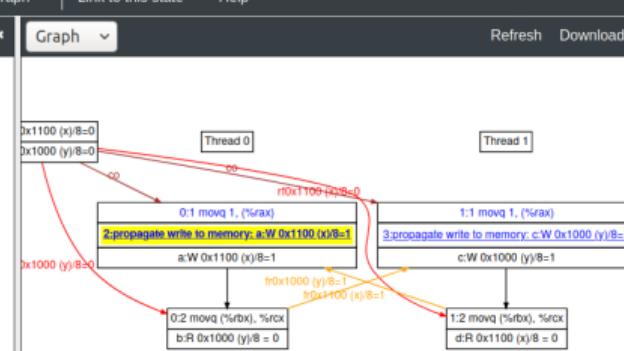

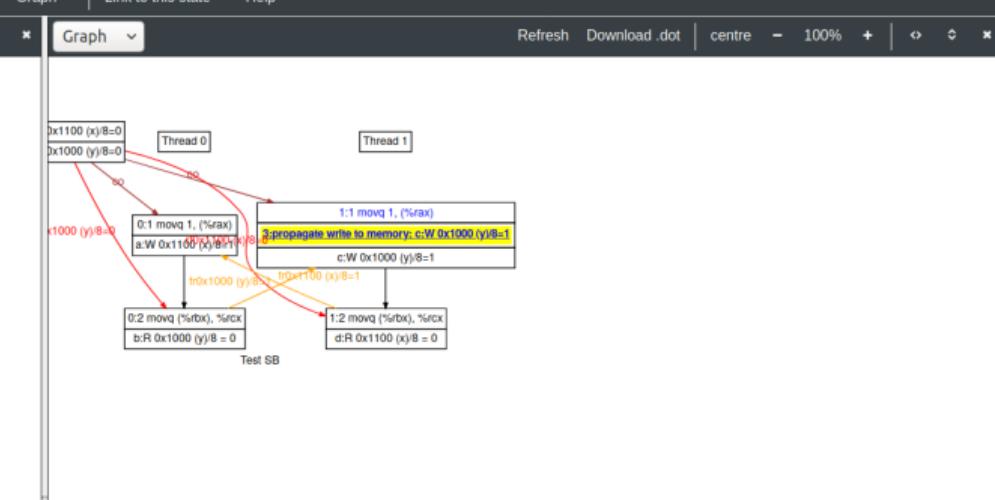

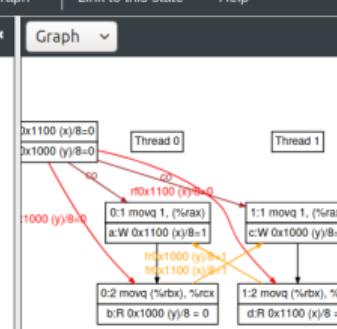

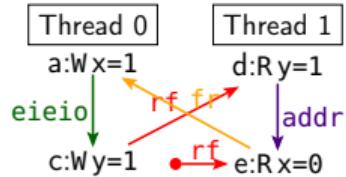

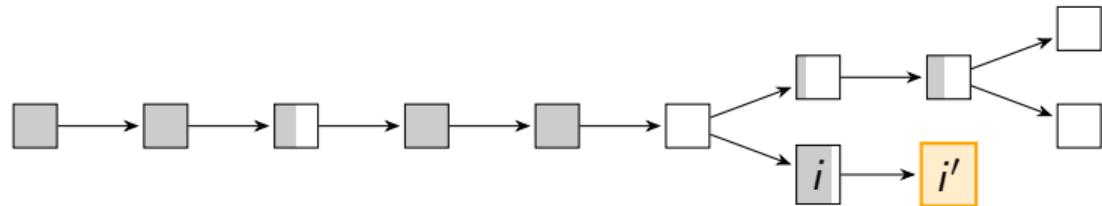

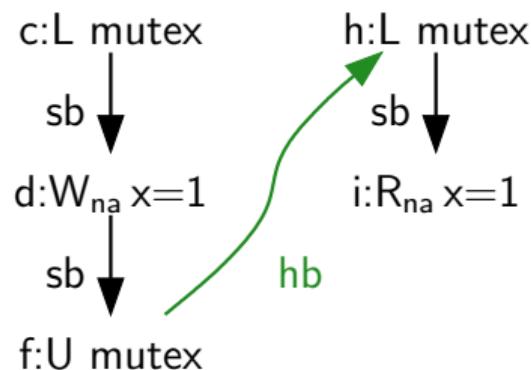

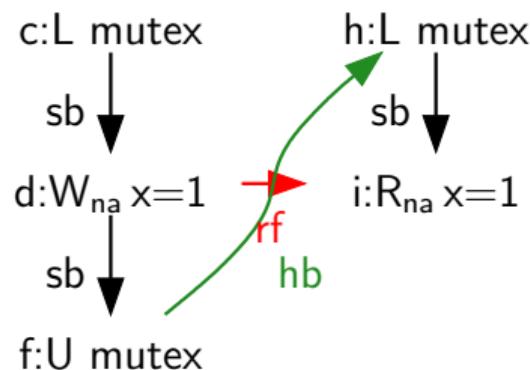

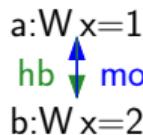

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

Thread 0

movq \$1, (x) //a

movq (y), %rax //b

Thread 1

movq \$1, (y) //c

movq (x), %rax //d

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

x86

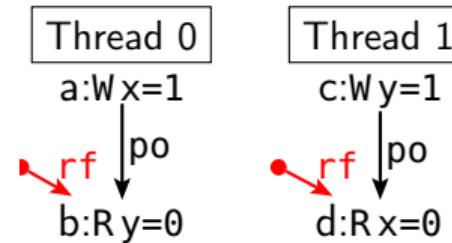

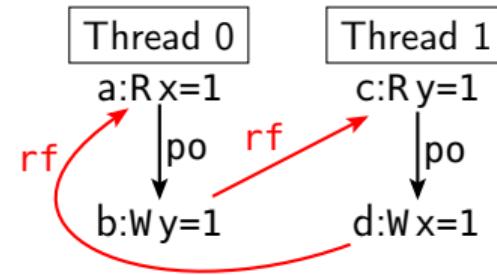

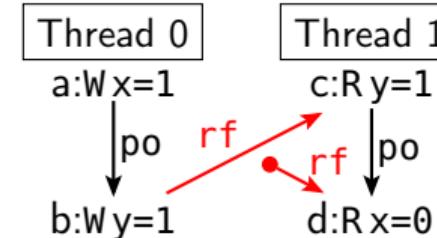

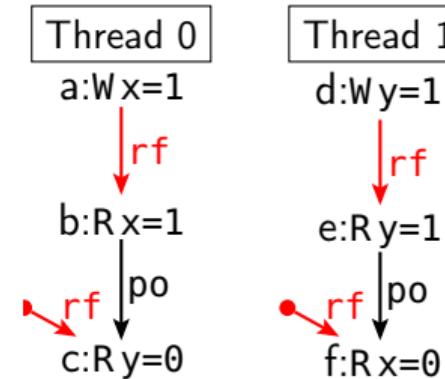

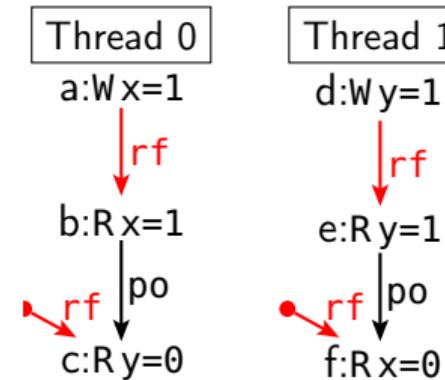

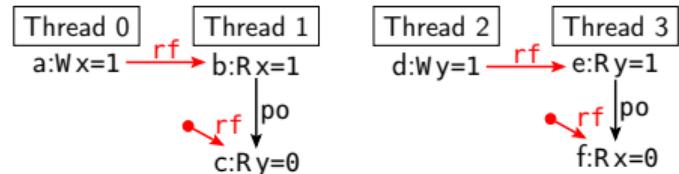

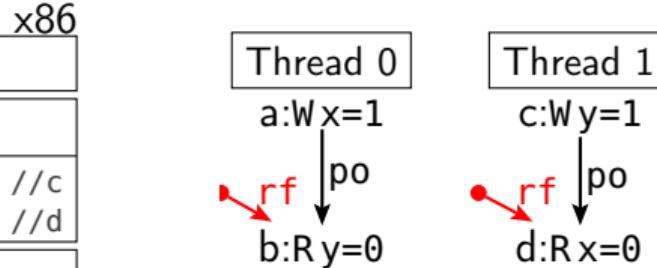

Thread 0

a:W x=1

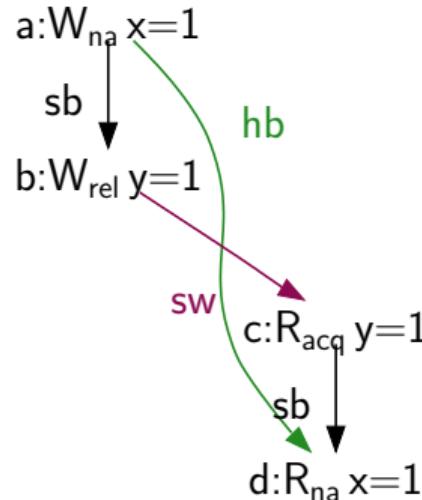

rf

po

b:R y=0

Thread 1

c:W y=1

rf

po

d:R x=0

$m_{init}$

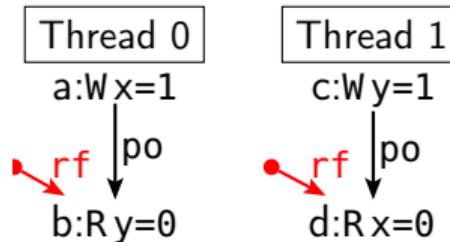

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

Thread 0

movq \$1, (x) //a

movq (y), %rax //b

Thread 1

movq \$1, (y) //c

movq (x), %rax //d

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

x86

Thread 0

a:W x=1

po

rf

b:R y=0

Thread 1

c:W y=1

po

rf

d:R x=0

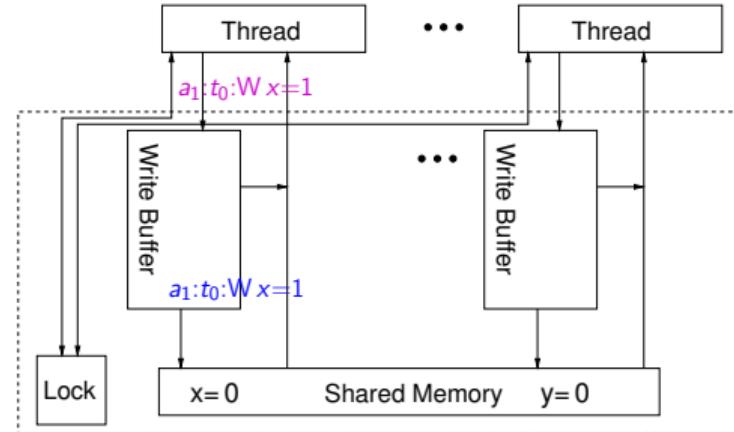

$m_{init} \xrightarrow{a_1:t_0:W x=1}$

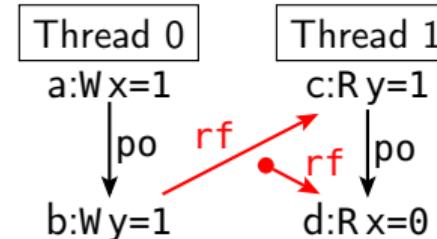

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

Thread 0

movq \$1, (x) //a

movq (y), %rax //b

Thread 1

movq \$1, (y) //c

movq (x), %rax //d

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

x86

Thread 0

a:W x=1

rf

po

b:R y=0

Thread 1

c:W y=1

rf

po

d:R x=0

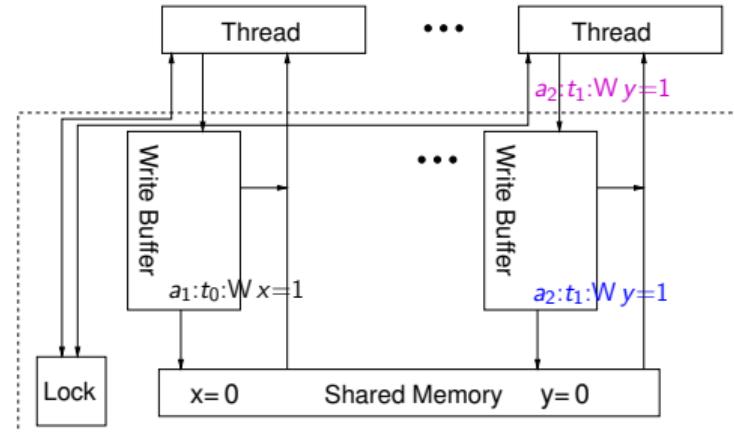

$m_{init} \xrightarrow{a_1:t_0:W\ x=1} \xrightarrow{a_2:t_1:W\ y=1}$

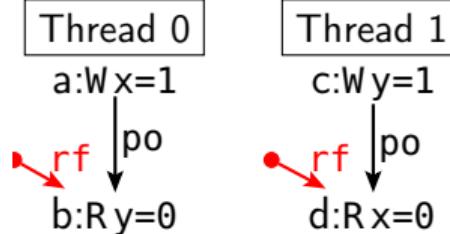

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| x86                      |                    |

|--------------------------|--------------------|

| Thread 0                 | Thread 1           |

| movq \$1, (x) //a        | movq \$1, (y) //c  |

| movq (y), %rax //b       | movq (x), %rax //d |

| Final: 0:rax=0; 1:rax=0; |                    |

Observation: 171/1000000000

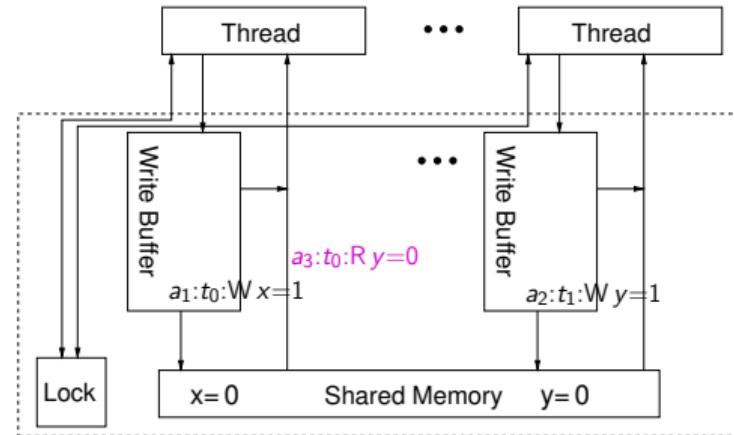

$m_{init} \xrightarrow{a_1:t_0:W\ x=1} \xrightarrow{a_2:t_1:W\ y=1} \xrightarrow{a_3:t_0:R\ y=0}$

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0                 |  | Thread 1           |  |

|--------------------------|--|--------------------|--|

| movq \$1, (x) //a        |  | movq \$1, (y) //c  |  |

| movq (y), %rax //b       |  | movq (x), %rax //d |  |

| Final: 0:rax=0; 1:rax=0; |  |                    |  |

Observation: 171/1000000000

x86

$m_{init} \xrightarrow{a_1:t_0:W\ x=1} \xrightarrow{a_2:t_1:W\ y=1} \xrightarrow{a_3:t_0:R\ y=0} \xrightarrow{a_4:t_1:R\ x=0}$

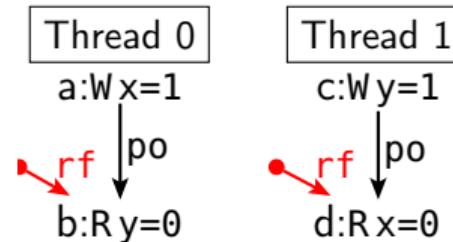

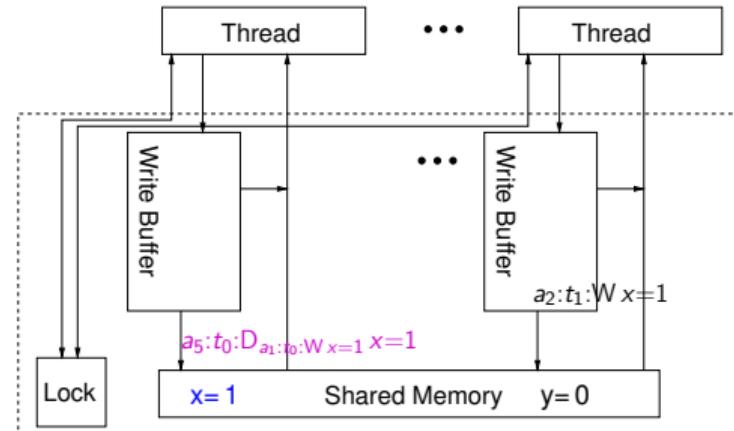

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

Thread 0

movq \$1, (x) //a

movq (y), %rax //b

Thread 1

movq \$1, (y) //c

movq (x), %rax //d

Final: 0:rax=0; 1:rax=0;

Observation: 171/1000000000

x86

Thread 0

a:W x=1

rf

po

b:R y=0

Thread 1

c:W y=1

rf

po

d:R x=0

$m_{init} \xrightarrow{a_1:t_0:W x=1} \xrightarrow{a_2:t_1:W y=1} \xrightarrow{a_3:t_0:R y=0} \xrightarrow{a_4:t_1:R x=0} \xrightarrow{a_5:t_0:D_{a_1:t_0:W x=1} x=1}$

# First Example, Revisited

SB

Initial state: 0:rax=0; 1:rax=0; y=0; x=0;

| Thread 0                 |  | Thread 1           |  |

|--------------------------|--|--------------------|--|

| movq \$1, (x) //a        |  | movq \$1, (y) //c  |  |

| movq (y), %rax //b       |  | movq (x), %rax //d |  |

| Final: 0:rax=0; 1:rax=0; |  |                    |  |

Observation: 171/1000000000

x86

$m_{init} \xrightarrow{a_1:t_0:W\ x=1} \xrightarrow{a_2:t_1:W\ y=1} \xrightarrow{a_3:t_0:R\ y=0} \xrightarrow{a_4:t_1:R\ x=0} \xrightarrow{a_5:t_0:D_{a_1:t_0:W\ x=1}\ x=1} \xrightarrow{a_6:t_1:D_{a_2:t_1:W\ y=1}\ y=1}$

## Does MFENCE restore SC?

Intuitively, if the program executed by the thread semantics has an mfence between every pair of memory accesses, then any execution in x86-TSO will have essentially identical behaviour to the same program with nops in place of mfences in SC.

What does “essentially identical” mean? The same set of interface traces except with the  $a:t:F$  and  $a:t:D_w\ x=v$  events erased.

# Restoring SC with RMWs

## NB: This is an *Abstract* Machine

A tool to specify exactly and only the *programmer-visible behavior*, based on hardware intuition, but not a description of real implementation internals

$\supseteq_{\text{beh}} \neq_{\text{hw}}$

Force: Of the internal optimizations of x86 processors, *only* per-thread FIFO write buffers are (ignoring timing) visible to programmers.

Still quite a loose spec: unbounded buffers, nondeterministic unbuffering, arbitrary interleaving

## Remark: Processors, Hardware Threads, and Threads

Our 'Threads' are hardware threads.

Some processors have *simultaneous multithreading* (Intel: hyperthreading): multiple hardware threads/core sharing resources.

If the OS flushes store buffers on context switch (for x86 – or does whatever synchronisation is needed on other archs), software threads should have the same semantics as hardware threads.

# x86-TSO vs SPARC TSO

## x86-TSO based on SPARC TSO

SPARC defined

- ▶ TSO (Total Store Order)

- ▶ PSO (Partial Store Order)

- ▶ RMO (Relaxed Memory Order)

But as far as we know, only TSO has really been used (implementations have not been as weak as PSO/RMO or software has turned those off).

- ▶ The SPARC Architecture Manual, Version 8, Revision SAV080SI9308. 1992.

<http://sparc.org/wp-content/uploads/2014/01/v8.pdf.gz> App. K defines TSO and PSO.

- ▶ The SPARC Architecture Manual, Version 9, Revision SAV09R1459912. 1994

<http://sparc.org/wp-content/uploads/2014/01/SPARCV9.pdf.gz> Ch. 8 and App. D define TSO, PSO, RMO

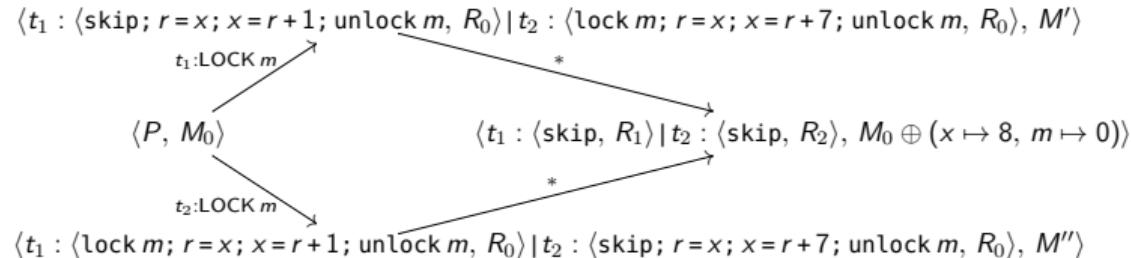

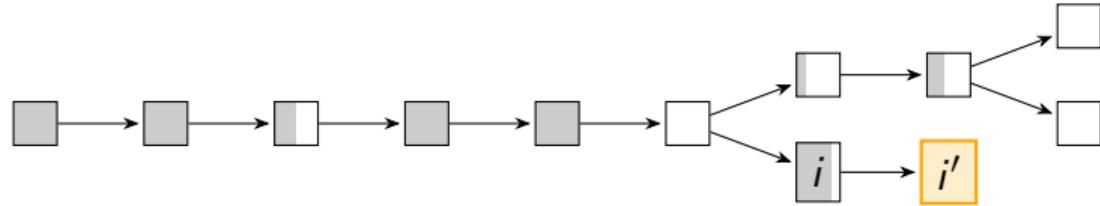

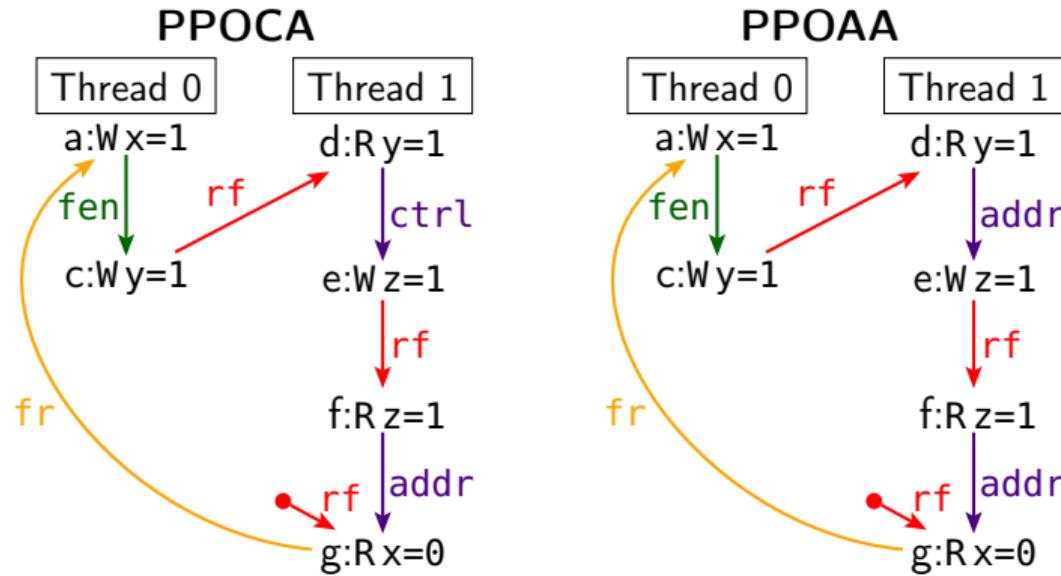

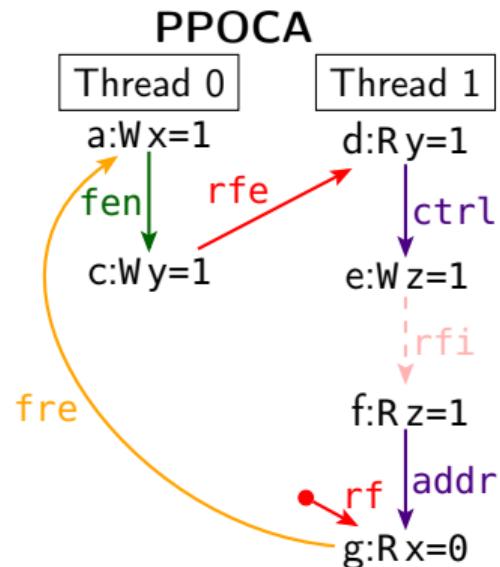

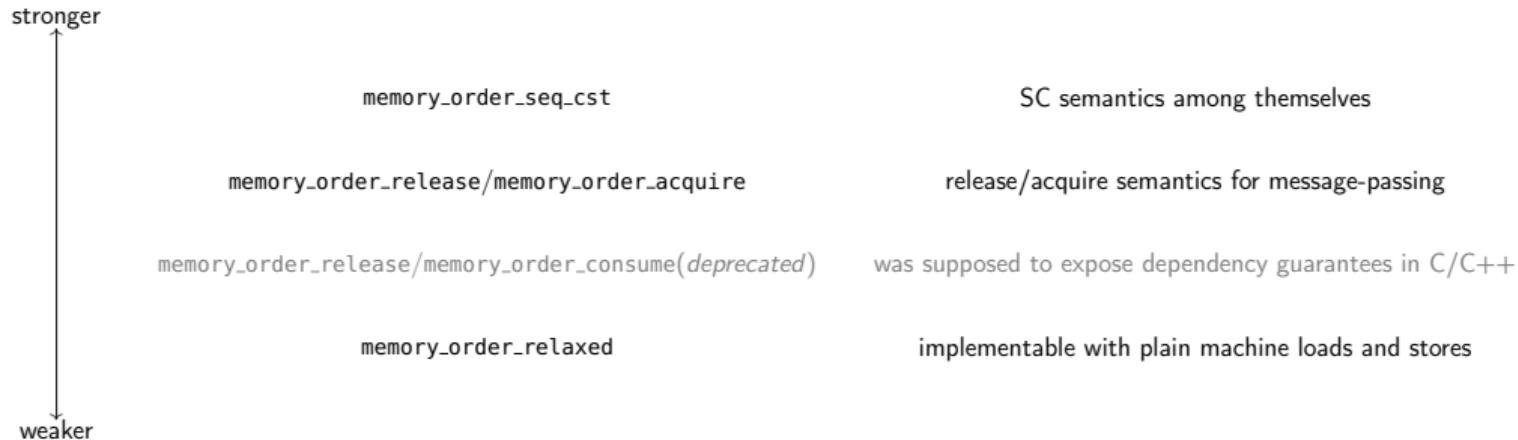

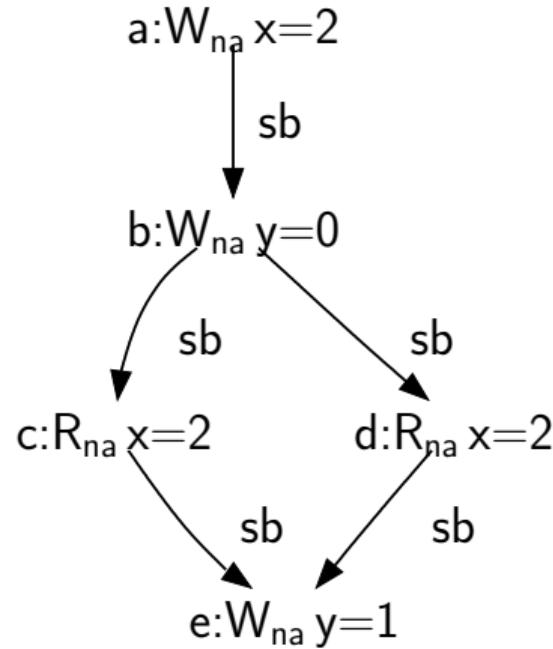

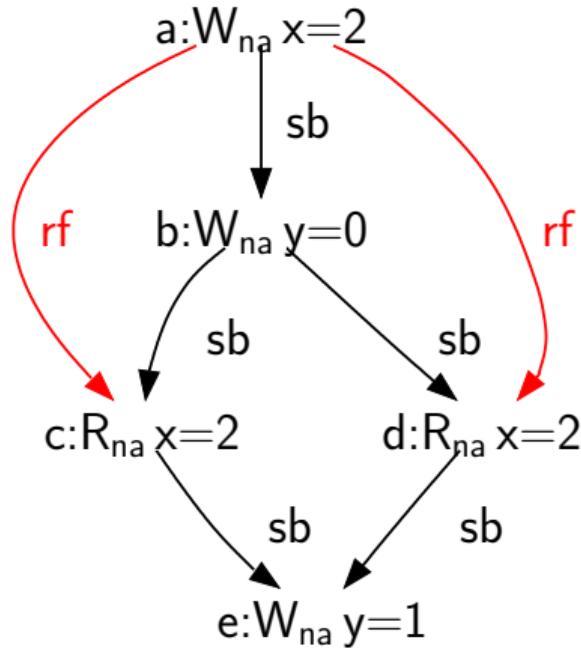

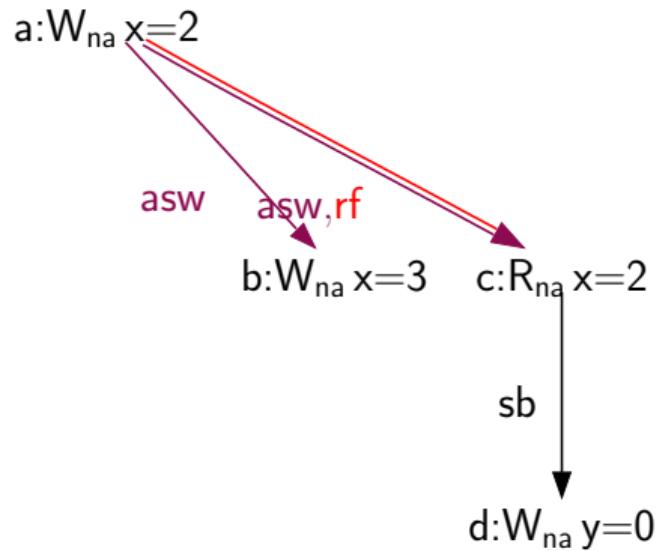

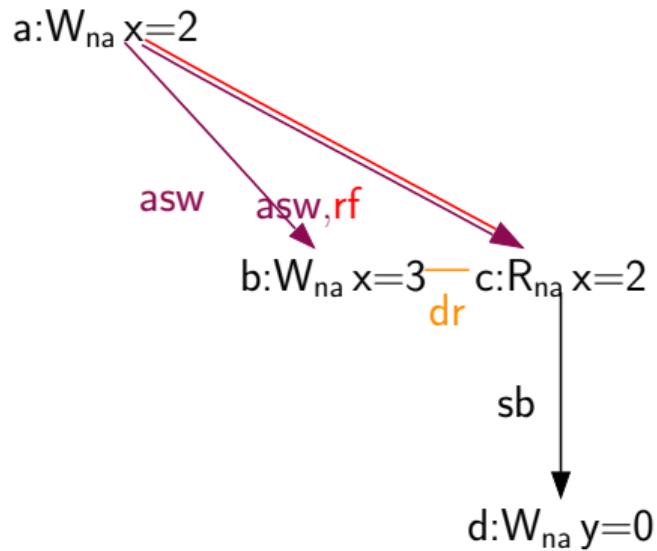

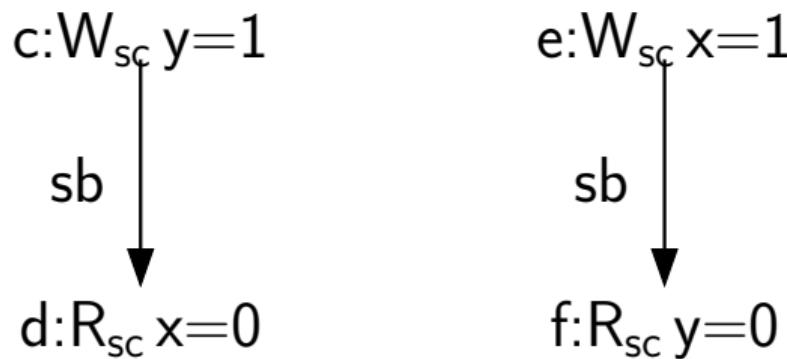

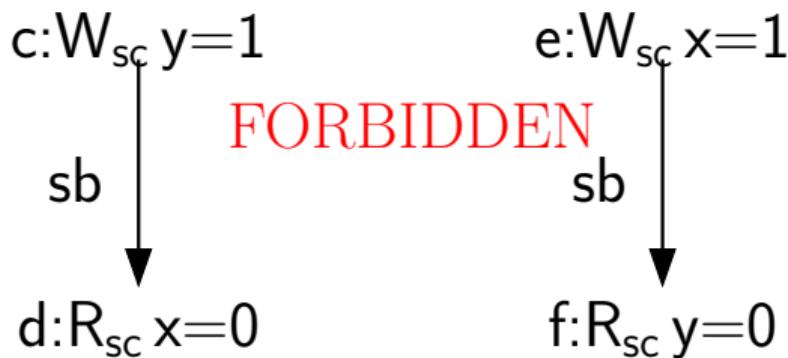

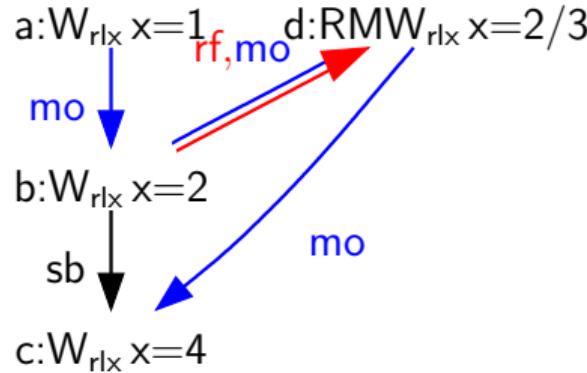

Those were in an axiomatic style – see later. x86-TSO is extensionally similar to SPARC TSO except for x86 RMW operations