## **Relaxed Memory**

Multicore Semantics course notes

Peter Sewell Shaked Flur

Working draft of 2025-02-13

### Contents

| Ac | cknowledgements                                                                     | 5                                                        |

|----|-------------------------------------------------------------------------------------|----------------------------------------------------------|

| Re | eading guide<br>Readership                                                          | <b>6</b><br>6<br>7                                       |

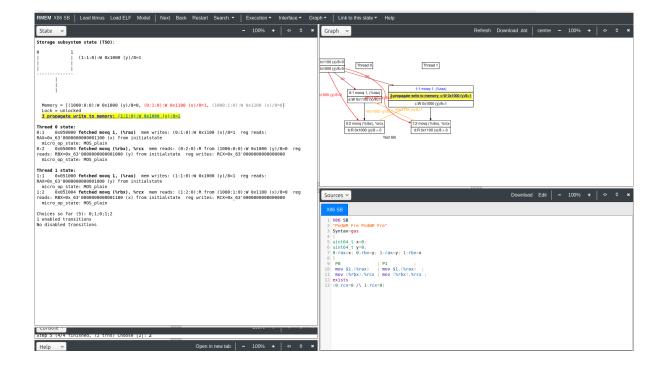

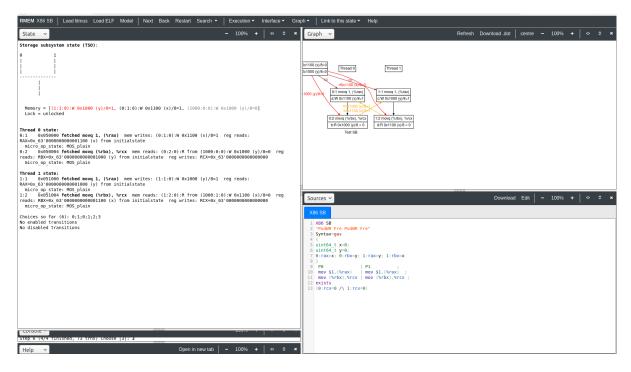

| 1  | Introduction1.1Memory                                                               | 8<br>9<br>10<br>11<br>14<br>19<br>20<br>21               |

| Ι  | SC, x86, tools, and approach                                                        | 23                                                       |

| 2  | x86 basic phenomena2.1Litmus tests and candidate executions                         | 24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33 |

| 3  | x86: some vendor documentation history         3.1       pre-IWP (before Aug. 2007) | <b>34</b><br>35<br>36<br>37<br>37<br>39                  |

4 x86-TSO: creating a good de facto standard model

| 5        | Opera   | tional and axiomatic concurrency model definitions                            | 43  |

|----------|---------|-------------------------------------------------------------------------------|-----|

| 6        |         | erationally                                                                   | 45  |

|          | 6.1     | An operational SC model                                                       | 45  |

| 7        | x86-TS  | SO, operationally                                                             | 49  |

| <i>'</i> | 7.1     | An operational x86-TSO model                                                  | 49  |

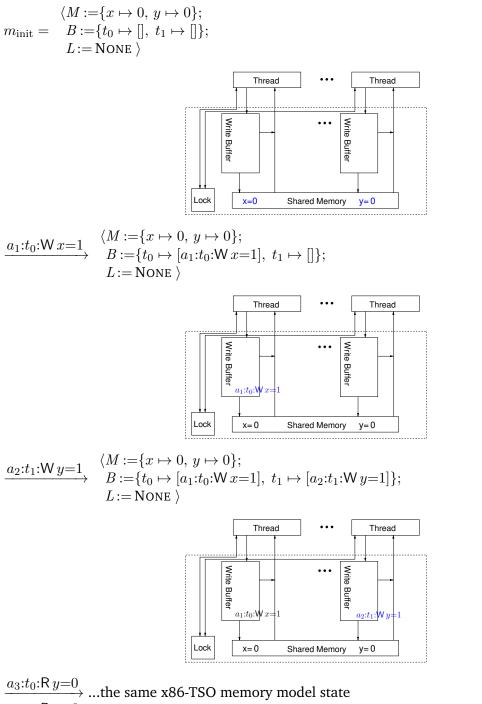

|          | 7.2     | x86-TSO operational example: SB                                               | 51  |

|          | 7.3     | x86-TSO operational example: spinlocks                                        | 53  |

|          | 7.4     | Discussion                                                                    | 60  |

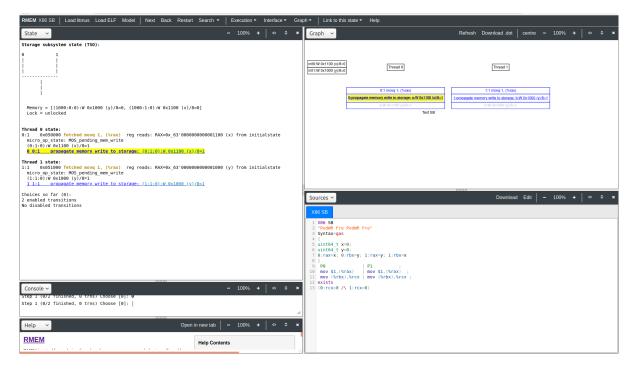

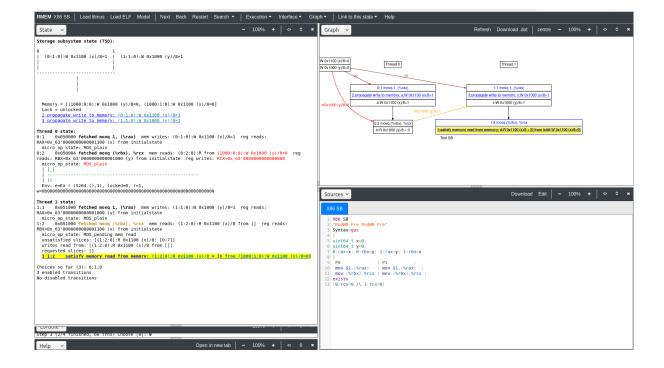

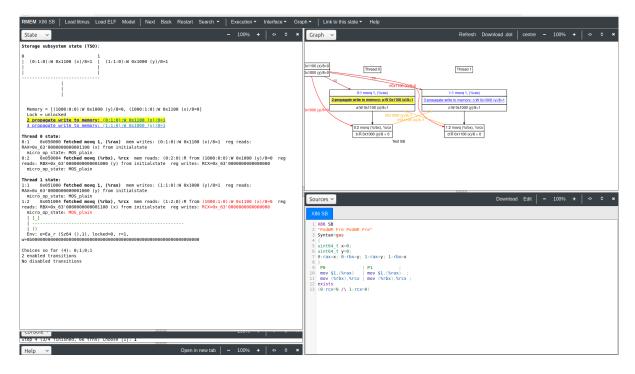

| 8        | Makin   | g operational models executable as a test oracle: RMEM                        | 63  |

| 0        |         |                                                                               | 70  |

| 9        |         | iomatically                                                                   | 70  |

|          | 9.1     | Execution graphs, formally                                                    | 70  |

|          | 9.2     | Coherence                                                                     | 72  |

|          | 9.3     | An axiomatic SC model                                                         | 80  |

|          | 9.4     | Equivalence of the operational and axiomatic SC models                        | 81  |

| 10       | x86-TS  | SO, axiomatically                                                             | 85  |

| 10       | 10.1    | Coherence in x86-TSO                                                          | 85  |

|          | 10.2    | Local ordering and the external relations                                     | 87  |

|          | 10.2    | An x86-TSO axiomatic model, without MFENCE and LOCK'd instructions            | 87  |

|          | 10.3    | x86-TSO axiomatic examples                                                    | 88  |

|          | 10.4    | Equivalence of the operational and axiomatic x86-TSO models, without MFENCE   | 00  |

|          | 10.5    | and LOCK'd instructions                                                       | 88  |

|          | 10 (    |                                                                               |     |

|          | 10.6    | Relational algebra Cat notation for axiomatic model definitions               | 89  |

|          | 10.7    | An x86-TSO axiomatic model, with LOCK'd instructions and MFENCE               | 90  |

|          | 10.8    | Equivalence of the operational and axiomatic x86-TSO models                   | 91  |

| 11       | Makin   | g axiomatic models executable: Herd and Isla                                  | 92  |

| 12       | Runni   | ng tests on hardware: Litmus                                                  | 97  |

| 13       | Test fa | milies and test generation: Diy                                               | 99  |

|          | 13.1    | Organising tests                                                              | 99  |

|          | 13.2    | Generating single tests from cycles                                           | 101 |

|          | 13.3    | Generating families of tests                                                  |     |

| 1/       | Valida  | ting the model: why should one believe it?                                    | 104 |

| 14       | 14.1    | Sound with respect to existing hardware: experimental validation              |     |

|          |         |                                                                               | 104 |

|          | 14.2    | Sound with respect to future hardware; loose enough to permit future microar- | 106 |

|          | 14.0    | chitectural innovation                                                        |     |

|          | 14.3    | Opaque with respect to hardware implementation detail                         |     |

|          | 14.4    | Complete with respect to hardware                                             |     |

|          | 14.5    | Strong enough for software                                                    |     |

|          | 14.6    | Precise and unambiguous                                                       |     |

|          | 14.7    | Clear                                                                         |     |

|          | 14.8    | Executable as a test oracle                                                   |     |

|          | 14.9    | Incrementally executable                                                      |     |

|          | 14.10   | Mathematically validated                                                      | 108 |

|          | 14.11   | Authoritative                                                                 | 108 |

|          | 14.12   | Accurately capturing the architectural intent                                 | 108 |

|     | 14.13   | Consiste  | ncy with the de facto standard                                         | . 108 |

|-----|---------|-----------|------------------------------------------------------------------------|-------|

| II  | Arm-    | A, IBM F  | Power, and RISC-V                                                      | 109   |

| 15  |         |           | m-A, IBM Power, and RISC-V relaxed concurrency                         | 110   |

|     | 15.1    |           | tures and Implementations                                              |       |

|     |         | 15.1.1    | Arm-A                                                                  |       |

|     |         | 15.1.2    | IBM Power                                                              |       |

|     |         | 15.1.3    | RISC-V                                                                 |       |

|     | 15.2    | Relaxed   | behaviour and abstract microarchitecture, informally                   |       |

|     |         | 15.2.1    | Microarchitecture optimisations and relaxed architecture specification |       |

|     |         | 15.2.2    | The pros and cons of relaxed architecture specifications               |       |

|     |         | 15.2.3    | Abstract microarchitecture – structure                                 |       |

|     |         | 15.2.4    | Abstract microarchitecture – behaviour                                 |       |

|     | 15.3    | Litmus te | ests                                                                   |       |

|     |         | 15.3.1    | Candidate executions                                                   | . 122 |

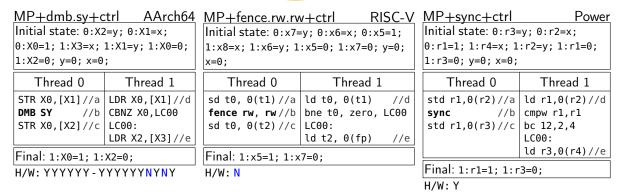

| 16  | Arm-A   | , IBM Por | wer, and RISC-V phenomena                                              | 124   |

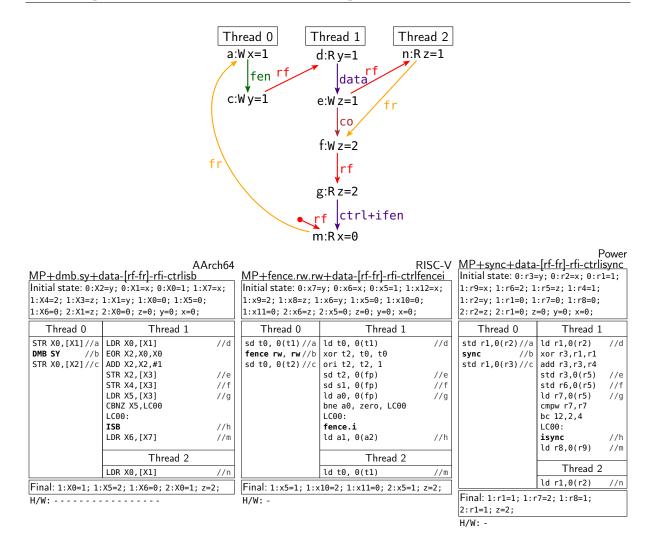

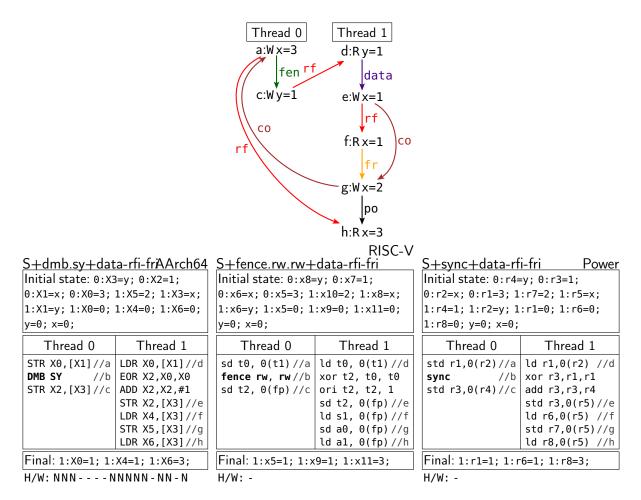

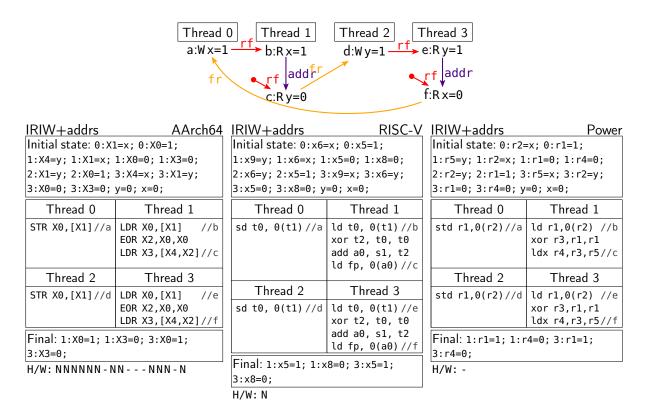

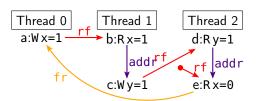

|     | 16.1    | Non-mix   | ed-size Phenomena                                                      | . 124 |

|     |         | 16.1.1    | Coherence                                                              | . 124 |

|     |         | 16.1.2    | Out-of-order execution                                                 | . 127 |

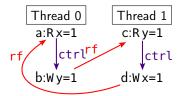

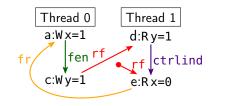

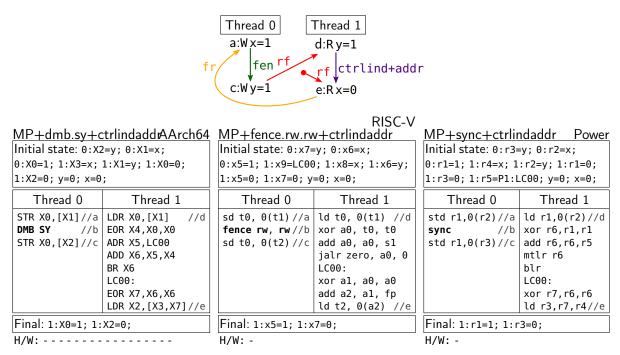

|     |         | 16.1.3    | Dependencies                                                           | . 131 |

|     |         | 16.1.4    | Speculative execution - branching                                      |       |

|     |         | 16.1.5    | Instruction Barrier                                                    |       |

|     |         | 16.1.6    | Write forwarding                                                       | . 141 |

|     |         | 16.1.7    | Speculative execution - restarts                                       |       |

|     |         | 16.1.8    | Satisfy same address reads out-of-order                                |       |

|     |         | 16.1.9    | Write forwarding from a non-speculative write                          |       |

|     |         | 16.1.10   | Multi-step read satisfaction                                           |       |

|     |         | 16.1.11   | Detour                                                                 |       |

|     |         | 16.1.12   | Write subsumption                                                      |       |

|     |         | 16.1.13   | Symbolic forwarding                                                    |       |

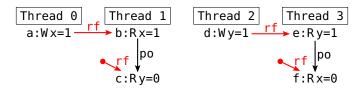

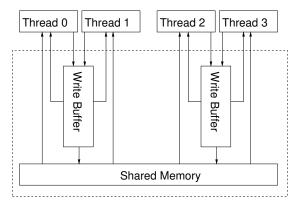

|     |         |           | Multi-Copy Atomicity                                                   |       |

|     |         |           | Atomic Memory Modification                                             |       |

|     |         |           | Release/Acquire Memory Accesses                                        |       |

|     | 16.2    |           | ize Phenomena                                                          |       |

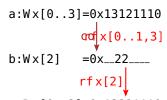

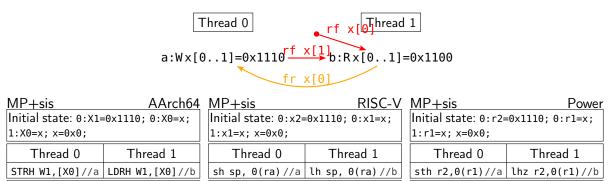

|     | 10.2    | 16.2.1    | Reading from Multiple Writes                                           |       |

|     |         | 16.2.2    | Mixed-size Coherence                                                   |       |

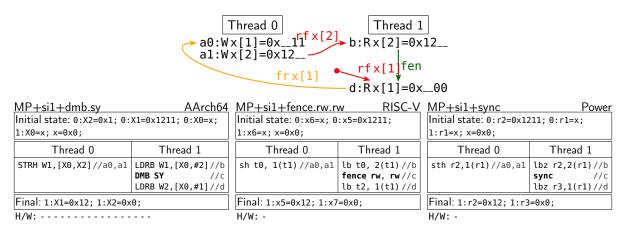

|     |         | 16.2.3    | Single-copy Atomicity                                                  |       |

|     |         | 16.2.4    | Atomicity of register accesses                                         |       |

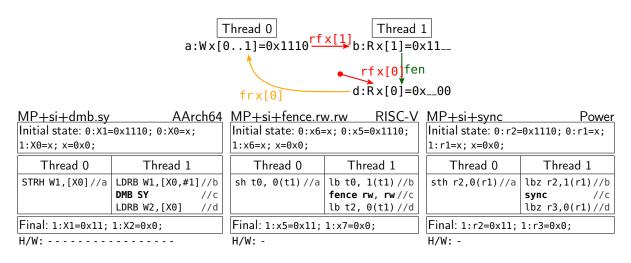

|     |         | 16.2.5    | Mixed-size Multi-copy Atomicity                                        |       |

|     |         | 16.2.6    | Mixed-size write-forwarding                                            |       |

|     |         |           |                                                                        |       |

| III | Syst    | ems con   | currency                                                               | 182   |

| IV  | Refle   | ections,  | related work, and history                                              | 183   |

| Re  | ference | es        |                                                                        | 184   |

|     |         |           |                                                                        |       |

### Acknowledgements

Many thanks are due to all those who have contributed to the research underlying this text, both in collaboration with the authors and separately, especially (in roughly chronological order) Susmit Sarkar, Francesco Zappa Nardelli, Jade Alglave, Thomas Braibant, Scott Owens, Tom Ridge, Magnus Myreen, Luc Maranget, Jaroslav Ševčík, Anthony Fox, Samin Istiaq, Mark Batty, Kathryn E. Gray, Tjark Weber, Kayvan Memarian, Sela Mador-Haim, Rajeev Alur, Milo M.K. Martin, Gabriel Kerneis, Dominic Mulligan, Ali Sezgin, Kyndylan Nienhuis, Robert M. Norton, Jon French, Alasdair Armstrong, Thomas Bauereiss, Prashanth Mundkur, Mark Wassell, Brian Campbell, Neel Krishnaswami, Ian Stark, Ben Simner, and Thibaut Pérami.

This work would not have been possible without our main industry collaborators: Derek Williams (IBM); Richard Grisenthwaite, Will Deacon, Alastair Reid, and Graeme Barnes (Arm); Hans Boehm, Paul McKenney, and other members of the C++ concurrency group; and Daniel Lustig and other members of the RISC-V concurrency group.

Thanks also to Ori Lahav and Viktor Vafeiadis for discussion of the current models for C/C++, to Paul Durbaba for his 2021 Part III dissertation mechanising the x86-TSO axiomatic/operational correspondence proof, and to many others for discussions, including: Alan Stern, Andy Glew, Anthony Williams, Clark Nelson, Dave Dice, David Christie, Doug Lea, Gil Neiger, Jasmin Blanchette, John Baldwin, John Wickerson, Keir Fraser, Konrad Slind, Lawrence Crowl, Michael Fetterman, Michael Wong, Mike Gordon, Nathan Chong, Nick Maclaren, Paul Loewenstein, Peter Dimov, Raul Silvera, Robert N.M. Watson, Warren Hunt, and William Collier.

This text is partly based on slides for the semantics part of the University of Cambridge MPhil and Part II/III course *Multicore Semantics and Programming*, given by Sewell and Pulte from 2010 to date. Thanks to all the students who have tested the exposition, and to Tim Harris who has given the Concurrent Algorithms part, which is not covered here.

This work was funded in part by UK Research and Innovation (UKRI) under the UK government's Horizon Europe funding guarantee (ERC AdG SAFER, EP/Y035976/1, Sewell). This work has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (ERC AdG ELVER, grant agreement No 789108, Sewell). This work was partly supported by EPSRC grants EP/K008528/1 (Programme Grant REMS: Rigorous Engineering for Mainstream Systems), EP/F036345 (Reasoning with Relaxed Memory Models), EP/H005633 (Leadership Fellowship, Sewell), and EP/H027351 (Postdoctoral Research Fellowship, Sarkar); the Scottish Funding Council (SICSA Early Career Industry Fellowship, Sarkar); an ARM iCASE award (Pulte); ANR grant WMC (ANR-11-JS02-011, Zappa Nardelli, Maranget); EPSRC IAA KTF funding; Arm donation funding; IBM donation funding; ANR project ParSec (ANR-06-SETIN-010); and INRIA associated team MM. This work was supported in part by the CIFV project sponsored by the Defense Advanced Research Projects Agency (DARPA) and the Air Force Research Laboratory (AFRL), under contract FA8650-18-C-7809. The views, opinions, and/or findings contained in this paper are those of the authors and should not be interpreted as representing the official views or policies, either expressed or implied, of the Department of Defense or the U.S. Government.

### Reading guide

#### Readership

Relaxed memory is both technical and pervasive, cutting across many areas and communities. We aim for this text to be broadly useful to all these groups:

- hardware designers and validation engineers, for building processors that conform to a specific concurrency model;

- programming language implementers, for building language implementations that conform to a specific programming language model, above one or more architecture models;

- concurrent programmers, for writing software that is correct above the underlying architecture or language-level model;

- hardware architects and programming language designers, for precisely specifying the allowed behaviour of their hardware architectures and programming languages;

- semantics and verification researchers, for building theory and tools to reason about concurrent hardware and software with respect to these models;

- advanced undergraduate and postgraduate students; and

- those who teach this material.

It cuts across microarchitecture, architecture, programming languages, concurrent algorithms, concurrent programming, and mathematical semantics. Some background in any of these would help, but very few readers will have background in all of them, so we have tried to write in a way that will make sense to anyone.

To precisely define the allowed behaviour of each concurrency model, we use some discrete mathematics that, although simple, may not be familiar for all readers. We include brief introductions to the notation as we go, to make this somewhat self-contained, but it's designed to still make sense if one skips over the more mathematical parts.

Relaxed memory does involve quite a number of subtle phenomena, and not all readers will need to know about all of them. This is designed to serve both as a tutorial, introducing the most important issues first, and as a reference, covering the phenomena and models in detail. We recommend reading the former chapters first, without going into all of the latter, and then going back to those as needed.

#### Structure

Chapter 1 gives a brief and informal introduction to relaxed-memory concurrency, in architectures and programming languages, and to the role of precise models in defining what concurrent behaviour is allowed by particular abstractions.

We begin the main text in Part I with the simple (but normally unrealistic) sequential consistency model (SC), and the x86 architecture model. x86 has a simpler and stronger model (less relaxed, closer to SC) than the other main architectures we consider, so it provides a good context to see some of the basic phenomena and the techniques and tools we use for modelling and validation, before we get to the complexities of those other architectures.

In Part II we continue with Arm-A, IBM Power, and RISC-V. These are broadly similar to each other, though not identical; they are much more relaxed than x86.

In both Part I and Part II we start with the relaxed-memory phenomena that the architecture exhibits, explaining them informally with litmus-test examples, and discussion of how the observable behaviour might arise from microarchitectural design choices. We then describe how one can express the architectural intent in general, with precise models that define what behaviour is allowed for arbitrary code. We do this using models in two complementary styles: *abstract-microarchitectural operational models*, that let one explain and understand the behaviour based on intuitions from hardware implementation, and *axiomatic models*, that more concisely (but perhaps less intuitively) define the allowed behaviour. Both are expressed mathematically, but we explain the small amount of required maths along the way, to make this as broadly accessible as possible.

In both these parts we focus just on the "user" architecture, including loads, stores, readmodify-write operations, barriers, and other synchronisation mechanisms, on coherent writeback memory, sufficient for many concurrent algorithms. This excludes all "systems" aspects: other memory types and "non-temporal" operations, self-modifying code and instruction/datacache maintenance, virtual memory and TLB maintenance, exceptions and interrupts, and device memory. Some of these are now reasonably well-understood for some architectures, and we may cover them in a future revision; others remain open research questions.

For now, the text covers only this "user" architecture-level concurrency. Future versions may also cover programming language concurrency, "systems" architecture-level concurrency, and the history of the subject.

#### Use as course material

As mentioned, this text is partly based on the semantics part of the University of Cambridge Computer Laboratory course *Multicore Semantics and Programming*. This is both a masters-level course, in the MPhil in Advanced Computer Science, and a 3rd- or 4th-year undergraduate course (Part II/Part III in Cambridge terms). The aim of the semantics part is to give the students a good understanding of the basic architecture-concurrency phenomena and how they are captured in operational and axiomatic models, along with the general issues in programming-language relaxed concurrency and a briefer introduction to the C/C++ model. The slides are available online. The semantics part of the course is 5 two-hour blocks, divided into 10 one-hour sessions roughly as below.

| 1–2 | Chapters 1–5:  | introduction and x86 basic phenomena                                |

|-----|----------------|---------------------------------------------------------------------|

| 3–4 | Chapters 6–10: | operational and axiomatic models for sequential consistency and x86 |

| 5   | Chapters 11–14 | 4:validating the models                                             |

| 6   | Chapter 16:    | Arm-A, IBM Power, and RISC-V – the basic phenomena                  |

| 7   | Chapter 16:    | Arm-A, IBM Power, and RISC-V – a sample of further subtleties       |

| 8–9 |                | Arm-A, IBM Power, and RISC-V – operational and axiomatic models     |

| 10  |                | an introduction to programming-language relaxed concurrency         |

|     |                |                                                                     |

One could also pull out a briefer treatment, e.g. for a one-hour lecture within a computer architecture, concurrent programming, and semantics course.

### Chapter 1

### Introduction

This text addresses a fundamental question for concurrent programming: *what is the programmer-visible behaviour of memory*? We look at this for several mainstream processor architectures: x86, Arm-A, IBM Power, and RISC-V; and for higher-level programming languages, especially C and C++. We discuss the main phenomena by example, explaining how they arise from microarchitecture and compiler implementation optimisations (though this is not a text on hardware or compiler design); show how one can precisely specify real-world *relaxed memory models*, in operational and axiomatic styles, that define the allowed behaviour of concurrent programs; discuss how models can be validated and implementations tested; and consider the relationships between models. These models give a solid basis for high-performance concurrent programming, criteria for hardware and compiler implementation correctness, and a foundation for semantic reasoning and verification tool building.

This is largely based on a line of research from 2008–2024 by the authors and many others, including key industry colleagues; it builds also on much earlier research. We mention a few key points of this context as we go along, but the main narrative describes the current state of the art, as we understand it, not the historical development. In a future version we aim to include a more detailed survey of the related work.

### 1.1 Memory

The abstraction of *memory*, and the organisation of computing devices into separate memory and processing components, dates back to the beginning of general-purpose computing. In 1837 Charles Babbage, describing his planned but unrealised Analytical Engine, wrote:

The calculating part of the engine may be divided into two portions

- 1st The Mill in which all operations are performed

- 2nd The Store in which all the numbers are originally placed and to which the numbers computed by the engine are returned.

[On the Mathematical Powers of the Calculating Engine, Charles Babbage [44]]

Here the store was to be able to hold 1000 numbers, each 40 decimal digits, while the mill was to be able to compute the four arithmetic operations and comparisons, controlled by a program on punched cards. Alan Turing's 1936 mathematical model of general-purpose computing [152], intended to characterise what is in principle computable, had an unbounded *tape*, divided into squares each holding one of a finite number of symbols, an *m-configuration* from a finite set of states, and a finite table determining the steps of the machine. The late 1940s and early 1950s saw the first general-purpose stored-program electronic computers, including Mauchly and Eckert's EDVAC (the design of which is detailed in von Neumann's *First draft of a report*

*on the EDVAC* [113, 153]), Turing et al's ACE [151, 159], the Manchester Baby [158], and the University of Cambridge EDSAC [157]. Each of these executed instructions sequentially in the order they were given in the program, issuing each required memory access to the memory and waiting for the memory to complete its operation before continuing.

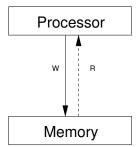

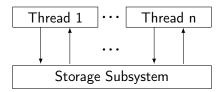

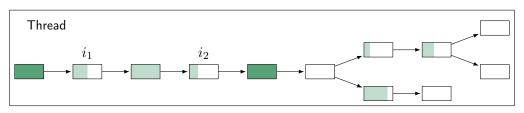

Semantically, these are all straightforward: one can regard memory as an array or sequence of values, with the processor taking a step per instruction, in program order, and each step reading or writing (one location of) memory if necessary. Informally, this can be depicted as below.

(Properly characterising early machines involves many other questions, e.g. whether program and data memory are distinguished, and whether memory addresses must be static in the program or can be dynamically computed, but those are not relevant here.)

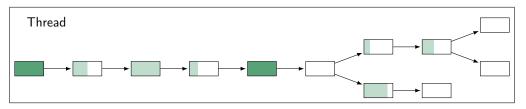

### 1.2 Out-of-order and speculative uniprocessors

Early high-performance machines in the 1950s and 1960s, such as the ILLIAC II, IBM Stretch, CDC 6600, and IBM System/360 Model 91, introduced a range of sophisticated hardware execution optimisations: *pipelined execution*, to simultaneously execute the successive stages of instructions, *superscalar execution*, to simultaneously dispatch multiple instructions to different execution units, *out-of-order execution*, to let program-order-later instructions go ahead when some of their program-order-predecessors are blocked waiting for some resource, such as a memory read, and *speculative execution*, to let instructions go ahead before it is known for sure that they will be reached, with roll-back as needed.

These let the hardware automatically extract some of the instruction-level parallelism (ILP) implicit in the instruction stream, but, at least in that uniprocessor context, they preserved the simple sequential programmer's model shown above: the hardware could do some out-of-order and speculative execution, but it would prevent or roll back anything that violated that model, so the programmer could still assume that instructions were executed one at a time in program order (apart from some imprecise exception cases).

### 1.3 Shared-memory multiprocessors

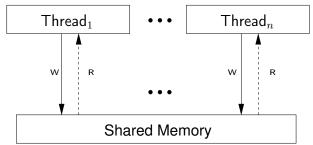

Shared-memory *multiprocessors*, with multiple processors that can interact via a shared memory, date back at least to the 1962 Burroughs D825, and to the 1972 IBM System 370/158MP. For many years they remained of relatively niche interest, as continued sequential performance increases came from smaller transistor sizes, increased clock frequencies, and better extraction of instruction-level parallelism by advanced processor designs. In the early 2000s those increases slowed, as they reached power-density, scaling, and ILP limits, and multiprocessors started to become commonplace, e.g. with the 2005 introduction of the Intel Core 2 Duo. Now they are ubiquitous.

Shared-memory concurrency has thus long become mainstream — but understanding, designing, and programming concurrent systems remains very hard. We focus here on the sharedmemory abstractions provided by general-purpose processors and programming languages, but similar issues arise in (and similar techniques and models can be used for) the abstractions provided by GPUs and other accelerators, by supercomputer interconnects, and in datacentre-scale and internet-scale distributed databases: wherever one needs multiple concurrent computation over the same shared data, and the need for performance means that everything cannot be simply synchronised.

Sometimes shared memory is presented in opposition to message-passing models of concurrency, but in reality the two are tightly intertwined. Modern high-performance interconnects provide a programmer-level shared-memory abstraction above message-passing hardware, and distributed databases provide a shared-memory abstraction above internet message passing.

### 1.4 Sequential consistency

The most obvious semantics for a shared-memory multiprocessor is *sequential consistency*, as articulated in 1979 by Lamport [97]. A machine has a sequentially consistent (SC) shared memory if:

the result of any execution is the same as if the operations of all the processors were executed in some sequential order, respecting the order specified by the program

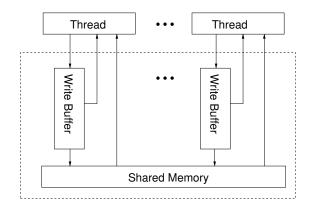

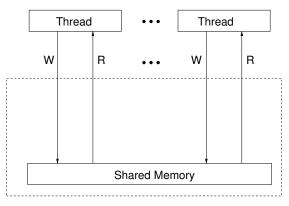

or, in other words, if each processor appears to execute in order, with their effects on memory interleaved in some arbitrary way. One can informally depict the programmer's model for such a machine as below.

Much previous theory research has assumed this SC model, and probably many programmers still do. To the best of our knowledge, the Burroughs D825 did behave like that, in the 1960s, but more recent machines do not. To investigate how modern multiprocessors actually behave, we start with a very simple example, of a shared-memory program intended to enforce mutual exclusion between two critical sections:

| Initial state: x=0; y=0;                |                                         |

|-----------------------------------------|-----------------------------------------|

| Thread 0                                | Thread 1                                |

| x=1;                                    | y=1;                                    |

| <pre>if (y==0) {critical section}</pre> | <pre>if (x==0) {critical section}</pre> |

For the moment, we'll use a C-like pseudocode and leave the per-thread semantics implicit, just regarding each thread as an automoton (a labelled transition system) that performs a sequence of memory accesses. This example is already highly simplified with respect to practically useful algorithms for mutual exclusion: it's a one-shot algorithm (not supporting repeated use), it's for exactly two threads, it's inline rather than abstracted into a library, and it may have poor performance and fairness properties – but none of that is relevant right now.

Intuitively, one might think that the algorithm is correct iff the two threads cannot both be executing their critical sections at the same time. However, that is a very intensional property – it's phrased in terms of the internal details of how execution happens, which is not directly observable, rather than the extensional programmer-visible behaviour – and it refers implicitly to a notion of global time, which we will see is problematic. We therefore simplify it still further, replacing the conditionals and their critical-section bodies with just reads of the shared variables:

| Initial state: x=0; y=0; |          |  |

|--------------------------|----------|--|

| Thread 0                 | Thread 1 |  |

| x=1;                     | y=1;     |  |

| r0=y                     | r1=x     |  |

(writing r0 and r1 for thread-local variables) and ask whether a final state with r0=0 and r1=0 is possible, instead of whether the threads can be executing their critical sections at the same time. Small concurrency test cases like these are known as *litmus tests*, as they indicate what behaviour a model or implementation might allow.

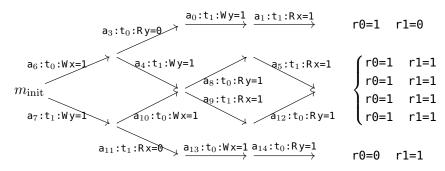

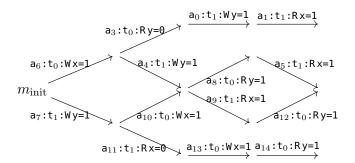

For such a simple example, one can enumerate all the possible interleavings in the SC model, with the final states of each. There are six possible SC interleavings – the six possible paths through the transition system below – leading to three distinct final states:

The initial memory state  $m_{init}$  has x=0 and y=0, and each memory read or write transition is labelled with a unique event ID  $a_i$ , its thread  $t_j$ , and its address and value. We elide the details of the intermediate memory states. None of the final states have r0=0 and r1=0, so in the SC model this code does enforce mutual exclusion. In the SC model one can also reason more briefly: because in any SC execution there must be a total order over all the operations, and each thread executes in program order, either the x=1 or y=1 must go first, then because there are no other writes, the other thread's read of that must see that value, so one cannot end up with r0=0 and r1=0.

### 1.5 Running the example experimentally, on hardware

Now we'll run the example on some modern multiprocessors, to see experimentally what actually happens. To focus on the behaviour of the hardware, rather than the combination of the hardware and some compiler, we'll first rewrite the test in assembly code, to ensure that we know exactly what is being tested. Here are x86 and Arm-A (AArch64) versions of the test:

|                                      |                      | <u>SB</u>      |              |                 | <u>AArch64</u> |

|--------------------------------------|----------------------|----------------|--------------|-----------------|----------------|

| <u>SB</u>                            | x86                  | Initial state: | 0:X3=y; 0:X  | 1=x; 0:X0=1; 0: | :X2=0;         |

| Initial state: 0:rax=0; 1:ra         | x=0; y=0; x=0;       | 1:X3=x; 1:X1=  | y; 1:X0=1; 1 | L:X2=0; y=0; x= | 0;             |

| Thread 0                             | Thread 1             | Threa          | d 0          | Thread          | d 1            |

| movq \$1, (x) //W x=1 m              | ovq \$1, (y) //W y=1 | STR X0,[X1]    | //W x=1      | STR X0,[X1]     | //W y=1        |

| <pre>movq (y), %rax//R rax=y m</pre> | ovq(x),%rax//Rrax=x  | LDR X2,[X3]    | //R R2=y     | LDR X2,[X3]     | //R R2=x       |

| <pre>Final: 0:rax=0; 1:rax=0;</pre>  |                      | Final: 0:X2=   | =0; 1:X2=0;  |                 |                |

**Assembly syntax** In these architecture-level litmus tests, there is an assembly language program for each hardware thread, which run concurrently. Each per-thread program is a list of assembly instructions, which map fairly straightforwardly onto the machine-code instructions that processors actually execute, and labels that identify program points. For x86, two styles of syntax are in widespread use: *Intel syntax* (used in the Intel manuals) and *AT&T* syntax (dominant in Unix environments). These x86 litmus tests use a variant of the latter: the movq \$1, (x)

is a 64-bit (quad-word) store of constant 1 to location x and movq (y),%rax is a 64-bit load of location y into 64-bit register rax. Intel syntax and the Arm-A syntax we use have the opposite argument order to that, destination before source. In the Arm-A test, which uses the Arm-A AArch64 64-bit instruction set, M0V W0,#1 copies the constant 1 into register R0. The AArch64 general-purpose registers R0...R30 can be referred to either as 64-bit registers, using X0...X30, or 32-bit registers, using W0...W30. These names determine the sizes of stores and loads: the STR W0, [X1] stores the low-order 32-bit contents of R0 into the memory location addressed by R1, while the LDR W2, [X3] loads a 32-bit value from the memory location addressed by R3 into R2, zero-extending it.

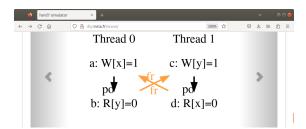

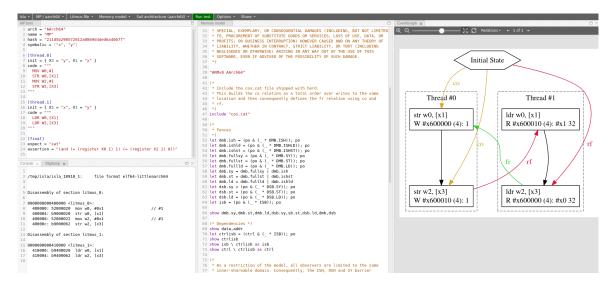

Then we need a test harness, to run the test repeatedly and log the outcomes. We'll use the litmus7 tool from the herdtools7 tool suite by Alglave and Maranget [32]. To install litmus7:

- 1. install the opam package manager for OCaml: https://opam.ocaml.org/

- 2. opam install herdtools7 (docs at diy.inria.fr)

This uses a common format for tests, shared with the other tools of that suite, diy7 and herd7, and with the rmem [132] and isla-axiomatic [40] tools by Flur et al. and Armstrong et al.; we'll return to all these later. In that format, the x86 version of this test can be written as SB.litmus:

```

1 X86_64 SB

2

"PodWR Fre PodWR Fre"

3

{

4

uint64_t x=0; uint64_t y=0;

5

uint64_t 0:rax; uint64_t 1:rax;

6 }

7

P0

| P1

;

8

| movq $1,(y)

movq $1,(x)

;

9

movq (y),%rax | movq (x),%rax ;

10 exists (0:rax=0 /\ 1:rax=0)

```

Here the initial X86\_64 specifies the test architecture, lines 3–6 define the initial state of memory (x and y) and registers (0:rax and 1:rax for the rax register of hardware threads 0 and 1 respectively), and lines 7–9 give a sequence of x86 assembly instructions for two threads, P0 and P1. Line 10 specifies the condition on the final state that we're interested in.

Running that with litmus7 executes the test in an aggressive test harness: it converts the test to actual assembly, runs many instances of the test ( $10^6$  times by default), iterates in randomised orders over arrays for x and y instead of scalars, roughly synchronises the start times of the threads in each instance, and so on. The embedded assembly kernel it actually generates for the x86 version of this test is below – one can see that the accesses to x and y use an indexed addressing mode to allow convenient iteration over arrays of locations.

```

[...]

Generated assembler

#START _litmus_P1

movq $1,(%r9,%rcx)

movq (%r8,%rcx),%rax

#START _litmus_P0

movq $1,(%r8,%rcx)

movq (%r9,%rcx),%rax

[...]

```

It logs a histogram of the observed final values. For a typical x86 processor we might see something like this, though the exact numbers will vary:

```

$ litmus7 SB.litmus

[...]

Histogram (4 states)

14 *>0:rax=0; 1:rax=0;

499983:>0:rax=1; 1:rax=0;

499949:>0:rax=0; 1:rax=1;

54 :>0:rax=1; 1:rax=1;

[...]

Observation SB Sometimes 14 999986

[...]

```

Here we see that in most executions it appears that Thread 0 runs entirely before Thread 1 or vice versa, and in a few executions (54 out of  $10^6$ ) it appears that the two stores happened before the two loads. Those are all allowed by the SC model. But in 14 out of  $10^6$  executions, we see the non-SC behaviour in which both threads' reads see 0. This is a rather common non-SC behaviour; to see rarer non-SC behaviours one might need to run tests for  $10^9...10^{11}$  executions, and tune the litmus test harness with its command-line options.

If we run an Arm version of the test we see similar results:

```

Histogram (4 states)

7136481 *> 0:X2=0; 1:X2=0;

596513783:> 0:X2=0; 1:X2=1;

596513170:> 0:X2=1; 1:X2=0;

36566 :> 0:X2=1; 1:X2=1;

[...]

Observation SB Sometimes 7136481 1193063519

```

(7e6 in 1.2e9, on an Apple-designed Armv8-A SoC, Apple A10 Fusion, in an iPhone 7).

A priori, there are many possible explanations for the mismatch between these experimental observations and the SC model:

- 1. There is an error in the test i.e., it isn't testing what we think it is. It is quite easy to make errors when hand-writing subtle tests, so this needs care, but if there's a discrepency between the experimental observations and the model, then that's an issue exposed by the test as written irrespective of what we think it's testing.

- 2. There is an error in the test harness. This is certainly possible, but litmus7 is reasonably mature, and mismatches can almost always be traced to another cause. One can also gain some confidence in the harness from the fact that in extensive use for many tests it does give the expected results.

- 3. There is an error in the surrounding OS that is corrupting the test results. This is possible in principle, but we have not seen it in practice. If this were an issue one would expect to probably see it even for straightforward tests, which we do not.

- 4. There is an error in the hardware processor design. This is rare but certainly happens. Over the years this testing has identified a number of hardware errata, in core designs from several vendors.

- 5. There is a manufacturing defect in this particular instance of the processor. One can check this by contrasting experimental data from different instances of the same processor.

- 6. There is an error in our calculation of what the model allows for the test. For subtle tests and models this becomes challenging to do reliably by hand, especially for large numbers of tests, so one would typically use tools (such as rmem, isla-axiomatic, or herd) to do this. Of course, one then has to be concerned with the possibility of bugs in those tools.

7. There is an error in the model. In this case this is the correct explanation:

#### Sequential Consistency is not a good model for x86 or Arm processors.

In fact, SC is not a good model for any major multiprocessor architecture, including IBM Power, RISC-V, SPARC, or Itanium, or for major programming languages, including C, C++, and Java. Instead, all these have some form of *relaxed memory model* (or *weak memory model*), allowing some non-SC behaviour. In the remainder of this text we'll explain this, explore what programmers can actually depend on, and establish good models, for x86, Arm-A, IBM Power, and RISC-V.

As we shall see, hardware relaxed-memory behaviour arises from microarchitectural optimisations, including out-of-order and speculative execution, and sophisticated storage hierarchies and cache protocols, and programming-language relaxed-memory behaviour arises from the combination of this and established compiler optimisations. These hardware and software optimisations aim to leave the observable sequential behaviour unchanged from what one would expect in a straightforward in-order design, but some change the observable behaviour of concurrent code.

### **1.6** Architecture specifications

To understand what it means to be a "good model", and how we can conclude that SC is not a good model for x86 or Arm, we have to understand clearly what processor *architectures* are, how they relate to processor *implementations*, and what properties a good architecture definition should have.

Each specific processor implementation, such as an Intel i7-7700K, an AMD Ryzen 7 1800X, a Qualcomm Snapdragon 865, a Samsung Exynos 990, or an IBM Power 9 Nimbus, includes cores based on a specific *microarchitecture* and detailed design. We cannot use this internal structure of an implementation as a programming model: it is far too complex, it is generally commercially confidential, and it is too specific – most software has to run correctly on a range of similar implementations, past, present, and future, not just on one specific hardware implementation.

Processor implementations are grouped in families, e.g. the many variants of x86 processors developed by Intel, AMD, and VIA, and the many variants of Arm-A processors developed by Arm and its architecture partners (Apple, Qualcomm, Nvidia, Samsung, etc.). An *architecture specification* aims to define an envelope of the *programmer-observable behaviour* of all members of such a family: the set of all behaviour that a programmer might see by executing multi-threaded programs on any implementation of that family and examining the results. It thereby defines the hardware/software interface, serving both:

- 1. as a criterion for correctness of hardware implementations: any observable behaviour of any conforming hardware implementation should be within that envelope; and

- 2. as a specification of what programmers can depend on: they should be able to assume that any behaviour outside that envelope does not occur.

Architectures have to be *loose* specifications, to allow runtime variations in behaviour for each single implementation (e.g. due to differences in timing), and to accomodate the observable variations arising from different microarchitectural design choices among current, past, and future implementations. As we shall see experimentally, these differences can be quite substantial. For both reasons, they typically constrain only "functional correctness" properties, not timing and performance behaviour, as those can vary widely within and between implementations (though this leads also to the possibility of side-channel attacks).

This looseness makes software development challenging: in principle one might think that programmers should and can "program to the architecture", but normal software development

relies on testing software running on specific processor implementations. The runtime variations may mean that program bugs are not exposed in some particular test runs, and testing may be done on a specific implementation which may not exhibit some architecturally allowed behaviour that other implementations do or will exhibit. This increases the need for models that one can reason about mathematically, to ensure (at least for critical software) that all cases are covered.

The main architecture specifications are defined by industry vendors or groups, and published as pdf documents. Intel and AMD produce x86 processors, as described in their

- Intel 64 and IA-32 Architectures Software Developer's Manual [68] and

- AMD64 Architecture Programmer's Manual [17].

For our purposes these effectively define a single architecture, though the documents differ. VIA also produce x86 processors.

Arm define three main architectures, A-Profile (for applications), M-profile (for microcontrollers), and R-profile (for real-time). We focus on the first, as described in their

• Arm Architecture Reference Manual, for A-profile architecture [15].

Arm design specific cores (e.g. the Cortex-A76), which other vendors licence and integrate into SoCs (e.g. the Samsung Exynos 990). Arm also licence the architecture itself, allowing other architecture-partner vendors to design their own conforming cores (e.g. the Qualcomm Kryo).

The IBM Power architecture specification is now maintained by the OpenPOWER Foundation:

• Power ISA Version 3.1C [80].

This is the architecture used for the IBM POWER10 processor.

The RISC-V architecture is defined by the RISC-V International organisation (formerly the RISC-V Foundation):

- The RISC-V Instruction Set Manual Volume I: Unprivileged ISA [128]

- The RISC-V Instruction Set Manual Volume II: Privileged Architecture [127]

with many vendors and academic groups designing RISC-V implementations.

There are, and have been, many other important multiprocessor architectures, of course. Some have had interesting or influential relaxed-memory behaviour or specifications, notably SPARC, Alpha, and Itanium, and we will refer to them along the way, but we focus on the above currently dominant architectures for application and server-class general-purpose processors.

Each architecture definition is factored into several parts. The largest is typically the definition of the encoding and sequential behaviour of individual instructions, the *instruction-set architecture* (ISA), which is typically intricate but semantically relatively straightforward. Then there is the *concurrency architecture*, defining how instructions in different hardware threads interact with each other and with whatever mechanisms are provided for cache management. The latter is our focus here, along with the interaction between these two. Historically, most architectures have defined both parts in prose text, often with informal pseudocode for instruction behaviour.

Architectures also change over time, of course (each of the above exists in a sequence of versions) but this tends to happen more slowly than the development of new processor implementations. It usually aims to ensure backwards compatability, so that code written for one version, that should run correctly on conforming implementations of it, will also run correctly on conforming implementations of a newer version. In some cases one is also concerned with the converse, e.g. where a range of implementation and architecture versions co-exist within the

same software ecosystem. Major changes to the concurrency models are relatively rare; we will discuss a few important cases below.

All this might lead one to think that an architecture specification cannot be "correct" or "incorrect" – that each is what it is, as defined by the organisation in control of it. In practice, however, there is a delicate interplay between these specifications and the de facto standard of the hardware implementations that exist, or that are being designed. There are many properties that a good architecture specification should have, which we now discuss.

**Sound with respect to existing hardware** An architecture specification should be *sound* with respect to current implementations: it should admit all the behaviour that they can exhibit. Cases where this is found not to hold, for implementation behaviours that are deemed erroneous, are often documented as processor errata, but in some cases the architecture is loosened to accommodate some important (and impractical to change) implementation. Implementations often allow some boot-time configuration that allows specific optimisations to be turned off or simplified, which sometimes allows errata to be worked around.

In principle, soundness with respect to a particular hardware implementation could be established by mechanised mathematical proof of the correctness of that implementation, say down to the RTL level. In practice, that is still infeasible for full-scale architectures and implementations (though see e.g. [85] for recent work in that direction), and one instead gains partial confidence by extensive testing. Test results can conclusively demonstrate unsoundness, however – as we just did for the hypothesised SC model for x86.

**Sound with respect to future hardware** An architecture should also be loose enough to permit future microarchitectural innovation. That is hard to predict, of course, so this creates an incentive for the architecture to be as loose as possible, which can be in tension with the need for it to be strong enough for software and simple enough to understand.

**Opaque with respect to hardware implementation detail** In general an architecture should not unnecessarily expose any microarchitectural implementation detail, to keep the programmer's model simple, to avoid over-committing to some specific implementation and thereby excluding future improvements, to avoid skewing the thinking of hardware implementors, and to avoid revealing confidential information.

**Complete with respect to hardware** Architectures do *not* aim to be complete with respect to hardware, i.e. to capture all the functional properties of programmer-observable behaviour for specific implementations, for exactly the reasons above that mean that they have to be loose specifications.

**Strong enough for software** In the other direction, an architecture specification should be *strong enough* to support the intended corpus of existing software, and all desired programming idioms. A specification that allowed arbitrary behaviour would be trivially sound but not useful.

Showing rigorously that an architecture is strong enough to be useful is even more challenging than proving that one is sound with respect to a hardware implementation. One would like to argue that it is strong enough to support correctness proofs of all the key software that should run above it, but that is very far from the state of the art – and essentially all software is buggy in any case. In practice this is generally left to informal argument, or even left entirely implicit. However, for the concurrency model aspects of an architecture, what one can do is prove that a particular compilation scheme from a higher-level language (with its own concurrency model, and therefore its own strong-enough concern) is correct, and tensioning the two against each other like this has been very important in the design of both. We return to this later. In principle one could experimentally assess whether an archicture is strong enough by testing a substantial body of software above an architecturally aggressive emulator, that pseudorandomly chooses executions that exercise the extremes of what the architecture allows. For example, for x86 one could have an emulator that has very large write buffers, and flushes them roughly synchronised with data races in the code. Our understanding is that this has been done to some extent within several vendors, but we are not aware of such work for more relaxed architectures.

**Precise and unambiguous** For an architecture to serve its dual purposes, as a correctness criterion for hardware and a programming model for software, it should be *precise*: for any hypothetical programmer-observable behaviour, of any initial machine state, it should unambiguously define whether that behaviour is allowed or forbidden. Of course, in some cases this might depend on a specific architecture version, on some documented implementation-defined choice, or on some aspect of the architected (programmer-visible) machine state.

Ambiguity and imprecision should not be confused with looseness. On the contrary, the fact that architectures have to be loose specifications creates even more need for precision: for a subtle loose specification, it is essential that it precisely defines what is allowed and what is not, rather than leaving that vague.

The prose and pseudocode of most traditional architecture descriptions are generally reasonably precise about sequential behaviour but much less clear when it comes to concurrent behaviour and relaxed-memory phenomena — it is very hard to produce prose that unambiguously and completely captures these subtleties. Instead, we will develop models in *precise mathematics*.

**Clear** Architecture specifications have to be *clear*. They serve as a principal means of communication between the hardware and software development communities, and as such have to be comprehensible to both parties. This creates an incentive for an architecture specification to be as simple as possible – which is sometimes in tension with the desire to admit particular hardware optimisations.

One might think that the need for model definitions to be mathematically precise is in conflict with the need for them to be comprehensible to a wide audience, but in practice one can reconcile the two, by transcribing the mathematical definitions into prose (manually or automatically), and by providing tools that compute the allowed behaviour of test cases and let users explore them.

Another interesting tension relating to clarity is between models that are as concise as possible, just defining what whole-program behaviour is allowed or not, and models that are *explanatory*, that somehow explain how the allowed behaviour emerges from hardware optimisations. Several quite different styles of model definition are used – operational, axiomatic, and promising – which we return to in Chapter 5 and later. Typically (though there can be exceptions), operational models aim to explain the allowed behaviour in microarchitectural terms, while axiomatic models aim to define the allowed executions more abstractly in terms of the allowed orderings.

**Executable as a test oracle** Another major shortcoming of prose specifications is that they cannot be used directly for testing hardware or software against. Instead, one has to rely on test suites with manually curated outcomes, and on simulators written based informally on the prose. In practice, major vendors typically have one or more "golden models": executable simulators, written in-house and sometimes confidential, that they use to test against. However, as we understand it, these have often focussed just on sequential behaviour.

We will instead develop concurrency models that are *executable as test oracles*, i.e., that, given some (small) test and a potential observable result, can compute whether or not that

result is allowed by the model. In some cases they will have the stronger property that they are *exhaustively executable as a test oracle*: given some small test, they can compute the set of all the model-allowed results, as we did by hand for the sequential consistency model and the simple test above.

Given a model that is executable as a test oracle, an experimental setup (such as litmus7) for running tests on actual hardware, and a set of tests, one can automatically compare a model with the experimentally observable behaviour exhibited by specific hardware implementations, without having to manually curate the intended outcome for each test.

This is essential to support *experimental semantics* [54, 53]: the development of models informed and validated in part by such comparisons with experimentally observed behaviour, and to support experimental validation of hardware designs against such models. However, it is important to note that good architecture models cannot be developed solely by fitting to some experimental data, as they have to be loose specifications that also satisfy all the other properties in this list.

Having a model that is executable as a test oracle means that one can *generate* tests, either randomly or in some directed way, without having to manually curate the intended outcome of each; we return to this later.

Executable-as-test-oracle models can also be used directly to exhaustively model-check small concurrent algorithms.

**Incrementally executable** A different way in which an architecture model might be executable is *incrementally*, computing just single possible executions, e.g. by making pseudorandom choices at points where the specification is loose. This makes the model directly usable as an emulator, which may be useful for testing larger bodies of software for which it becomes infeasible to compute the set of all model-allowed outcomes. Note that such an emulator would be *architecturally complete*, in the sense that it can, pseudorandomly, generate any behaviour allowed by the architecture – in contrast to any specific implementation, and to conventional emulators such as QEMU.

**Mathematically validated** One typically cannot prove, mathematically, that an architecture specification is "correct", because there is no more authoritative statement of what "correct" would mean. However, proving results about a specification can be invaluable, both by establishing specific desired results, and boosting confidence in the detailed definition by exercising it in quite different ways to testing. Many different kinds of result can be useful, including:

- Equivalences between models in different styles, such as operational and axiomatic, for the same architecture.

- Refinements between models, showing that for programs that are in some sense wellbehaved, a simpler model accurately captures all the observable behaviour of a more fundamental model.

- Correctness of compilation schemes or compilers, from a high-level language model or semantics down to an architecture-level model.

- Soundness of program logics, model-checking algorithms, and other techniques for reasoning about programs.

**Authoritative** Ideally, a mainstream architecture specification would also be *authoritative*, defined by the relevant vendor or industry group. Socially, for each of these major architectures, there is an individual or small group that (perhaps following consultation with architecture partners and software users) has the authority to decide whether some observed behaviour is a bug or not – this is the ultimate role of an architect, to decide the architectural intent.

However, in some cases the vendor or other industry group produces prose specifications that do not have the above properties, or simply has not yet considered all the issues, and there one might end up with a model by a third party that aims to capture – and perhaps becomes – the de facto standard.

Accurately capturing the architectural intent Where there is an architect or group with the social authority to decide the architectural intent, one would like to confirm that any formal specification accurately captures that intent, allowing no more and no fewer behaviours than they intend to be allowed.

That can be challenging, especially when moving for the first time from an architecture specified only in prose to a formal model in an initially-unfamiliar form, that may be quite intricate. One can gain significant assurance through walking through the model in detail, and also by checking it gives the intended allowed behaviour for a set of litmus tests that is small enough for this to be tractable but which still covers a wide range of behaviour.

However, the consequences of a formal model may not all be obvious, and some of them may simply never have previously been considered, by the architects or anyone else. Some of the relaxed phenomena that we discuss later were of this kind: they emerged only from the process of developing and evaluating a model, and that informed later decisions about the architectural intent.

In practice, all architecture specifications are subject to change, at least in detail, in the face of implementation and usage reality – nothing is set in stone forever. However, on the positive side, when one has an established model, test suite, and intended results for those tests, any change to the model can be evaluated with respect to all those, which is much more tractable than establishing an initial formal model.

**Consistency with the de facto standard** One also has to consider consistency with the de facto standard. For any architecture with significant hardware implementations and software usage, the behaviour of those implementations, and the assumptions on hardware implementation behaviour implicit in the corpus of software, can tightly constrain possible architectural choices.

### 1.7 Programming language compiler effects

At the language level, observable relaxed-memory behaviour arises from the *combination* of any hardware relaxed-memory effects, for the memory accesses in the generated machine code, and a diverse collection of compiler optimisations. Just as for hardware implementations, these have been developed over many decades to optimise performance while preserving sequential behaviour, but they have substantial observable consequences for concurrent behaviour. Compiler optimisations routinely reorder, eliminate, introduce, split, and combine "normal" accesses, and remove or convert dependencies, in ways that vary between compilers, optimisation levels, and versions.

For example, in SC, the message passing example below – another very important litmus-test shape – should work as expected. This shape is a simple version of a common idiom for passing data between threads, in which Thread 0 writes some data to x (perhaps a large data structure), before writing a flag value to y to signal to other threads that the data is ready, and Thread 1 busy-waits reading y until it sees the new flag value, and then reads the data from x. In SC, if the Thread 1 read of y sees the write of y=1 then the program-order-later Thread 1 read of x will see the write of x=1; the program will either print nothing or 1.

Figure 1.1: Compiler reordering

| Thread 0 | Thread 1           |

|----------|--------------------|

| x = 1    |                    |

| y = 1    | <b>if</b> (y == 1) |

|          | printf("%d", x)    |

However, if there's some other read of x in the context, then common subexpression elimination could replace the second read by a reuse of the value from the first (which could easily be kept in a register), effectively reordering the Thread 1 reads of y and x to (the result of naively compiling):

| Thread 0 | Thread 1           |

|----------|--------------------|

| x = 1    | <b>int</b> r1 = x  |

| y = 1    | <b>if</b> (y == 1) |

|          | printf("%d", r1)   |

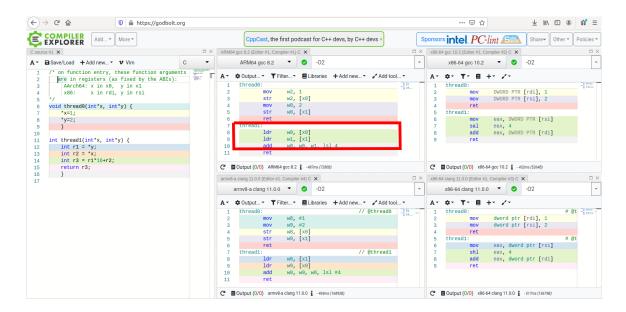

Compiler-introduced relaxed memory effects will typically be specific to some compiler version, optimisation level, and the details of the code. For example, in Fig. 1.1 ARM64 gcc 8.2 reorders the threadl loads, but the other compilations shown do not. One can see this in Compiler Explorer (short link) (full link).

This makes it harder to experimentally test what high-level language relaxed-memory behaviour is in practice, and, as we shall see, the interplay between hardware and compilation effects makes it harder to define reasonable concurrency models for high-level languages.

A general-purpose high-level language should provide a common abstraction over the common hardware architectures, that is efficiently implementable with respect to both:

- the cost of providing whatever synchronisation the language-level concurrency model mandates above those various hardware concurrency models; and

- the impact of providing the language-level model on existing compiler optimisations.

### **1.8 Programming language specifications**

Programming language specifications play a similar role to architecture specifications, serving as a criterion for correctness of language implementations, and as a specification of what pro-

grammers in the language should be able to depend on.

Historically, also like architecture specifications, they have been expressed just in prose, despite many decades of research on more precise and less ambiguous mathematical semantics of programming languages, and the specification of concurrency behaviour has been particularly lacking. For example, a specification of concurrency was added to the ISO C and C++ language specifications only in 2011, following an effort led by Boehm [60, 45, 51].

They often differ from most architecture specifications in having a looser relationship between the organisation maintaining the specification and those implementing it.

Of particular interest here are the C++ and C standards, maintained by ISO/IEC JTC 1/SC 22/WG 21 and WG 14 respectively, e.g. with recent versions:

- ISO/IEC 14882:2017 Information technology Programming languages C++ [92]

- ISO/IEC 9899:2018 Information technology Programming languages C [93]

We will also touch briefly on Java, JavaScript, and WebAssembly.

### 1.9 Status of the models

We discuss the validation of the concurrency models we cover, with varying combinations of experimental testing, discussion with architects, and proof, as we go. To briefly summarise the origin and status of the models:

**x86** For x86, the x86-TSO model we describe is widely accepted as the de facto standard. It was developed by Owens, Sarkar, Sewell, Zappa Nardelli, and Myreen, originally published in [116, 137]. This followed our earlier attempts [129] to interpret the then-confusing Intel and AMD documentation (the current vendor documentation [68, 17] is improved but still hard to interpret). It was informed by brief communications with Intel, AMD, and VIA architects. The operational and axiomatic models have been proved equivalent, first by Owens in HOL4 [116], and later, for a more modern presentation of the axiomatic model, by Durbaba in Isabelle [74].

**IBM Power** The IBM Power model we describe is also a good de facto standard to the best of our knowledge, capturing the architectural intent. It was developed based on detailed discussions with one of the senior IBM designers, Derek Williams, and extensive experimental testing on Power G5, 5, 6, 7, and 8. The vendor documentation [79] has not been updated to reflect the model design, however. The examples, discussion, and operational model that we present are some of the results of an extended line of work, mainly by Alglave, Flur, Maranget, Pulte, Sarkar, Sewell, and others, variously in collaboration or separately, that developed a series of axiomatic and operational models for IBM Power [22, 23, 131, 36, 25, 130, 103, 107, 38, 87, 78]. Much of the discussion text for this, Arm-A, and RISC-V is taken from the forthcoming PhD thesis by Flur.

**Arm-A** For Arm-A, we present operational and axiomatic models. The axiomatic model [70] was developed principally by Deacon, then at Arm, and was incorporated into the Arm documentation of the time [13]; the operational model was developed principally by Flur, Pulte, Sarkar, and Sewell. Both build on the above-cited work and [77, 78], and on extensive discussion between them and with Grisenthwaite (the Arm Chief architect). They incorporate a substantial simplification to the previous ARMv8-A architectural intent, switching to a "multicopy atomic" model (as we describe later). The two models were proved equivalent by Pulte [121, 120]. Further academic work by Armstrong et al. integrated the axiomatic model with the full Arm-A instruction semantics [41, 42, 43], and work by Simner et al. developed extensions

for some systems aspects: instruction fetch [142], virtual memory [141], and exceptions [140], again in collaboration with Grisenthwaite. Further work within Arm by Alglave (now at Arm) and colleagues has refined the Arm documentation model in various respects [28].

**RISC-V** For RISC-V concurrency, the RISC-V Foundation (since reconstituted as RISC-V International) established its RISC-V memory model working group in 2017-03, chaired by Daniel Lustig [14]. Flur, Maranget, Pulte, Sarkar, and Sewell contributed substantially from 2017-07, together with several others, to what became the RISC-V weak memory ordering model (RVWMO), which was ratified in 2018-07. This is very similar (though not identical) to the multi-copy atomic Arm-A model. The RISC-V formal axiomatic and operational models were incorporated into the RISC-V unprivileged specification [81].

C/C++ For C/C++, the early language standards did not attempt to specify concurrent behaviour. There was an extended effort to define a model, from around 2004 onwards, led by Boehm and recorded in the cpp-threads mailing list [6] and the ISO C++ concurrency subgroup (which later became the ISO C++ Concurrency Study Group, WG21/SG1) and its working papers [1]. Boehm and Adve outlined the model under construction in 2008 [60]. From 2009 Batty, Owens, Pichon-Pharabod, Sarkar, Sewell, and Weber worked to formalise the design and build tools; this uncovered and led to fixes for a number of flaws in the model [45, 56, 49]. The ISO C++11 standard [51] incorporated text in tight correspondence to the mathematical model of Batty et al., and this was ported to the ISO C11 standard. More recent work by many authors has continued to improve the model, although the "thin-air problem", which we return to later, continues to be a major open problem for this and other high-level language models. A separate line of work by Alglave, Maranget, McKenney, Parri, and Stern defined a model for the concurrency primitives used in the Linux kernel [34, 35] (though this too has related open problems).

### Part I

# SC, x86, tools, and approach

### Chapter 2

### x86 basic phenomena

Throughout this part we focus on a simple "user" fragment of x86, including loads, stores, read-modify-write operations, and barriers, but excluding misaligned and mixed-size accesses, string operations, and all "systems" aspects. We consider just coherent write-back memory, with no exceptions, "non-temporal" operations, self-modifying code, page-table changes, or device memory.

To help build a solid intuition, and to introduce some basic concepts and litmus tests that we'll elaborate on for other architectures and for programming languages, we'll approach the x86 behaviour incrementally: we'll discover the underlying model bit-by-bit with a few key examples.

### 2.1 Litmus tests and candidate executions

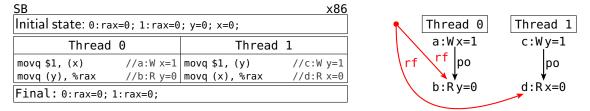

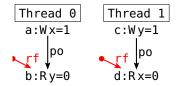

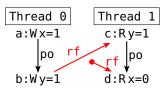

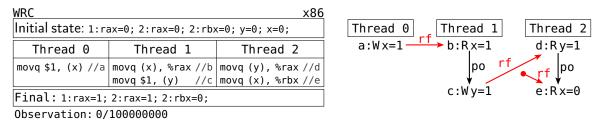

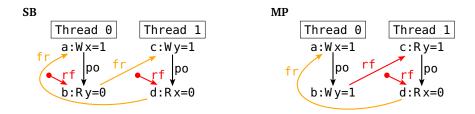

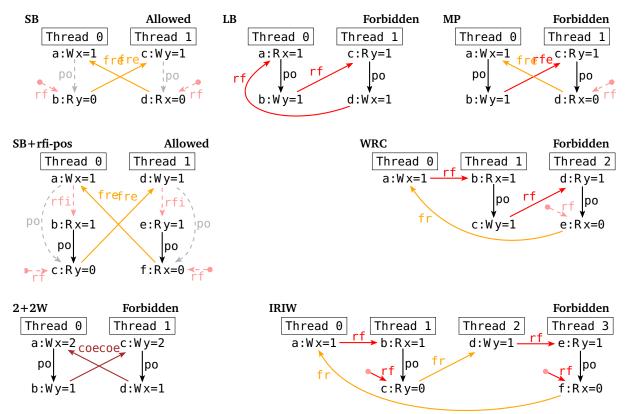

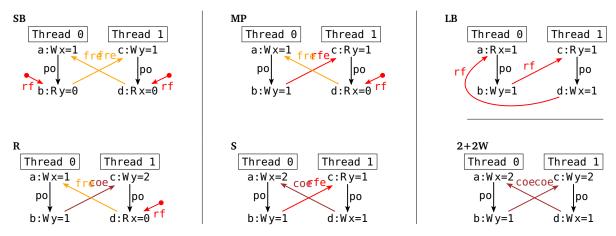

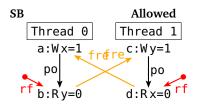

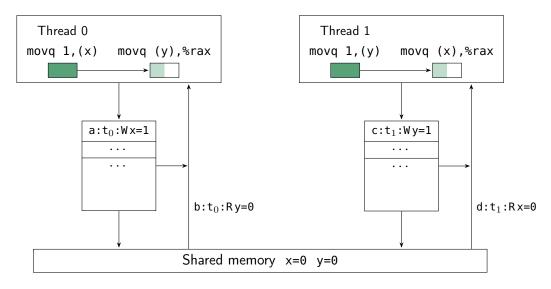

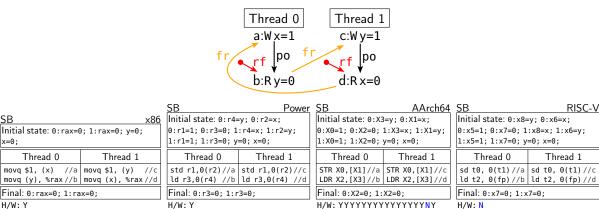

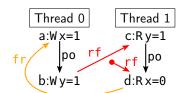

We've already seen one non-SC x86 behaviour, of the SB test on the left below, typeset from the SB.litmus file.

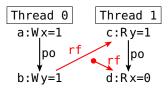

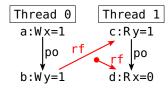

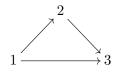

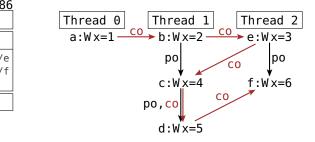

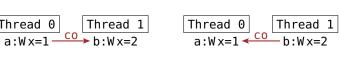

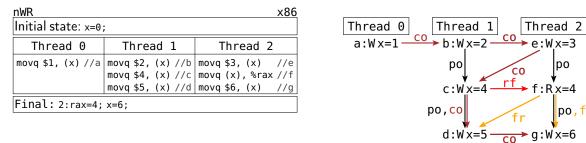

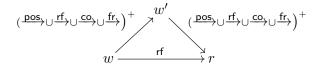

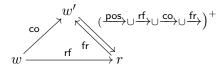

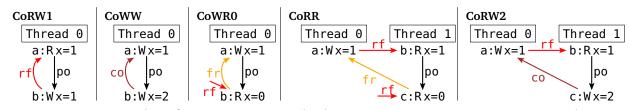

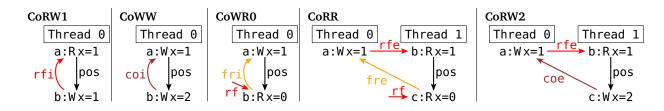

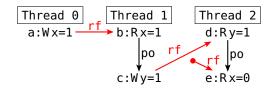

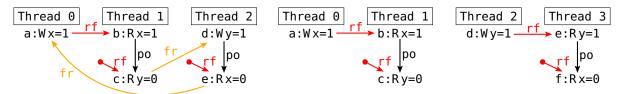

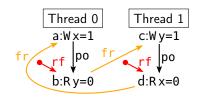

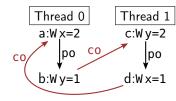

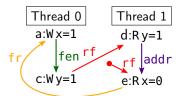

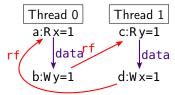

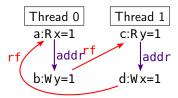

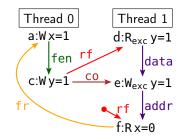

On the right above we draw the *candidate execution* of this that we are interested in. Each candidate execution is a graph with nodes that are memory access events and with edges indicating various relationships between them. Each memory access, e.g.  $a:t_0:Wx=1$ , has a unique identifier (a, b, etc.) and a thread ID ( $t_0$ ,  $t_1$ , etc.), and is either a write W or read R of a memory location (x, y, etc.) with a specific value (here 0 or 1). Usually the thread IDs are clear from the context and we elide them.

The edges are *program order* (po, in black) and *reads-from* (rf, in red), together with other relations that we introduce later. Program order relates each event to its successors (if any) in some control-flow unfolding of the program. Here, there are no conditional branches, so there is only one possible control-flow unfolding, and program order just follows the program source text. Program order is transitive, but we normally draw only its transitive reduction – just the edges between adjacent events. Note that these graphs are quite different to the SC labelled transition system we saw in Section 1.4: that was a diagram of all possible SC interleaving executions, with nodes representing global states and arrows the transitions between them; while this shows the events of one particular (not necessarily SC) execution, as the nodes, with arrows indicating various relations between those.

The reads-from relation relates each write event to all the read events that read from it in the execution. In this execution, both reads read from the initial state, indicated with arrows from a red dot. To de-clutter the diagrams, we usually draw such a dot for each read from the initial state, as below, but they all represent the single shared initial state.

Each litmus test has a condition on the final state, e.g. the Final: 0:rax=0; 1:rax=0; condition of this test. The final condition usually uniquely determines a single non-SC candidate execution of interest (under minimal assumptions on the model): for this test, the interesting execution is the only one in which both reads read 0 from the initial state (and the internal semantics of each instruction is respected). This execution is the one shown in the diagram. Note that the final condition only identifies some final state(s) of interest; it doesn't imply whether that state is observed or not experimentally on specific hardware implementations, or whether it is allowed or not in any specific model.

Litmus tests can be interesting for many different reasons: some capture the pattern of some important concurrent programming idiom, some may not arise in normal programming but are useful to explore exactly what is observed or allowed in implementations or models, and some arise from automatically and/or systematically generated families. Litmus tests can also be useful for identifying errors in hardware implementations, though most of those we shall see are not tuned for that (e.g. by stressing particular hardware resources); they are mostly aimed at concisely capturing some semantic choice, of what behaviour is or is not allowed.

### 2.2 SB: store buffering?

We saw in §1.5 that the non-SC final state of SB, 0:rax=0; 1:rax=0, is experimentally observable on at least some x86 processor implementations, and in fact it's easily observable on all that we have tested, which include a number from both Intel and AMD.

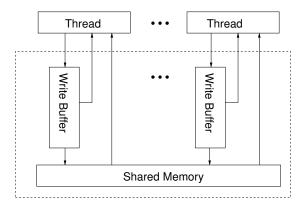

As we saw in §1.4, this is not an SC-allowed final state. To understand how it might arise, one can consider the microarchitectural hardware-implementation optimisations that would permit it. There are two obvious possibilities:

- 1. Hardware often *buffers* writes, decoupling the execution of program-order-later instructions from the propagation of the write down to memory. That propagation can take a long time, and it is often not necessary (for the correct execution of a program) for the program-order-later instructions to wait for it, so this can provide a big performance gain.

- 2. Hardware often executes instructions *out of order*, subject to checks on their dependencies. This allows, for example, later instructions to go ahead while earlier instructions are waiting for read values to come back from memory.

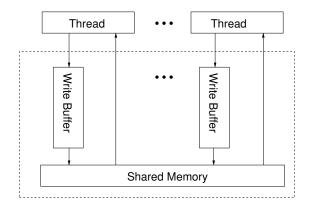

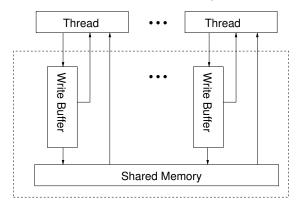

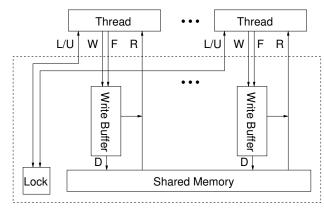

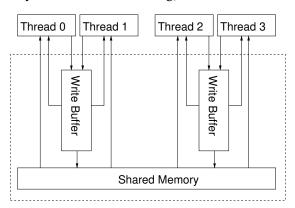

Either could explain the experimental data for this test. For 1, in a processor implementation with write buffers for each hardware thread, as in the cartoon microarchitecture below (which we will later see is not quite right), the writes to x and y might still be in the Thread 0 and Thread 1 store buffers, respectively, when the reads of y and x get satisfied from memory.

For 2, because the load instructions are to different locations to the program-order-preceding store instructions, and have no register dependencies on them, they might be executed first.

With what we know so far, we can't tell whether either one of these, or both, or something else, is the true explanation for the experimental observations.

To understand the architectural intent – to know whether the experimental observation is intended by the vendors to be allowed – we can turn to the vendor documentation. In this case that is clear. The Intel SDM [68, Vol.3A, §8.2.2] says

Reads may be reordered with older writes to different locations but not with older writes to the same location

and their Example 8-3 is essentially identical to this litmus test, with the final state given as allowed, while the AMD APM [17, Vol.2, §7.2] says

Non-overlapping Loads may pass stores

again with an example essentially identical to this test.

One should be cautious about the "reordered with" phrasing of the Intel documentation: it suggests that relaxed-memory effects can be explained with a mental model in which instructions are each executed atomically but in a reordered instruction stream. That is sometimes true, but it is not true in general, and it's not the most useful way of viewing the observable x86 behaviour.

To fix terminology: we usually speak of load and store instructions, giving rise to read and write memory events, though the literature and test names are not always consistent with this (otherwise this test would be WB, not SB).

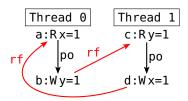

### 2.3 LB: load request buffering?

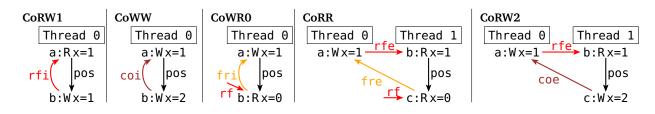

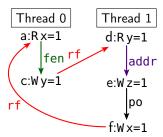

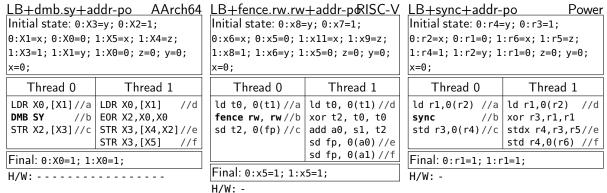

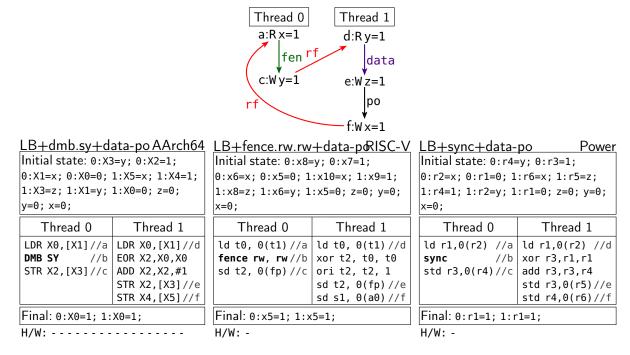

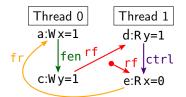

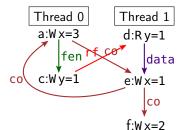

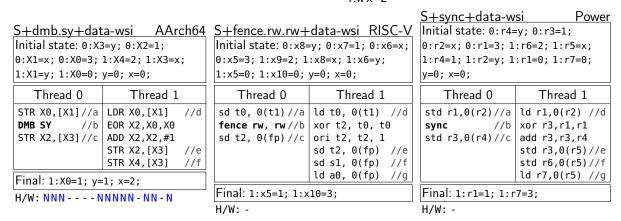

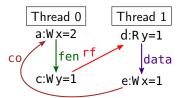

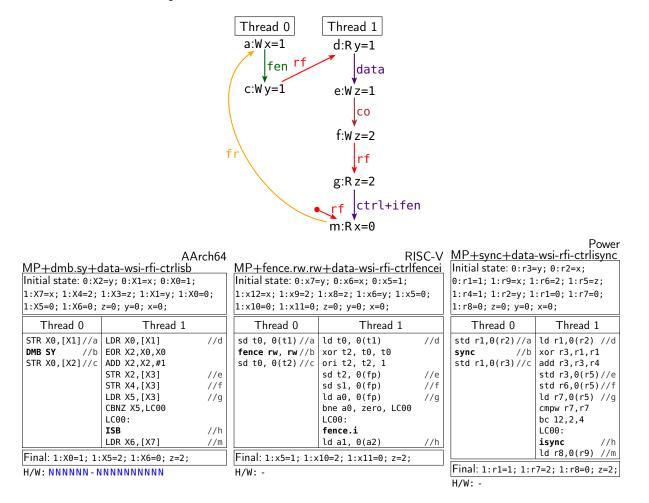

We turn now to the dual of SB: the "LB" litmus test below, in which Thread 0 reads x and then writes y while Thread 1 reads y and then writes x. The interesting execution is that in which both reads read from the other thread's write, rather than from the initial state, as shown on the right below.

| LB                     | x86                                |

|------------------------|------------------------------------|

| Initial state: 0: rax= | 0; 1:rax=0; y=0;                   |

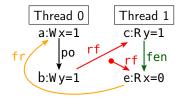

| х=0;                   |                                    |