Overview of the Rocket chip

An overview of Berkeley’s RISC-V “Rocket Chip” SoC Generator can be found here.

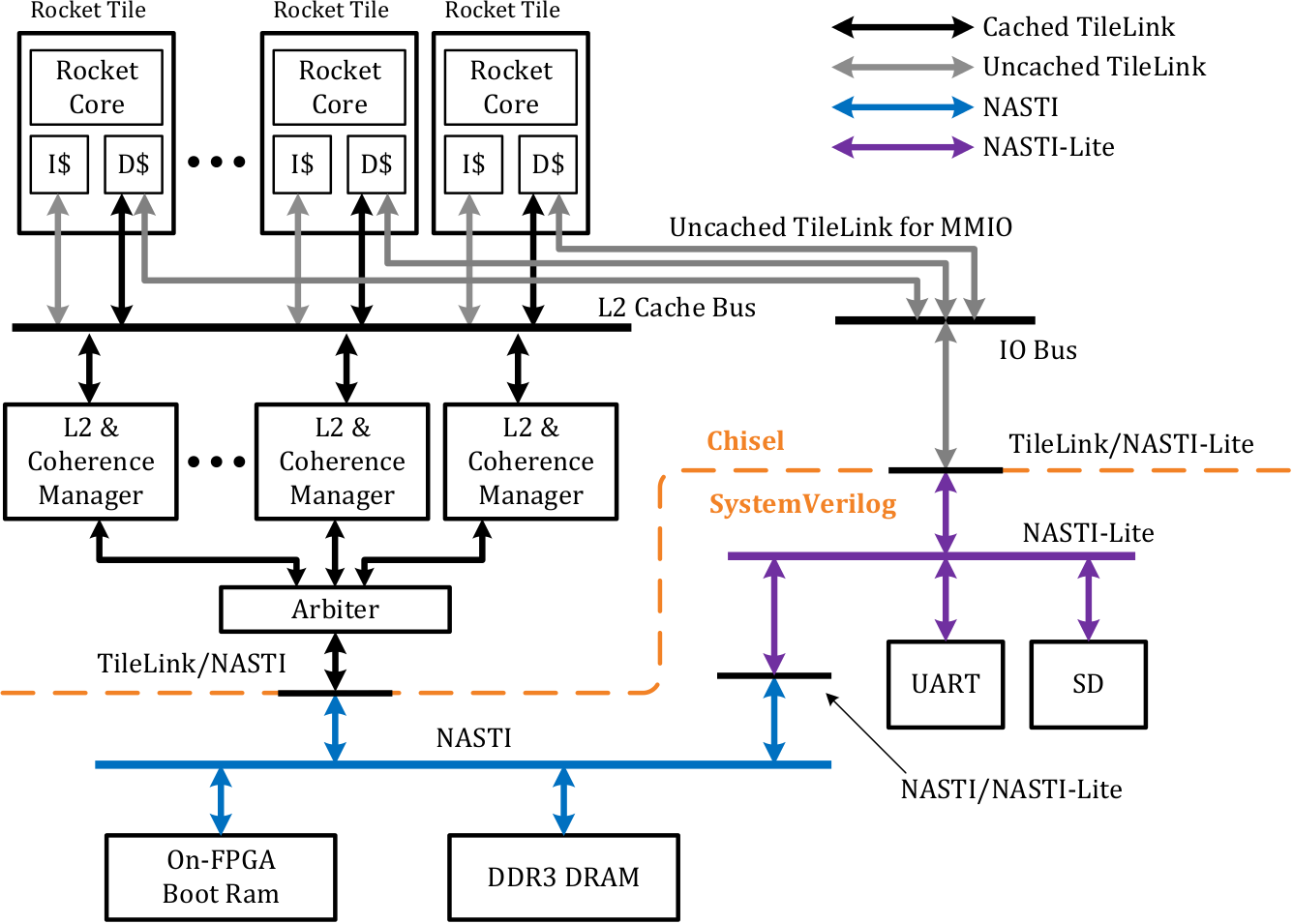

A high-level view of the untethered Rocket chip is shown below. The design

contains multiple Rocket tiles each of which consists of a Rocket core and L1

instruction and data caches. All tiles share a unified and banked L2 cache and an I/O bus.

The Rocket (Chisel) side of the SoC is encapsulated in a Chisel island whose features are configurable using the top-level configuration file $TOP/src/main/scala/Configs.scala (see Configuration parameters for more details).

Two NASTI/NASTI-Lite interfaces are exposed to the FPGA peripherals. They implement a limited subset of the AXI/AXI-Lite bus functions. The NASTI interface is used by the L2 cache for memory reads and writes, while the NASTI-Lite interface is used by the I/O bus for peripheral accesses.

The NASTI on-chip interconnects are implemented in parameterized SystemVerilog located in $TOP/socip/nasti.

- On-FPGA Boot RAM

(0x00000000 - 0x0000FFFF)

On-FPGA Block RAM, 64 KB [AXI Block RAM (BRAM) Controller v4.0]. - DDR DRAM

(0x40000000 - 0x7FFFFFFF)

Off-FPGA DRAM, KC705 DDR3 1 GB, NEXYS4-DDR DDR2 128 MB [Zynq-7000 AP SoC and 7 Series Devices Memory Interface Solutions v2.4]. - UART

(0x80000000 - 0x8000FFFF)

Xilinx AXI UART 16550 [AXI UART 16550 v2.0]. - SD

(0x80010000 - 0x8001FFFF)

Xilinx AXI Quad SPI [AXI Quad SPI v3.2].

Fat 32 support [FatFs - Generic FAT File System Module].