An RTL description is at the so-called Register Transfer Level

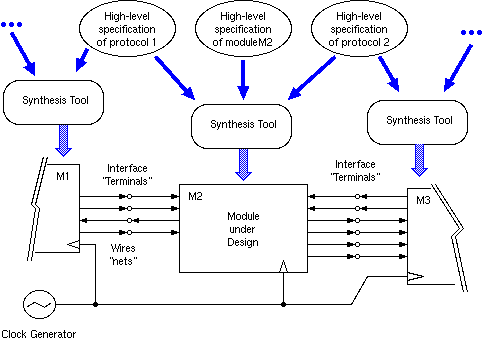

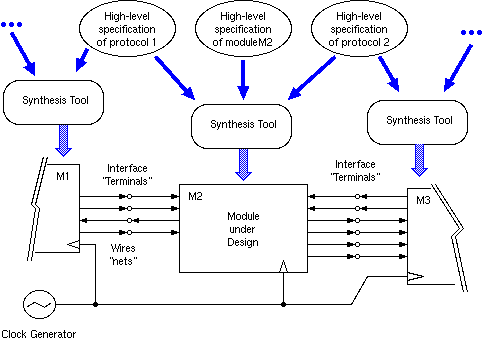

A hardware design consists of a number of modules interconnected by wires known as `nets' (short for networks).

The interconnections between modules are typically structured as mating interfaces. An interface nominally consists of a number of terminals but these ultimately may have no physical manifestation owing to inter-module logic optimisation.

In a modern design flow, the protocol at an interface is ideally specified once in a master file that is imported for the synthesis of each module that sports it.

But a lot of low-level manual entry of RTL design is still (2017) used.

A clock domain is a set of modules and a clock generator. Within a synchronous clock domain all flip-flops have their clocks commoned.

| 1: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. | |